MÁRCIO HENRIQUE FERREIRA

MÁRCIO ROBERTO DA SILVA

RODRIGO BARROCA DIAS FERRAZ

## **SISTEMA DEDICADO DE MEDIÇÃO DE FREQUÊNCIA**

Projeto de Formatura apresentado à disciplina

PCS 2502 – Laboratório de Projeto de Formatura II,

da Escola Politécnica da Universidade de São Paulo.

Orientadores: Prof. Edson Midorikawa

Prof. Ricardo Paulino Marques

V.1

São Paulo

2005

## Agradecimentos

Gostaríamos de citar e agradecer o apoio de várias pessoas, que direta ou indiretamente contribuíram para o projeto. Algumas pessoas merecem uma menção especial.

O professor Edson Midorikawa, do PCS-USP, guiou o planejamento da solução baseada na FPGA, e permitiu que pudéssemos andar com nossas próprias pernas no projeto.

O professor Wang, do PSI-USP, contribuiu com muitas idéias relacionadas à otimização e implementação de partes do sistema, e informações valiosas sobre implementação e manufatura dos sistemas, placas, etc.

Gostaríamos de agradecer também o LSI-USP por ter cedido o kit de desenvolvimento com o qual foi realizado todo o projeto de formatura. A falta deste equipamento provavelmente inviabilizaria os trabalhos realizados.

Ao senhor Mário, da Unisal, pela ajuda no projeto dos circuitos eletrônicos auxiliares.

À BL Representações por fornecer amplos recursos de teste para a realização do projeto.

MÁRCIO HENRIQUE FERREIRA

MÁRCIO ROBERTO DA SILVA

RODRIGO BARROCA DIAS FERRAZ

Sistema Dedicado de Medição de Frequências

Projeto de Formatura apresentado à disciplina

PCS 2502 – Laboratório de Projeto de Formatura II,

da Escola Politécnica da Universidade de São Paulo.

Aprovado em:

Banca Examinadora

Professor: \_\_\_\_\_

Instituição: \_\_\_\_\_ Assinatura: \_\_\_\_\_

Professor: \_\_\_\_\_

Instituição: \_\_\_\_\_ Assinatura: \_\_\_\_\_

Professor: \_\_\_\_\_

Instituição: \_\_\_\_\_ Assinatura: \_\_\_\_\_

## Resumo

O projeto de formatura aqui desenvolvido consiste em projetar e construir o protótipo de um sistema dedicado de medição de freqüência, utilizando hardware dedicado baseado em FPGA, que realize a seguinte operação: receber dados de um medidor de gravidade (gravímetro) e de uma base de tempo estável (GPS ou cristal de precisão, ou uma simulação da mesma), processá-los e armazená-los da forma adequada em um computador.

O freqüencímetro servirá para realizar o processamento do sinal de um instrumento chamado gravímetro, que serve para levantar o valor da gravidade em um certo ponto. Este instrumento está sendo utilizado em um projeto feito para a Agência Nacional de Petróleo, de levantamento de dados geofísicos de uma certa área. O gravímetro é um instrumento de altíssima precisão e sensibilidade, que necessita de um sistema medidor de freqüência dedicado especial para ser compatível com esse tipo de medição. A medição de gravidade impõe várias restrições ao processamento do sinal.

O processamento do freqüencímetro deve responder com dados de alta precisão, com alta velocidade de funcionamento. Um circuito com estas características é alcançado através do projeto de um hardware dedicado. A maneira mais prática de fazer esse tipo de desenvolvimento é utilizando chips do tipo FPGA. A FPGA é um chip no qual se pode criar um circuito digital especial e utilizá-lo como se fosse um CI. Porém a FPGA é reconfigurável, e isto diminui o tempo de projeto, facilita a reconfiguração e mudanças de projeto, e propicia melhor desempenho em relação a um dispositivo baseado em microcontroladores.

## Sumário

|       |                                                            |    |

|-------|------------------------------------------------------------|----|

| 1     | Introdução .....                                           | 7  |

| 1.1   | Objetivo .....                                             | 7  |

| 1.2   | Motivação .....                                            | 7  |

| 1.3   | Organização .....                                          | 8  |

| 2     | Aspectos conceituais .....                                 | 9  |

| 2.1   | Tecnologias .....                                          | 9  |

| 2.1.1 | Projeto VHDL .....                                         | 9  |

| 2.1.2 | IDE e Simulador .....                                      | 10 |

| 2.1.3 | Design em FPGA .....                                       | 11 |

| 2.1.4 | Protocolo RS232 .....                                      | 12 |

| 2.2   | Conceitos utilizados .....                                 | 13 |

| 2.2.1 | Teoria de medição .....                                    | 13 |

| 2.2.2 | Organização de sistemas digitais .....                     | 18 |

| 3     | Especificação do Projeto .....                             | 22 |

| 3.1   | Especificação dos requisitos .....                         | 22 |

| 3.2   | Detalhamento do projeto .....                              | 23 |

| 3.3   | Características funcionais .....                           | 25 |

| 3.3.1 | Como funciona o freqüencímetro .....                       | 26 |

| 3.3.2 | Como funcionam os módulos .....                            | 27 |

| 4     | Metodologia .....                                          | 40 |

| 4.1   | Implementação .....                                        | 40 |

| 4.2   | Metodologia de Teste .....                                 | 41 |

| 4.3   | Organização .....                                          | 42 |

| 4.3.1 | Ferramentas de apoio .....                                 | 42 |

| 5     | Projeto e Implementação .....                              | 46 |

| 5.1   | Pesquisa e concepção .....                                 | 46 |

| 5.1.1 | Familiarização com o ISE 7.1 / ModelSim MXE .....          | 47 |

| 5.2   | Familiarização com a placa Digilent D2SB/DIO4 .....        | 50 |

| 5.2.1 | Estudo dos algoritmos de divisão e modelos .....           | 53 |

| 5.2.2 | Estudo de alternativas para otimização de desempenho ..... | 54 |

| 5.2.3 | Melhorias no processo de medição .....                     | 55 |

| 5.2.4 | Implementação single clock X multi clock .....             | 57 |

| 5.2.5 | Trade-off de desempenho .....                              | 59 |

| 5.2.6 | Montagem da placa .....                                    | 60 |

| 5.3   | Desenvolvimento .....                                      | 61 |

| 5.3.1 | Digitalizador .....                                        | 62 |

| 5.3.2 | Programação da FPGA .....                                  | 63 |

| 5.3.3 | Conversores de tensão .....                                | 68 |

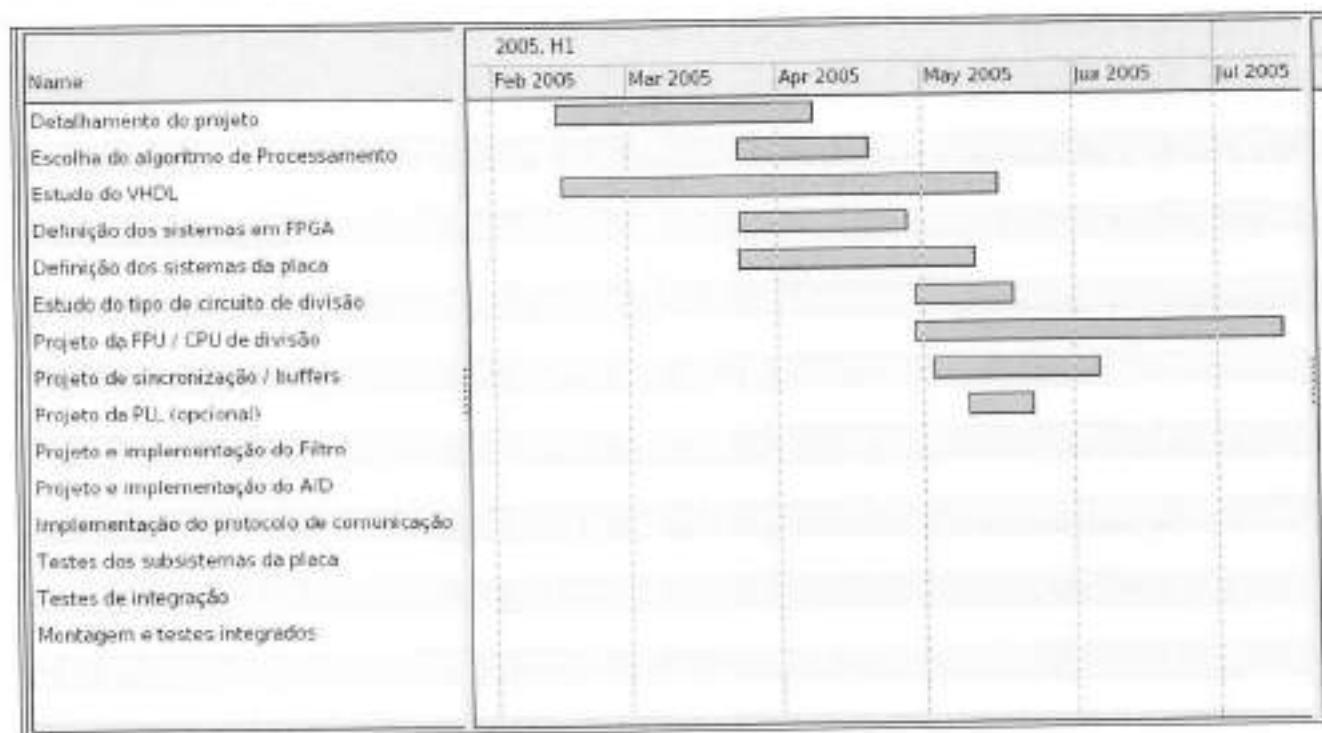

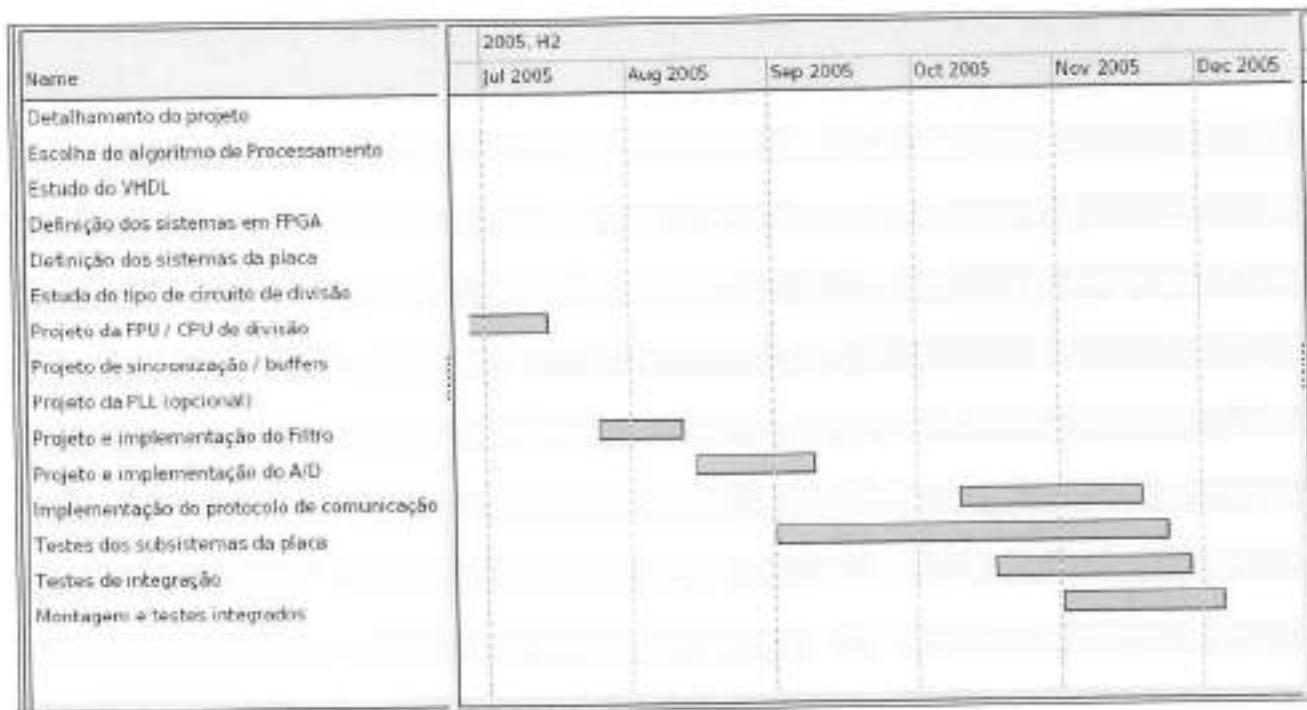

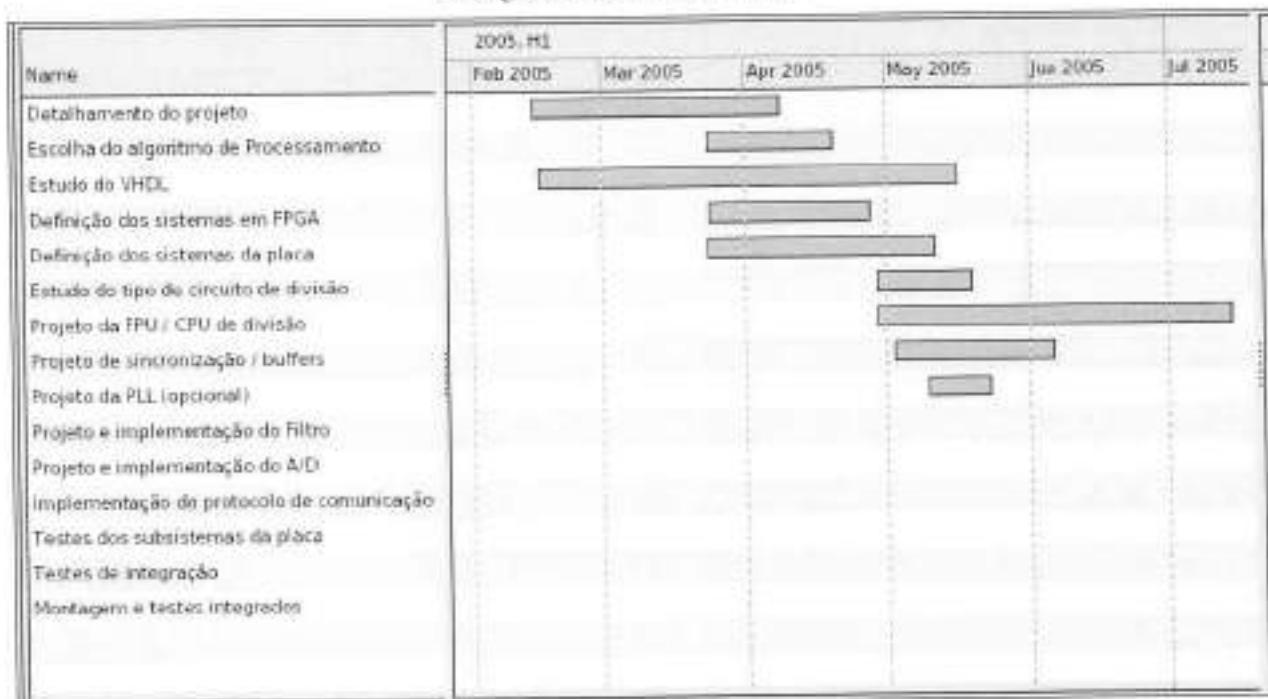

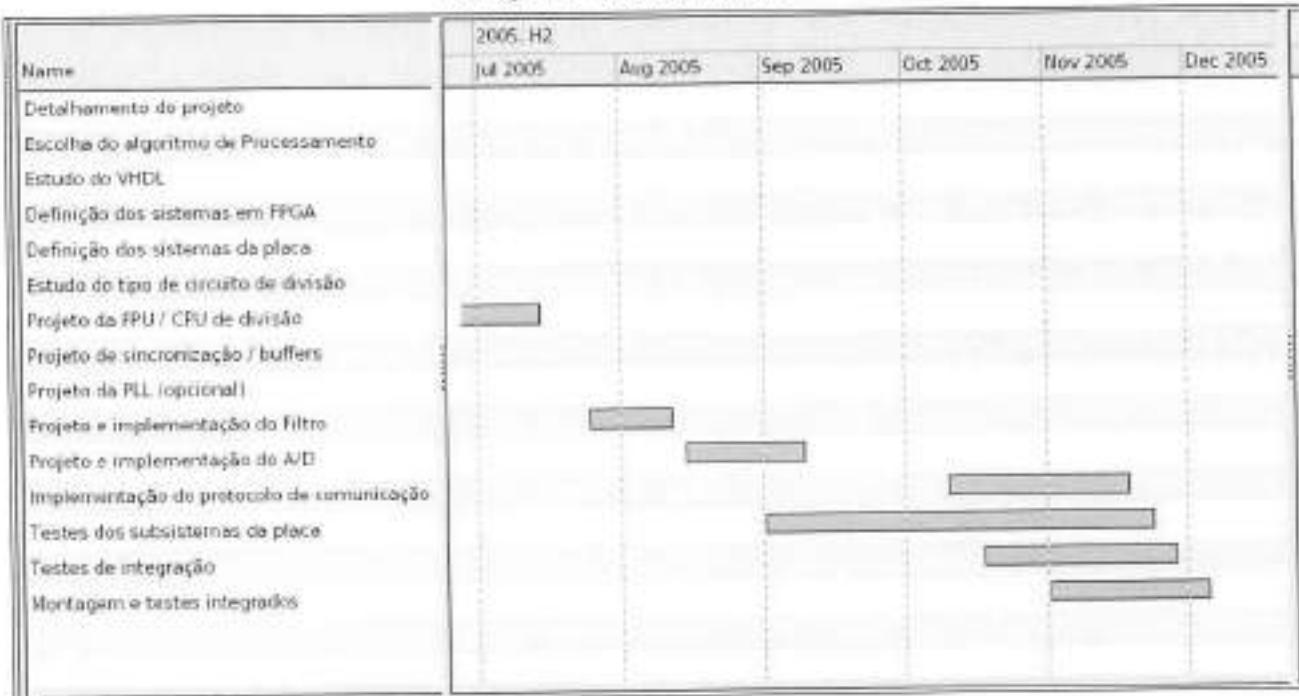

| 5.4   | Cronograma .....                                           | 71 |

| 5.4.1 | Cronograma inicial .....                                   | 71 |

| 5.4.2 | Modificações .....                                         | 73 |

| 5.5   | Problemas encontrados .....                                | 76 |

| 6     | Balanço da implementação .....                             | 81 |

| 7     | Testes e depuração .....                                   | 82 |

| 7.1   | Resultados obtidos .....                                   | 83 |

|     |                                                           |     |

|-----|-----------------------------------------------------------|-----|

| 7.2 | Análise do desempenho do circuito.....                    | 85  |

| 8   | Conclusão / Considerações finais.....                     | 88  |

| 8.1 | Balanço do projeto.....                                   | 88  |

| 8.2 | Perspectiva de Continuidade .....                         | 89  |

|     | Anexo I: Processo de teste e geração de código.....       | 91  |

|     | Referências .....                                         | 99  |

|     | Livros .....                                              | 99  |

|     | Papers .....                                              | 99  |

|     | Sites URLs .....                                          | 100 |

|     | Apêndice I – Apresentação do CD do projeto dirigido ..... | 101 |

# 1 Introdução

## 1.1 *Objetivo*

Desenvolver um sistema dedicado medidor de freqüência que possa receber dados de um gravímetro (medidor de gravidade) e de uma base de tempo estável (GPS ou cristal de precisão), processá-los e armazená-los da forma adequada em um computador.

## 1.2 *Motivação*

O tema se relaciona à área de sistemas dedicados, processamento de sinais e instrumentação. O sistema proposto é parte do gravímetro do projeto da Agência Nacional De Petróleo (ANP), executado pelo Laboratório de Automação e Controle (LAC), de levantamento de dados geofísicos (entre outros tipos relevantes e dados) de algumas regiões do Brasil.

O gravímetro é um instrumento de alta precisão e que necessita de um sistema medidor de freqüência dedicado especial, com diversas características específicas. Para atender a estas necessidades foi iniciado o desenvolvimento deste projeto.

### **1.3     *Organização***

A equipe de desenvolvimento deste projeto é composta por três integrantes de diferentes ênfases de Engenharia Elétrica: Automação e Controle, Computação e Sistemas Eletrônicos. Por este motivo, os trabalhos foram orientados por um professor do Departamento de Automação e Controle da Escola Politécnica da USP (Prof. Ricardo Paulino Marques) e um professor da do Departamento de Computação e Sistemas Digitais (Prof. Edson Midorikawa). Isto foi possível devido a multidisciplinariedade evidente do projeto.

Por fazer parte de um projeto maior da ANP, desenvolvido pelo LAC, a concepção e o desenvolvimento foram acompanhados também pelo professor João Luiz de Paiva Martins que está ligado a equipe de desenvolvimento deste projeto do LAC.

## 2 Aspectos conceituais

O objetivo deste tópico é permitir ao leitor conhecer e ter um ponto de referência para acompanhar o desenvolvimento do projeto.

Nessa parte serão citadas as principais tecnologias aplicadas, algumas das ferramentas utilizadas no projeto, e criamos referências que podem ser consultadas sempre que algum ponto citado na implementação ou desenvolvimento não estiver suficientemente claro.

Apresentamos inicialmente as principais tecnologias referenciadas, e numa segunda parte serão cobertos conceitos freqüentemente utilizados e um pouco de teoria de circuitos digitais. Nem tudo que foi utilizado está descrito, mas os de maior influência podem ser facilmente reconhecidos.

### 2.1 *Tecnologias*

As tecnologias empregadas estão relacionadas à construção de circuitos digitais e transmissão de dados. Vamos explicar como é feito esse projeto e com que ferramentas.

#### 2.1.1 Projeto VHDL

Este projeto consiste em desenvolver um hardware dedicado para realizar o processamento digital de sinais.

As linguagens de descrição de hardware são utilizadas justamente para descrever o funcionamento de circuitos digitais. Mais recentemente, com o advento de chips programáveis, elas têm se tornado muito difundidas para descrever e sintetizar projetos para FPGA's e circuitos ASIC's, que são basicamente projetos de circuitos digitais customizáveis, em projetos dos mais variados tipos, tais como aplicações customizadas, baixa quantidade, protótipos e sistemas no chip (SoC, System on Chip).

Existem várias linguagens de descrição de hardware, tais como o VHDL (nossa escolha), Verilog, SystemC, AHDL, etc. Muitas delas são específicas das empresas que as desenvolvem.

A linguagem VHDL se tornou um padrão do IEEE para descrição de circuitos digitais. O que se faz numa descrição VHDL é criar o circuito digital baseado em unidades lógicas básicas, tais como flip-flop, registradores, etc. É possível encapsular circuitos de modo a se fazer o reaproveitamento de código em outras partes do circuito, ou até mesmo outros projetos.

### **2.1.2 IDE e Simulador**

Esta seção fala sobre o que sem dúvida é o objeto de trabalho principal durante o projeto. O termo IDE significa "Integrated Development Environment", ou seja, ambiente integrado de desenvolvimento. IDE's para o design de software são bem difundidos hoje em dia. Podemos citar como exemplos famosos o Visual Studio e o Eclipse.

Existem vários tipos de IDE's para diversos propósitos, e a sua função é prover ferramentas que facilitem a criação e gerenciamento de projetos de software ou outros tipos de design. No nosso caso, utilizamos o ISE 7.1i, que é um ambiente de desenvolvimento da Xilinx, que é a empresa que fabrica a FPGA de trabalho.

O processo de criar um sistema funcionando em uma FPGA não é trivial. Existem várias etapas para serem feitas e o uso do IDE realmente facilita o projeto. O ISE permite o acompanhamento do projeto desde as primeiras codificações até o envio do código de baixo nível para a placa ou EPROM/flash.

É possível durante o processo de desenvolvimento simular o código VHDL sintetizado. Isso é extremamente útil para depurar problemas na lógica de implementação e comportamentos imprevistos.

No simulador é possível acompanhar todos os sinais utilizados, internos ou externos, e seus valores a cada instante. Esse tipo de simulador é chamado simulador de waveform, pois podemos acompanhar as formas de onda dos sinais. Podemos simular diversas situações alterando as formas de onda de entrada, simular falhas, situações anormais, transitórios, etc. Os sinais podem ser agrupados de modo a fazer sentido. Por exemplo, podemos agrupar as saídas paralelas de um registrador para que possamos ver o número que eles representam, ao invés de uma cadeia de bits (por exemplo, 12 no lugar de 00001100).

### **2.1.3 Design em FPGA**

Vamos fazer uma breve introdução sobre como é feito o projeto de um circuito digital em FPGA, para que o leitor possa acompanhar como foi desenvolvido o projeto do nosso processador digital de sinais.

O termo FPGA significa Field Programmable Gate Array, ou seja, um conjunto de dispositivos de lógica programável. Ou seja, a FPGA é um chip no qual é possível programar (e reprogramar) o circuito lógico digital que está operando no interior da mesma.

A FPGA é muitas vezes utilizada para circuitos dedicados, projeto customizados e em soluções que envolvem rápida prototipação ou baixo volume.

É possível gerar vários tipos de circuito para funcionarem na FPGA, ela é muito flexível. Existem vários tipos de FPGA, sendo que as mais potentes podem suportar rodar uma CPU virtual com a potência de uma CPU PowerPC inteiramente funcional. Esses circuitos são muitas vezes referenciados como "soft-cores", em uma referência à palavra software, para lembrar que não é um processador real, mas sim um circuito de CPU rodando em cima da FPGA. Alguns sistemas de FPGA possuem integrados uma CPU para aumentar o desempenho (pois o circuito da FPGA é mais lento que os chips comuns), dada a possibilidade de reconfigurabilidade, é normal se esperar um circuito de menor desempenho.

Para se criar um circuito em FPGA são necessários várias etapas. Não vamos descrevê-las aqui, pois seria precipitado. Na parte de desenvolvimento é possível acompanhar o processo com riqueza de detalhes e telas do programa ISE, para facilitar o acompanhamento.

#### **2.1.4      Protocolo RS232**

O protocolo RS232 para transmissão serial de dados é muito difundido. Apesar de ser um protocolo um pouco antigo, sua importância e relevância não são diminuidos.

Vários protocolos presentes atualmente se baseiam na transmissão serial, por exemplo, é possível no protocolo Bluetooth emular uma porta serial de comunicação. É possível utilizar conversores entre protocolos Serial e USB, o que permite utilizar componentes com comunicação serial utilizando cabo USB, ou fazer crer a um programa em um computador que ele possui uma porta serial (serial virtual), quando a ligação na verdade é USB ou Firewire.

Essa flexibilidade e a facilidade em implementar a comunicação serial nos fez optar por esse caminho na construção do protótipo. Esta solução pode ser facilmente adaptada ou modificada para outros casos, ou ser encapsulada em uma solução mais moderna, por exemplo.

O protocolo é simples e a implementação da controladora serial UART (Universal asynchronous receiver transmitter) não exige muitos componentes ou desempenho. Tanto é que no nosso projeto estamos implementando a controladora de serial internamente à FPGA, em VHDL. A UART é responsável por tratar os dados recebidos pelo cabo serial e preparar dados para serem enviados, além de conter mecanismos de detecção de erro de transmissão simples.

## **2.2 *Conceitos utilizados***

Este segundo bloco é um resumo das principais áreas estudadas e aplicadas ao trabalho de formatura.

### **2.2.1 *Teoria de medição***

O processo de medição por contagem é o método de medição de freqüência dominante. Neste método busca-se gerar eventos que ocorrem com a mesma periodicidade que o fenômeno que se quer medir, e no caso da contagem digital, deseja-se que esse evento seja um sinal digital que seja passível de ser contado por um sistema digital em seguida.

Muito foi pesquisado pela equipe sobre instrumentação e medição de freqüência. Há relativa pouca informação a respeito desse campo, pois na maioria das aplicações uma contagem simples é suficiente, e com o advento de circuitos digitais cada vez mais potentes, os empecilhos

diminuiram bastante. Também não existem muitos fabricantes de medidores de freqüência de alta precisão e/ou calibradores de freqüência.

A medição de freqüência basicamente é feita de duas formas:

**1) Medição por contagem:** compara-se a repetição de um evento com outro conhecido ou de periodicidade conhecida

**2) Medição por ressonância:** método para alguns freqüencímetros (principalmente de microondas) que utilizam uma cavidade de ressonância para realizar a medida. Este segundo método, por ressonância, é pouco utilizado, pois funciona apenas para uma certa faixa de freqüências.

O processo de contagem é muito mais genérico, e baseia-se na simples comparação com uma referência conhecida. O uso de cristais fornecendo uma base de tempo estável e a crescente quantidade de circuitos digitais popularizou esse método. A geração de pulsos em eventos ou sinais digitalizados são fáceis de serem obtidos.

O método de contagem por comparação também tem alguns problemas intrínsecos. Em uma medição de um sinal senoidal, por exemplo, existem alguns problemas relacionados à detecção do ponto que o sinal é nulo, pois geralmente a medida é feita entre dois intervalos em que o sinal vale zero.

Pode-se reduzir esse problema digitalizando o sinal a ser medido (utilizando um comparador com AmpOp, para saturar o sinal em +Vdd e -Vdd, como no nosso caso), e obter uma onda quadrada com a mesma freqüência do sinal original. Uma vez obtida uma onda digital, é muito mais simples tratar da contagem, pois pode-se utilizar detectores de borda de subida ou descida.

Para um sinal periódico, o tratamento pode ser imediato. Pode-se introduzir algumas variações para o caso do sinal ter um duty cycle diferente de 50%, ou um buffer de entrada, se o

sinal for composto de pulsos irregularmente distribuídos no tempo (ou no caso de uma medição única, não contínua, chamada "single shot").

### **2.2.1.1 *Métodos de contagem***

Os métodos de medida da contagem são de 3 tipos:

#### **1) Inversão da medição do período**

Este método é utilizado para a medição de freqüências baixas e consiste em contar quantos ciclos de um sinal de clock conhecido (sinal de referência) ocorreram durante um ciclo executado pelo sinal desconhecido. Assim, obtém-se a duração do pulso como sendo  $n$  vezes o período do sinal de referência. Nota-se também que neste método há uma incerteza intrínseca de  $\pm 1$  período do clock de referência. Outra coisa a se notar é que este caso corresponde à situação deste projeto, em que há um sinal de KHz a ser medido, e uma referência na ordem de MHz.

#### **2) Número de pulsos ocorridos em um certo intervalo**

Para sinais mais rápidos é mais interessante contar quantos ciclos ocorrem para um certo intervalo conhecido, ou seja, um ou mais períodos da base de referência.

#### **3) Medição do tempo necessário para ocorrer um certo número de pulsos**

É uma variação do método 2, para o caso em que a freqüência do sinal digital é variada, ou seja, onde se tem pulsos muito próximos ou muito distantes um do outro, sendo que o sinal seria uma combinação de um sinal de baixa e um de alta freqüência. Neste caso, deve-se tentar

absorver estas variações realizando um número de medições igual aproximadamente ao valor de saída que se espera. Por exemplo, se está sendo medido um sinal de MHz, com pulsos não uniformes, o ideal seria realizar um milhão de medições em um segundo, o que englobaria as variações de maneira suficiente. O problema é que é necessário ter em mãos uma estimativa da freqüência previamente.

Logo, utilizando o fato que devido ao circuito ser digital o valor medido sempre tem um erro intrínseco de mais ou menos um período do clock mais elevado, pode-se calcular de maneira simples o erro envolvido em cada caso, o que pode ser encontrado no artigo da National Instruments sobre precisão de contagem, na referência deste documento.

### **2.2.1.2 Análise do erro**

Dados os três métodos básicos de medição simples, as fórmulas de erro de medição podem ser deduzidas. É importante dizer que como foi dito, são métodos simples e que servem de base para a realização de uma medida. Em uma aplicação real, utilizam-se esses métodos como artifícios que possibilitam aumentar a precisão do sistema.

Para fins de conhecimento, vamos enumerar os resultados abaixo. Sejam as variáveis de interesse:

Fk: freqüência conhecida, estável

Fx: freqüência a ser medida

n: resultado do contador

k: repetições de medida

Fm: freqüência medida

Erro método 1 ( $F_k \gg F_x$ ):  $F_m = F_k/n$  e  $\text{err}(F_m) = F_x/(F_k - F_x)$

Erro método 2 ( $F_k \gg F_x$ ):  $F_m = F_k * n$  e  $\text{err}(F_m) = F_k/F_x$

Erro método 3 (igual #1):  $\text{err}(F_m) = F_x/(k * F_k - F_x)$

Para um efeito ilustrativo, vamos imaginar alguns cenários de medição (que por conveniência são próximos do nosso cenário).

Segundo o método 1, para um clock de 80MHz (pensando em um oscilador OCXO de 20MHz, e um sistema para quadruplicar esta freqüência), e tendo como alvo um valor de aproximadamente 27 bits (o valor deve ser próximo de 27 bits) e entrada na ordem de KHz, tem-se uma variação na medida devida somente a esse erro já na primeira casa decimal (ou pior). Ou seja, para um clock de 80 MHz, e sinal na casa de 1K, a máxima precisão limitada pelo método de divisão é de uma casa depois da vírgula.

#### **2.2.1.3 Base estável de referência**

Conforme foi citado, a contagem geralmente necessita de uma base estável de referência de tempo. As bases de tempo de referência são geralmente de dois tipos:

**Cristal / Oscilador**

**Sinal de referência de GPS**

O GPS fornece uma referência muito estável de 1pps (1Hz), ou seja, um sinal de 1 segundo de duração. Este sinal geralmente é usado para calibrar o instrumento (que pode ser um calibrador de instrumentos também), e geralmente é utilizado em equipamentos muito sensíveis.

Os instrumentos possuem também uma referência interna de um oscilador de cristal. Geralmente é utilizado um sistema chamado OCXO (Oven Compensated Crystal Oscillator), que

é composto por um oscilador, e um sistema de aquecimento com controle, de modo a manter o cristal em uma certa temperatura estável, pois a freqüência de oscilação de um cristal varia com a temperatura. É necessário manter a temperatura estável para manter a precisão da medida. Também é importante obedecer e levar em conta o tempo de "warm up" do circuito, que é o tempo que ele demora para estabilizar e funcionar com precisão máxima.

Em geral, pode-se obter OCXO's de algumas dezenas de MHz. A intenção neste projeto é usar um OCXO próximo de 180MHz para fornecer o sinal de referência, um valor elevado, de modo a reduzir o erro intrinseco na medida, além de poder utilizá-lo também como clock do circuito.

Nota-se também que os instrumentos mais caros possuem um cristal de Rubidio, aparentemente mais estável que os comuns. Há ainda a possibilidade de usar uma medida atômica, como um relógio de Césio, como existem em alguns equipamentos de instrumentação e calibração de laboratórios.

## 2.2.2 Organização de sistemas digitais

Sendo um projeto de hardware digital, foram utilizados muitos conceitos de Organização de Sistemas Digitais. Além disso, foram utilizados conceitos de projeto de sistemas dedicados (embedded systems).

### 2.2.2.1 Fluxo de Dados e Unidade de Controle

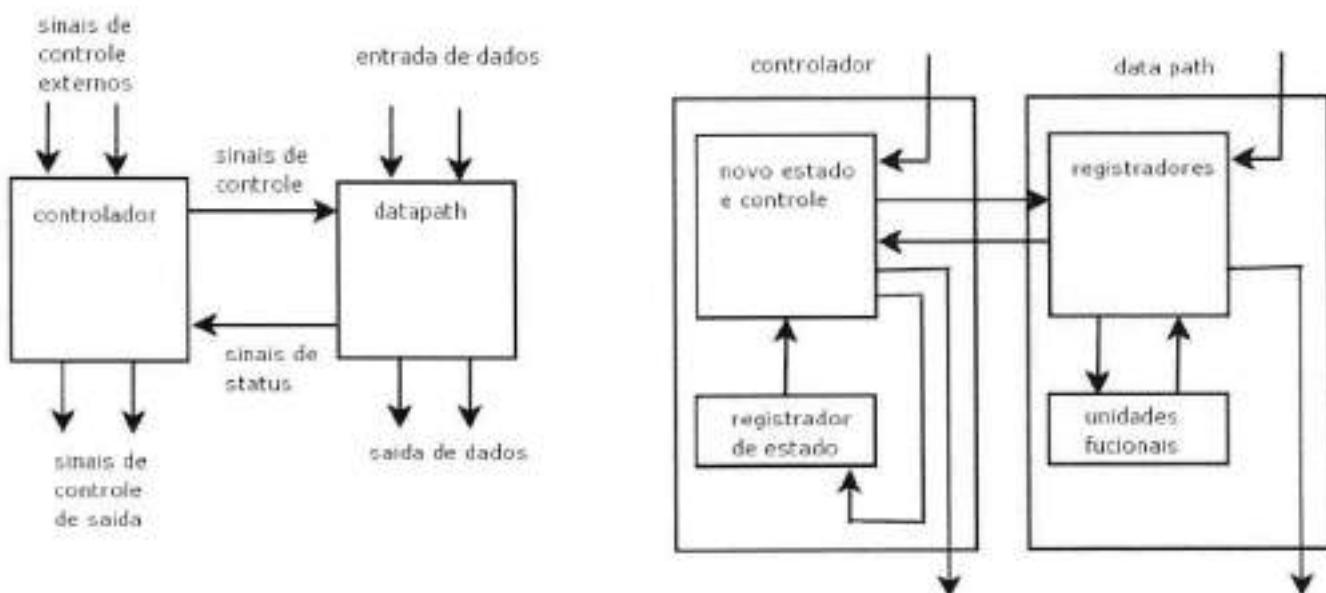

A estrutura básica de um circuito digital é composta por duas partes distintas que interagem para realizar o comportamento funcional do circuito: Fluxo de Dados e a Unidade de Controle.

O Fluxo de Dados é composto em geral por registradores, unidades funcionais e alguns elementos de interligação arranjados na topologia adequada a implementação do algoritmo executado pelo módulo digital.

A Unidade de Controle é um circuito seqüencial que determina as ações que devem ser executadas no Fluxo de Dados na ordem especificada pelo algoritmo do módulo e nos instantes corretos determinados pelas relações de tempo existentes entre o componente físico e o módulo. A Unidade de Controle é composta, em geral, por um registrador de estado, por uma lógica responsável pela determinação do próximo estado e por outra lógica responsável pela determinação dos valores da saída, além de, nos circuitos síncronos prover também a lógica de geração de todos os sinais de tempos necessários.

#### **2.2.2.2 *Síntese de processador dedicado***

Como descrito, o funcionamento correto do circuito depende de ele funcionar com alto desempenho. É crítico que o circuito funcione com a máxima eficiência.

O processador dedicado é constituído de fluxo de dados com capacidade de guardar e manipular dados e um controlador capaz de manipular os dados através desse fluxo. Alguns sistemas requerem tarefas tão específicas que um processador dedicado deve ser projetado para cumprir tal tarefa. Este é o caso deste projeto. Esse tipo de circuito é chamado de "custom single-purpose processor".

Assim como os processadores comuns, estes também são baseados em lógica combinacional. Porém, convertemos o programa gerado em uma Máquina de Estados Finitos (FSM, finite state machine) representando a unidade de controle, que é criada através de exemplos construtivos adaptados para cada caso.

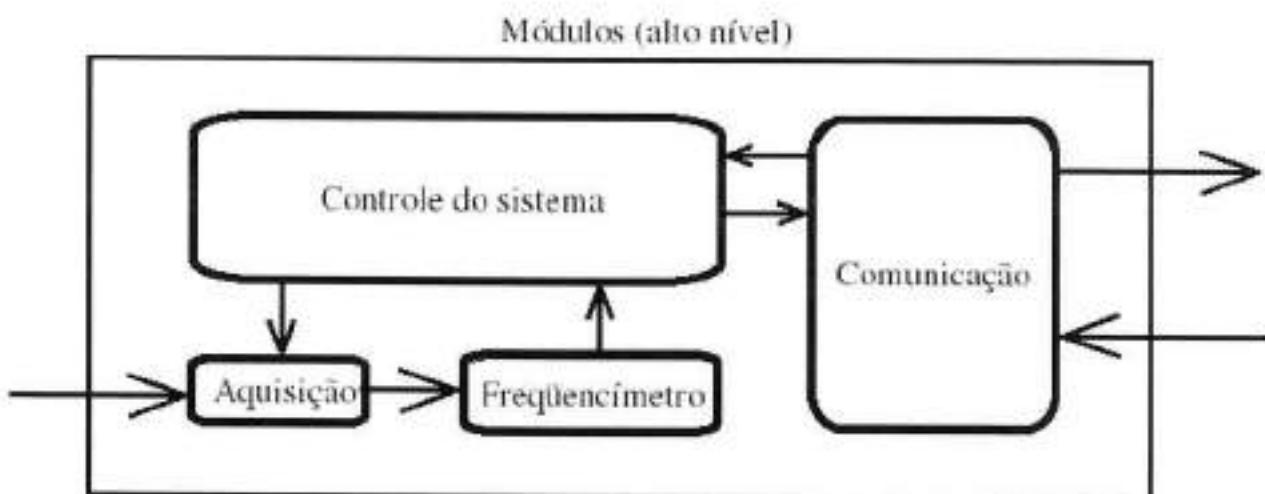

Figura 1: Estrutura geral de um módulo digital

O fluxo de dados (ou datapath) é criado observando a seguinte regra:

- 1) Criar registradores para as variáveis declaradas

- 2) Criar unidades funcionais para as operações de processamento que são executadas

- 3) Conectar as portas lógicas, registradores e unidades funcionais, com multiplexadores e selecionadores de sinais, se necessário

- 4) Criar identificadores únicos para cada sinal de controle e de status dos componentes do fluxo de dados

Após este procedimento básico é possível otimizar o sistema gerado, tanto o programa quanto a FSM. O uso de melhores algoritmos, simplificações podem tornar o programa mais eficiente. A máquina de estados pode ter estados repetidos, transições desnecessárias.

Pode-se usar técnicas de otimização e minimização para reduzir o tamanho dos circuitos e o número de estados. Esta tarefas são feitas durante a alocação de operações que serão realizadas em cada estado e na alocação de tipos de componentes que serão utilizados no fluxo de dados.

### 3 Especificação do Projeto

Esta seção consiste na descrição de toda a especificação do projeto, desde seus principais requisitos até a explicação de detalhes do seu funcionamento.

#### 3.1 *Especificação dos requisitos*

Após conversa com os orientadores do projeto, foram definidas dentro do objetivo traçado algumas características importantes que o sistema deve possuir. Além disso, existem restrições de projeto que acabam por induzir uma certa abordagem ou tecnologia. Desta forma, os principais requisitos do projeto foram:

- **Possibilidade de construção em placa compacta**

Para poder ter operação tanto embarcada (aviões) como em terra e poder ser transportado sem grande dificuldade o projeto deve possibilitar uma futura implementação em placa de dimensões reduzidas.

- **Altíssima precisão na medida**

Para poder ser utilizado no projeto do gravímetro, o sistema desenvolvido necessita de altíssima precisão nas medidas, já que os valores de gravidade mensurados alcançarão 3 casas decimais.

- **Alta velocidade de operação**

Para se atingir o nível de precisão de medida desejado, é necessário que a aquisição e processamento dos sinais seja feita em uma velocidade elevada (localização da posição geográfica da medida).

- **Reconfigurabilidade**

Como o freqüencímetro poderá vir a ser utilizado também em um magnetômetro, ele deve possuir facilidade de alteração de suas configurações principais.

- **Facilidade de operação**

É desejado que o equipamento projetado possua uma certa facilidade de operação, para que os técnicos que o utilizarem futuramente não tenham que enfrentar maiores problemas.

- **Adequada disponibilização de dados**

Os dados de saída do sistema devem ser disponibilizados de forma adequada, para que possam ser utilizados facilmente pelo usuário final, podendo ser relacionados a dados recolhidos de outras fontes.

### **3.2    *Detalhamento do projeto***

A partir das limitações do projeto, começaram a ser pensadas soluções para o sistema medidor de freqüência. Estão listadas abaixo algumas das conclusões iniciais sobre o problema, para se atingir os requisitos.

- **O sistema será de operação dedicada**

Não é possível utilizar um sistema pronto de medição de freqüência. Isso é devido ao alto grau de especialização do sistema, não seria possível atingir os requisitos de projeto;

- **O sistema deve ser compacto, no formato de uma placa compacta**

Este formato é adequado ao de um sistema embarcado, não devendo ocupar muito espaço, e sendo robusta e de fácil operação;

- **O sistema será implementado em hardware**

Por exigir um grande desempenho (muitas contagens por segundo), um altíssimo nível de precisão e por ser um sistema dedicado, a implementação em hardware passou a ser altamente recomendável em detrimento a um possível desenvolvimento em software.

- **o tratamento de sinais será feito em FPGA**

A FPGA (field programmable gate array) é um circuito integrado especial que pode ser programado para conter diversos tipos de circuitos de lógica digital. Ele é denso (pode implementar grandes circuitos, até pequenas CPUs RISC), altamente reconfigurável e flexível, além de ser um hardware dedicado para a medição, o que dá desempenho e segurança à implementação. Ela traz grande flexibilidade, pois pode abrigar outras partes do projeto (como o controle do display, ou o driver de USB), desde que haja espaço (leia-se pinos suficientes) para i/o e área disponível para o circuito lógico na FPGA.

- **Os dados devem ser transmitidos para um computador**

O sistema deve fornecer os dados a um computador, através de uma saída comum, tais como cabos seriais (opção escolhida), USB ou FireWire, pois os dados serão tratados e incorporados ao conjunto de dados levantados pelos outros sistemas.

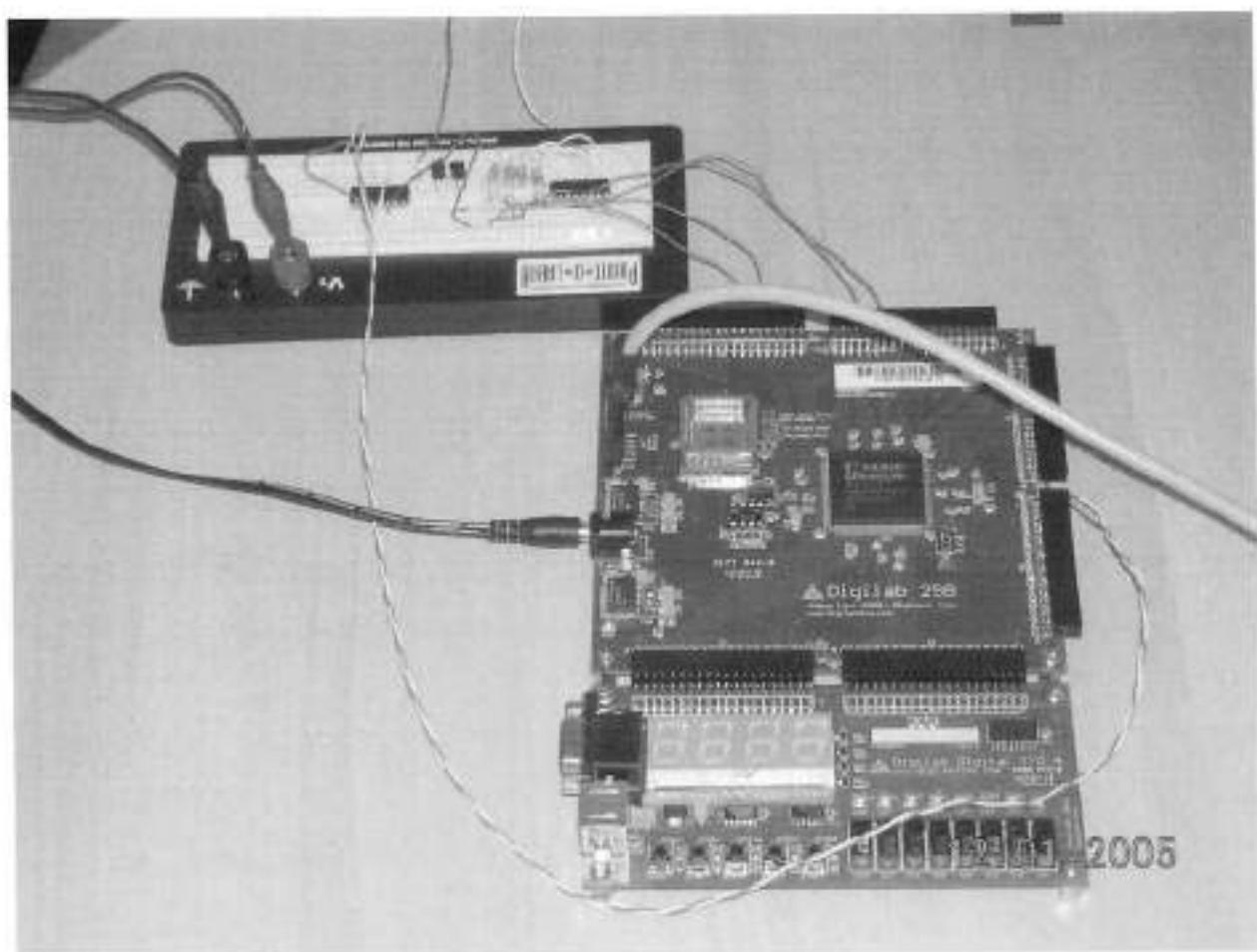

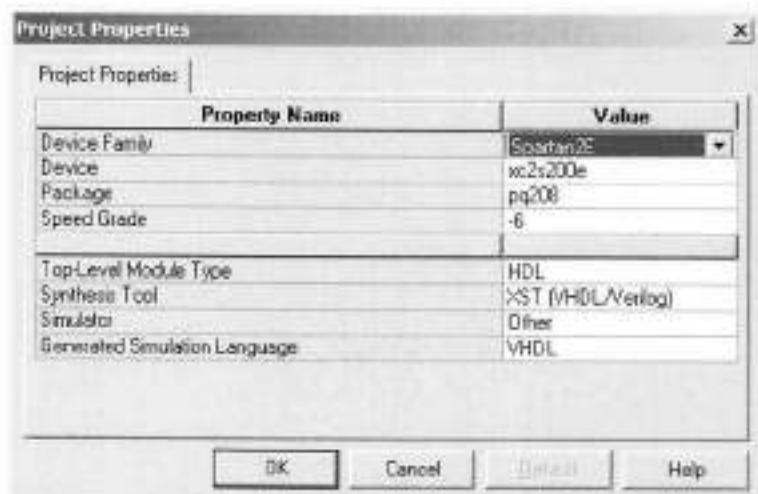

Foi utilizada para o desenvolvimento do trabalho de formatura uma placa de desenvolvimento em FPGA da Digilent Inc. A placa consiste em dois módulos: o módulo principal da FPGA e um módulo de I/O digital que utilizamos para verificar o funcionamento. A placa da Digilent contém uma FPGA model Spartan IIe, da Xilinx, que é a família (Spartan) de chips alvo do nosso desenvolvimento. Foi utilizado o ambiente de desenvolvimento da Xilinx chamado ISE 7.1i, que permite realizar o projeto do circuito digital e enviar para a placa de desenvolvimento através do protocolo JTAG. Na fase de desenvolvimento é possível utilizar um simulador de waveform chamado Modelsim MXE, que opera em conjunto com o ISE. A placa de desenvolvimento foi gentilmente cedida pelo LSI-USP, Laboratório de Sistemas Integráveis da USP.

### **3.3    *Características funcionais***

Neste tópico será tratado todo o funcionamento do sistema projetado e de seus subsistemas.

### 3.3.1 Como funciona o freqüencímetro

O objetivo desta seção é dar uma visão geral de como é feita uma medição utilizando o freqüencímetro. Será dada uma visão de alto nível do funcionamento, já que os detalhes de cada módulo estão explicados posteriormente, e dar uma introdução geral ao sistema.

Será explicado o sistema começando da saída do gravímetro até chegar no dado processado no computador, que são os limites extremos deste sistema, cuja tarefa é intermediar a "conversa" entre o gravímetro e o computador, e servir de ponte de ligação entre estas camadas.

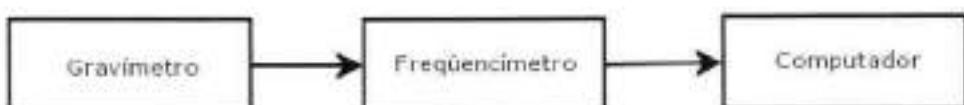

Figura 2: Sistema geral do gravímetro

O sinal do gravímetro é uma senóide. A freqüência dessa senóide representa uma indicação do valor de gravidade e é a informação que se quer coletar. Além disso, é importante localizar no tempo o momento da medição, pois como o instrumento pode se mover (embarcado no avião) esse dado também é importante para localizar a posição geográfica em que foi feita a medição.

O sinal é recebido e tratado, para evitar ruidos. Em seguida ele é digitalizado e entra na FPGA. A FPGA também recebe uma informação de base de tempo estável (geralmente de um cristal, ou um sinal de GPS, que é muito estável). O sinal é comparado com essa base de tempo para gerar a informação de tempo. O sinal depois é dividido por essa freqüência de base, para sabermos sua freqüência com alta precisão. Além disso, pelo número de ciclos entre cada medição podemos também estimar o tempo desde a última medição, que é o outro dado passado.

Os dados gerados após o processamento devem ser codificados segundo o protocolo estabelecido, para então ser transmitido pela controladora de comunicação serial (UART) para o computador. Este recebe através de uma porta serial (ou cabo USB, emulando uma porta serial virtual) os dados enviados pelo processador na FPGA. Um programa responsável por estabelecer e manter a comunicação serial recebe os dados da FPGA e decodifica as informações segundo protocolo de comunicação estabelecido em cima da comunicação serial, e pode mostrar os dados na tela, imprimir para um arquivo de dados (que são a freqüência e o tempo decorrido desde a última medição), ou gerar gráficos, entre várias outras opções.

### 3.3.2 Como funcionam os módulos

#### 3.3.2.1 Aquisição do sinal

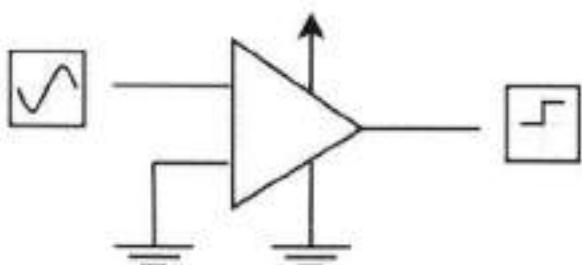

Neste tópico será descrito o funcionamento do sistema de aquisição de sinal. A visão geral desta etapa está ilustrada abaixo.

Figura 3: Sistema de aquisição de sinal

### 3.3.2.1.1 Conversão A/D

O sinal utilizado como entrada provém do gravímetro. Ele foi especificado pelos desenvolvedores do gravímetro como uma onda senoidal, com amplitude de 3 V, offset nulo, e freqüência variando de 250 a 3000 Hz.

Essa entrada deve ser digitalizada para realizar o processo de medição pelo método de contagem. O outro método que não necessita de digitalização é a medição de freqüência por ressonância. O método tradicional de medição de freqüência consistem em gerar eventos cíclicos que provoquem pulsos ou trens de pulsos e contar a quantidade de pulsos decorridas durante o evento repetitivo.

Para tanto, o sinal senoidal de entrada é convertido em uma onda quadrada que seja compatível como o circuito digital. Isso é feito através do CI comparador LM339. Esse CI consiste basicamente de amplificadores operacionais simples.

Foi utilizado um dos Amp-Op's do chip em aberto, e alimentado com uma tensão de  $V_{cc}=3.3V$  e a outra alimentação simétrica aterrada. Como o Amp-Op está em aberto e sem a ligação negativa, no semiciclo positivo da senóide, o sinal será saturado em  $V_{cc}$ , enquanto que no semiciclo negativo, o sinal ficará aterrado. Com isso é gerada uma onda quadrada que representa a mesma freqüência do sinal senoidal de entrada e compatível com o circuito de níveis de tensão LVTTL, e assim pode ser ligado diretamente a um pino de entrada da FPGA, para ser processado.

O processo de digitalização altera ligeiramente o duty cycle do sinal. Isso porque o sinal fica mais tempo em nível baixo do que em nível alto. Isso, porém não afeta a freqüência do sinal, pois para cada ciclo da senóide é gerada uma borda de subida, que é utilizada para disparar um processo de contagem.

### 3.3.2.1.2 Filtragem

O segundo estágio, último antes da digitalização, consiste na filtragem do sinal. Esse estágio não está implementado no protótipo montado a partir da placa de desenvolvimento, pois o sinal utilizado provém de um gerador de sinais, e não seria necessário filtrar tal sinal. Na implementação real, é necessário remover os ruídos presentes através de um adequado filtro analógico.

### 3.3.2.1.3 Pre-scaling

A operação de pre-scaling consiste em alterar um sinal de entrada para facilitar o funcionamento do circuito. Por exemplo, aquisita-se um sinal de microondas, e através de um divisor de freqüência reduz-se o sinal até que ele entre na faixa de freqüências de rádio. O processamento do sinal é feito através de um circuito que opera nesta região. Após o processamento, o sinal é restaurado para a freqüência de microondas.

Geralmente quanto mais rápido um sinal, mais tempo temos que amostrar ou maior o desempenho exigido do circuito. O efeito de pre-scaling do sinal (utilizar um sinal mais lento) equivale no nosso circuito a aumentar a quantidade de ciclos amostrados no sinal de entrada, e a idéia é semelhante: reduzir os erros de medição (diminuir a significância) pelo aumento do universo de dados existente.

### 3.3.2.2 Processamento do sinal (FPGA)

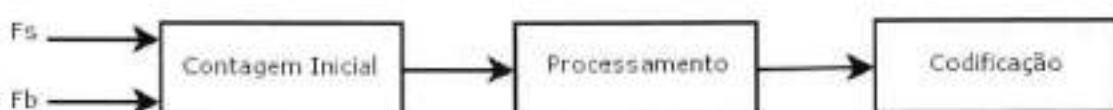

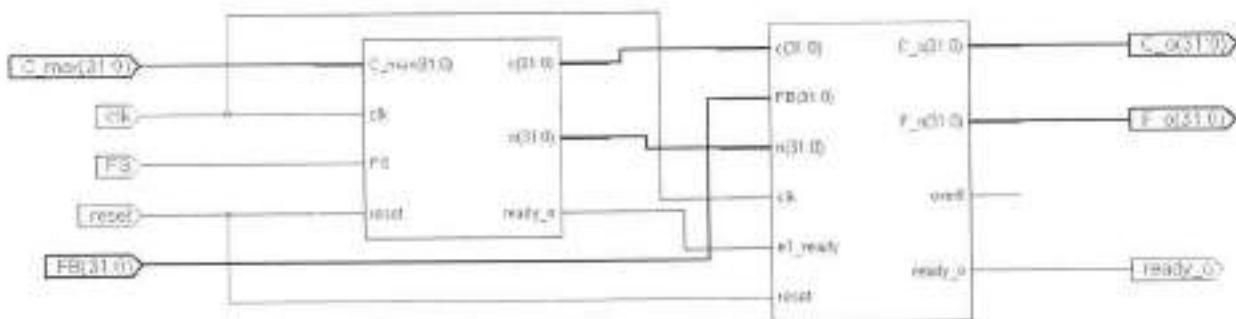

Este seção descreve o funcionamento do processamento do sinal pela FPGA. Seu esquema geral está ilustrado abaixo.

Figura 4: FPGA – alto nível

#### 3.3.2.2.1 Contagem inicial

O primeiro estágio tem por tarefa armazenar as informações dos sinais de entrada. Os sinais de entrada são dois, sendo o primeiro deles o sinal medido do gravímetro, e o outro sinal consiste na base de tempo. No protótipo feito na placa de desenvolvimento Digilent o sinal da base de tempo é o próprio clock.

Os dados digitalizados são contados (bordas de subida) para determinar quantos ciclos foram executados durante um procedimento de medição.

Os contadores e registradores são controlados por uma U.C. (unidade de controle) que controla o momento em que a aquisição de dados se inicia e se encerra, e após a aquisição os dados são enviados para registradores de saída, para serem processados.

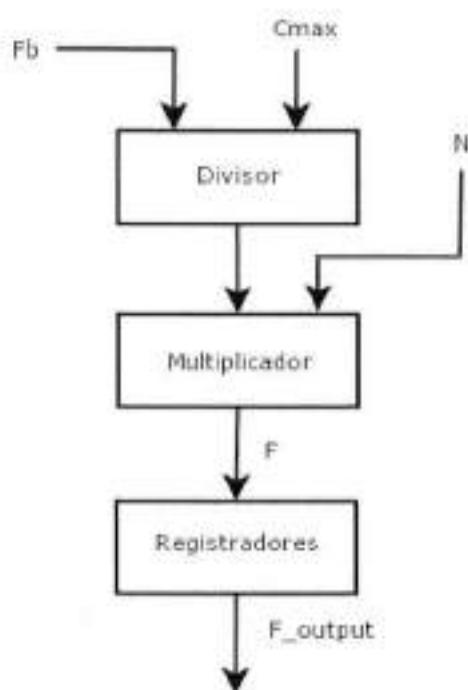

### 3.3.2.2.2 Processamento das entradas

O bloco de processamento das entradas é o coração do circuito lógico, e é também o maior bloco em VHDL do circuito. Ele é responsável por gerar os resultados pedidos de freqüência e tempo entre medidas para que eles sejam enviados para o micro, a partir das entradas do sistema.

Este bloco se subdivide em dois grandes blocos: o bloco divisor e o multiplicador. O bloco divisor recebe os sinais inicialmente e divide a freqüência de base pela contagem. O valor é multiplicado pelo número de períodos do sinal medido para obter o valor da freqüência esperado e então armazenado em um registrador de saída.

Figura 5: Processamento do sinal

Gera as saídas:

- $(F_b/C)^N = \text{freqüência}$

- Contagem de clocks (tempo entre medidas)

### 3.3.2.2.1 Divisor

O circuito divisor realiza a operação de divisão de números inteiros e é uma implementação baseada no circuito de divisão do processador Leonel, que é uma implementação de uma CPU compatível com a definição do processador Sparc V8, um processador RISC da Sun Microsystems, feita pela ESA (European Spacial Agency, Agência Espacial Européia).

O divisor implementa o algoritmo de divisão digital Radix-2. O algoritmo Radix é muito famoso e de uso comum comercial em processadores que implementam a operação de divisão em hardware, servindo de base para vários circuitos implementados em chips da Intel, Sun, etc.

### 3.3.2.2.2 Multiplicador

O segundo estágio multiplicador é muito mais simples que o primeiro, pois existem implementações simples de multiplicação em circuitos digitais, diferentemente do caso da divisão.

O segundo estágio é uma implementação em VHDL simples que realiza a multiplicação do valor do divisor pelo número de períodos contados para que se tenha a freqüência medida em Hz (e não em ciclos de clock ou contagem pura).

Existe um circuito de apoio para armazenar os valores e controlar o envio dos mesmos para estágios posteriores de processamento.

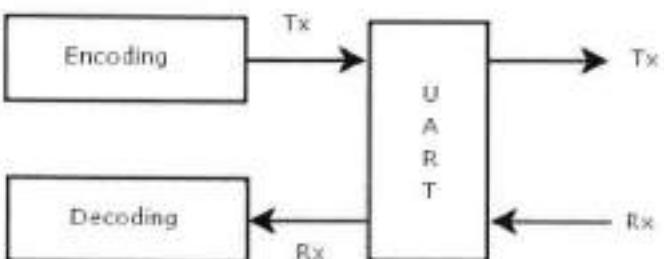

### 3.3.2.2.3 Codificação da comunicação

O terceiro bloco principal da FPGA é o bloco responsável pela comunicação entre a FPGA e o computador. As tarefas principais do bloco podem ser divididas em duas partes: a) Tratamento dos pacotes RS232 e b) Tratamento do protocolo em cima dos pacotes (encoding e decoding)

A primeira parte trata do envio e recebimento dos pacotes em padrão RS232. Essa parte compreende basicamente o bloco da UART. A parte do envio de está explicada no próximo tópico.

A outra parte necessária para se fazer a comunicação é a codificação das informações que será enviada pela UART.

Essa parte é composta basicamente por buffers e registradores que enviam as informações na ordem esperada pelo protocolo.

Os dados recebidos da UART para o sistema de decodificação são colocados em registradores conforme os pacotes de controle enviados. O protocolo completo está especificado em um tópico posterior.

Essa parte do circuito tem função e funcionamento análogos ao do programa em C que trata a "outra ponta" da comunicação, serial, do lado do computador.

Pode-se considerar esse bloco como uma codificação de nível superior à codificação de pacotes seriais da UART (ou seja, está em uma camada de rede superior), pois ela leva em conta os dados que estão sendo enviados.

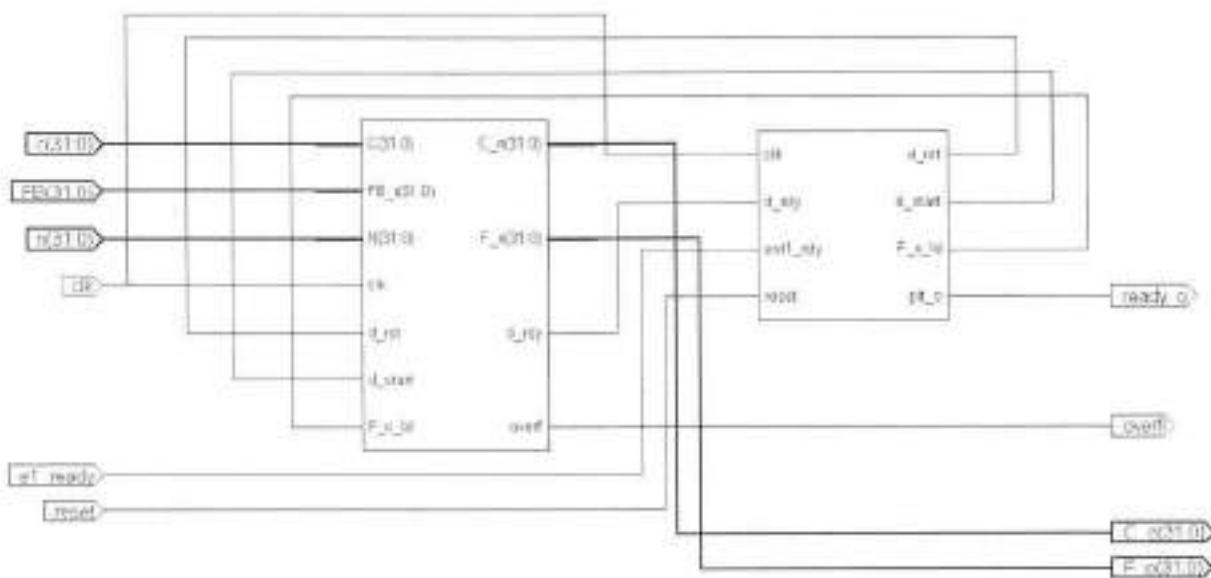

### 3.3.2.3 Comunicação de dados

Esta seção trata do subsistema de comunicação do circuito da FPGA com o computador. A figura abaixo ilustra o esquema desta etapa do sistema.

Figura 6: Sistema de comunicação

#### 3.3.2.3.1 Implementação da UART

O termo UART significa Universal Serial Asynchronous Receiver-Transmitter, ou seja, é o circuito digital responsável por converter os bits para a transmissão de dados RS232,e vice-versa.

Através da UART o circuito "conversa" com o computador, podendo enviar os dados processados, e receber informações de reconfiguração.

O circuito para permitir a comunicação no padrão RS232 é de baixa complexidade, e não ocupa muita área. Muitos circuitos dedicados, tais como microcontroladores possuem chips de UART integrados no seu encapsulamento. Para evitar a inclusão de novos chips, fizemos o design da UART de forma interna à FPGA.

A UART foi implementada em VHDL e faz parte do circuito digital que funciona na FPGA. Abaixo podemos ver o símbolo funcional correspondente à UART no simulador ISE:

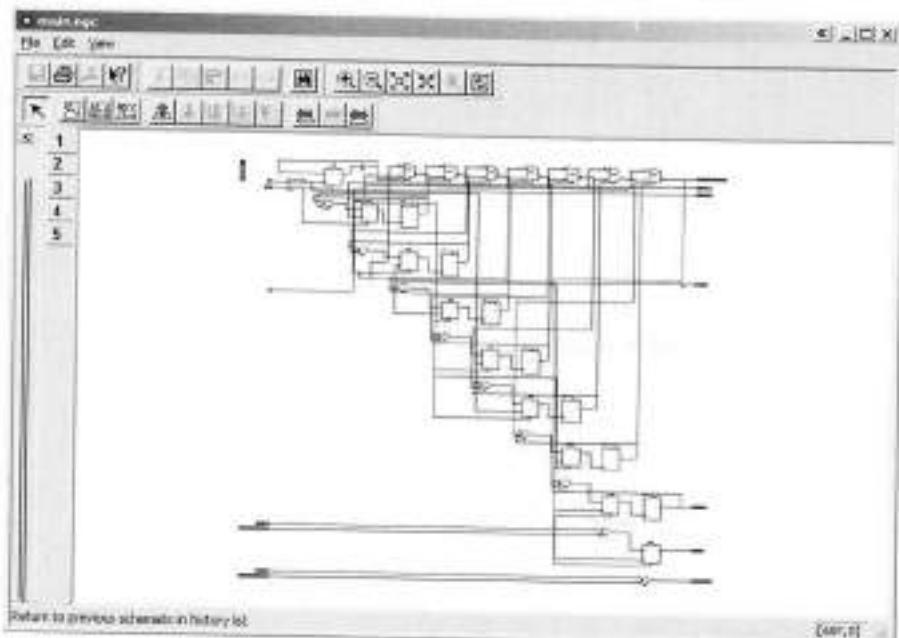

Figura 7: Símbolo funcional da UART no ISE.

### 3.3.2.3.2 Protocolo de transmissão

Para a demonstração do conceito de transmissão e reconfiguração por transmissão serial do nosso sistema criamos um protocolo básico para a comunicação.

Cada pacote de transmissão serial compreende 11 bits. Cada pacote possui 8 bits de dados que podem ser transmitidos (payload do pacote). Os 3 bits adicionais (que não fazem parte da informação) são:

- Bit de início de transmissão

- Bit de fim de transmissão

- Bit de paridade

Foi definido pela equipe o conteúdo que cada comunicação serial deveria ter. Segue abaixo o conteúdo dos pacotes recebidos pelo micro e aqueles que são enviados.

### • Protocolo FPGA para micro

Os pacotes recebidos da FPGA compreendem a maior parte dos dados em funcionamento normal. Uma comunicação completa da FPGA com o PC deve conter todas as informações de uma medição realizada pelo freqüencímetro. Foram adicionados também alguns bits para detectar erros e separar variáveis. Separou-se sempre em grupos de 8 bits (ou seja, 1 byte) para que eles sejam enviados juntos em um pacote serial RS232. O esquema de envio segue abaixo:

- 1 byte de identificação de transmissão: seqüência característica que indique que um conjunto de dados de medição será enviado

- 1 byte de informações: essas informações compreendem 2bits com o ID do freqüencímetro/gravímetro/sinal (para o caso de existir mais de um), 2 bits do modo de operação, 4 bits reservados para uso futuro.

- 1 byte de início da medida

- 4 bytes da medida de freqüência

- 1 byte de fim da medida

- 4 bytes da medida de tempo

- 1 byte de fim de transmissão

Figura 8: Protocolo / encapsulamento.

### • Protocolo micro para FPGA

Os pacotes enviados do micro para a FPGA visam a reconfiguração do circuito durante a medição. O protocolo abaixo corresponde a um exemplo básico em que é possível alterar a freqüência de base e o número máximo de contagem por medição ( $F_b$  e  $C_{max}$ , que são valores de 32bits) para um certo sistema de aquisição na FPGA. Abaixo segue o esquema:

- 1 byte de identificação de transmissão

- 1 byte de informações: 2 bits de freq-id, 2 bits modo de operação, 4 bits reservados para uso futuro

- 1 byte de inicio de dados

- 4 bytes com a  $F_b$

- 1 byte separador

- 4 bytes do  $C_{max}$

- 1 byte de fim de transmissão

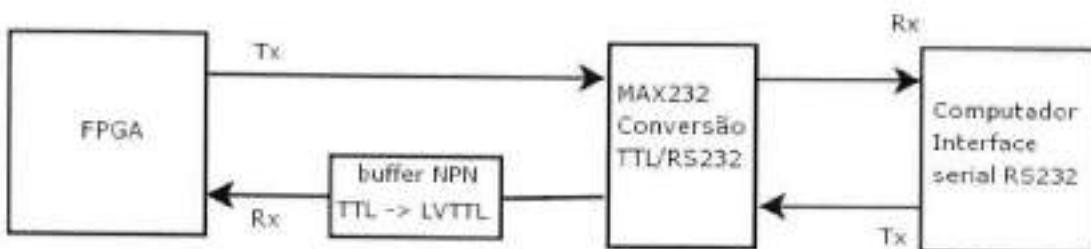

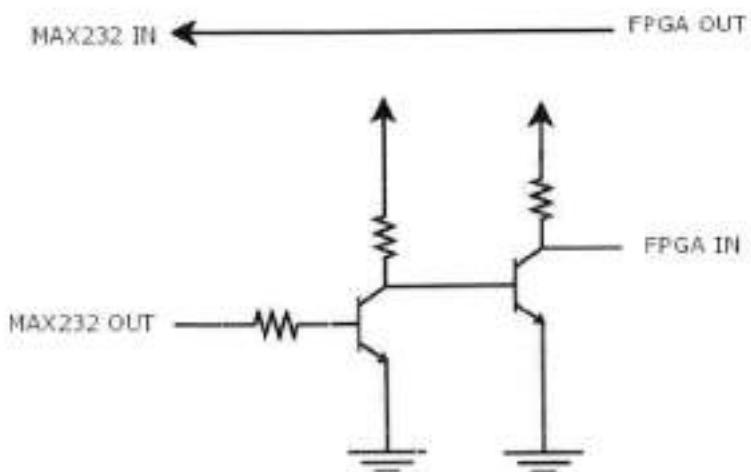

#### 3.3.2.4 Conversão de sinais e alimentação

Nesta seção será descrito o funcionamento de todos os blocos de conversão de sinais e níveis necessários ao sistema. Sua estrutura geral está ilustrada no esquema abaixo.

Figura 9: Sistema de conversão de sinais.

### **3.3.2.4.1 Conversão de níveis TTL / LVTTL / RS232**

O sistema do freqüencímetro utiliza componentes auxiliares à placa da FPGA principalmente para a comunicação de dados. Esses circuitos e sistemas auxiliares necessitam de algumas conversões de sinal para o funcionamento.

Nem todos os circuitos auxiliares operam com o mesmo nível de tensão. Os componentes TTL são facilmente encontrados, enquanto que os LVTTL não são tão comuns assim.

Além disso, precisa-se fazer com que a FPGA possa se comunicar com PC em padrão RS232. E para isso é necessário mais um sistema de conversão de tensão.

Na seção sobre o desenvolvimento do projeto, maiores detalhes sobre como obter as transições de tensão e quando elas são necessárias serão tratados. Às vezes a conversão não é explicitamente necessária, por exemplo, no caso de LVTTL para TTL, pois o nível 0 lógico coincide, e o nível 1 do LVTTL, apesar de menor, já é suficiente para o circuito TTL perceber como 1 lógico.

### **3.3.2.5 Processamento dos dados no computador**

#### **3.3.2.5.1 Programa receptor de dados**

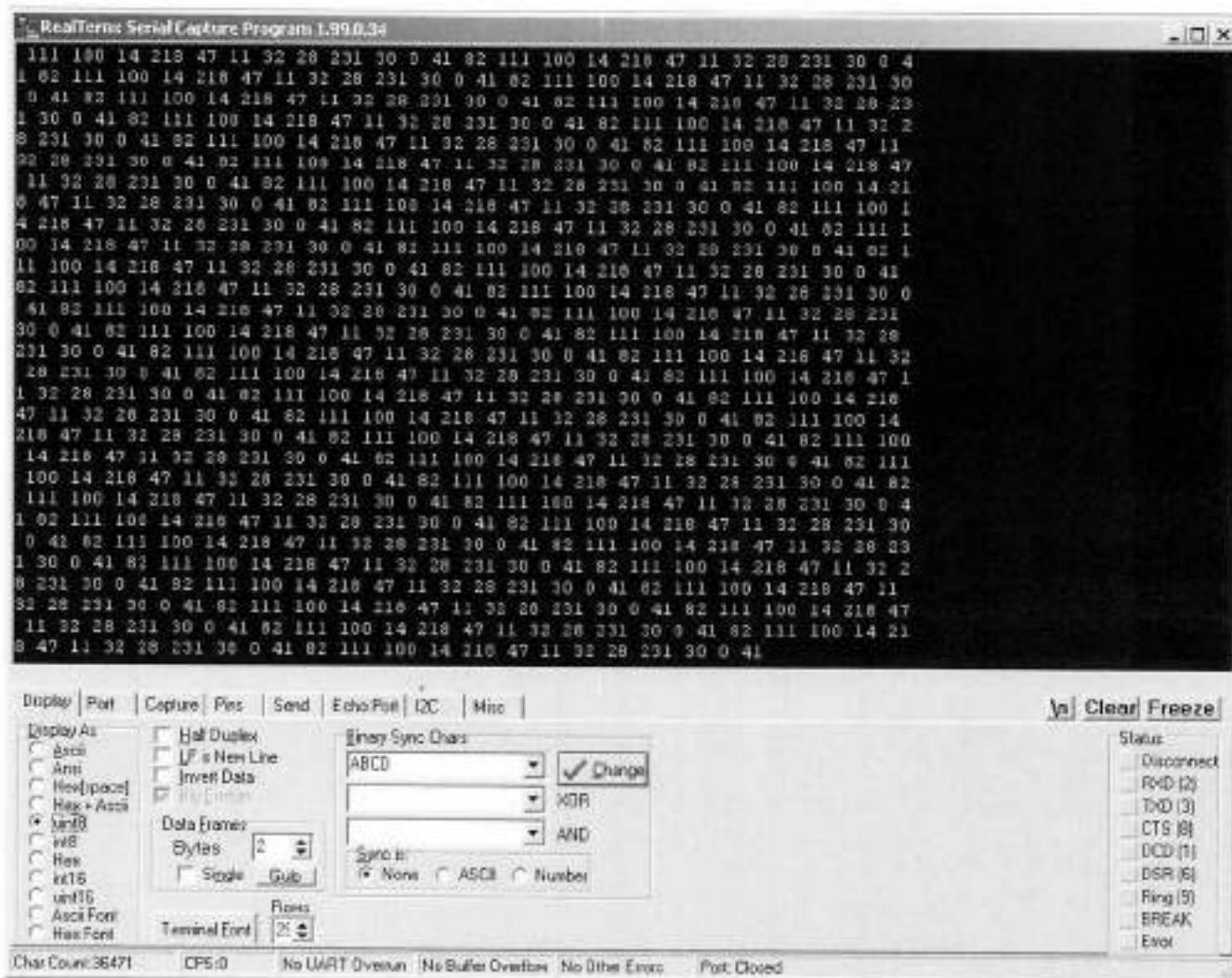

O programa receptor de dados é um programa de testes muito simples para testar o recebimento e transmissão dos dados. Para testar o funcionamento utilizamos priori um programa de terminal de texto comum, tal como o HyperTerminal no Windows ou o minicom no Linux.

A parte de recebimento dos dados deve basicamente emular o comportamento de um cliente de terminal. O motivo de não ser utilizado simplesmente um cliente de terminal é que um

cliente de terminal sempre converte as seqüências de 8 bits transmitidas em caracteres. Porém nem toda seqüência de bits gera um caractere válido no mapa de caracteres, e é possível que alguns resultados não sejam visualizados.

A parte de envio é codificada individualmente através de variáveis numéricas, representando cada conjunto de 8 bits. Após a codificação, é feita uma transformação de casting (mudança do tipo de variável) para codificar o dado a ser enviado em um tipo de 8 bits. Assim, é possível codificar qualquer seqüência de 8 bits sem o risco de ser necessário utilizar um caractere inexistente ou não imprimível.

O programa deve emular a característica do terminal serial, ou seja, manter um baud rate de 9600, paridade par e controle de fluxo por software. O programa pode ser facilmente implementado em C, acessando o dispositivo de porta serial disponível (ttyS0 no Linux, ou COM1 no Windows). Uma vez que seja possível manter a comunicação serial, programa deve conhecer o protocolo de transmissão dos dados (codificação) para permitir a exibição correta dos dados na tela e o encoding de dados a serem enviados para a FPGA.

## 4 Metodologia

Esta seção se dedica a explicar um pouco sobre nossa filosofia de projeto, e como foi pensado o desenvolvimento do trabalho de formatura em toda a sua extensão.

### 4.1 Implementação

*"Rule #1: Modularity: Write simple parts connected by clean interfaces.", from The Basics of Unix Philosophy*

O projeto, desde a sua concepção foi pensado sempre em termos de módulos, unidades funcionais e interligações.

As palavras chave deste processo são:

- Modularidade

- A união faz a força

- Faça pouca coisa, mas faça bem feito.

- KISS (keep it simple, son)

Muitos dos tópicos relembram a filosofia Unix de desenvolvimento. Hove sempre a busca em manter o código limpo. Manter a depurabilidade do código (habilidade de debugar o sistema).

Os blocos que adicionam funcionalidades foram mantidos com o mínimo necessário. Interligar blocos simples para prover funcionalidades complexas. Manter as interfaces simples ou sistemas complexos encapsulados (como o caso do sistema de divisão).

## 4.2 Metodologia de Teste

A metodologia de teste se baseia em uma linha que decorre diretamente da filosofia da concepção.

Testamos inicialmente pequenos blocos. Tentamos manter o teste em simulação o máximo possível. Uma vez que vimos que o sistema funciona, adicionamos novos sistemas, anteriores ou posteriores e testamos funcionalidade do dois corretamente. Mesmo que ambos aparentem terem funcionamento correto individualmente, isso não implica de maneira alguma que os blocos vão funcionar bem quando interligados.

Esse crescimento e teste coordenado a partir de uma "semente de blocos" permitem manter o sistema debugável e num ponto funcional a cada instante. Se alguma coisa não funciona corretamente, pode-se começar a investigar o problema na interface entre o último bloco adicionado e o sistema principal estabelecido.

Foi iniciado o desenvolvimento dos sistemas principais da FPGA, e foram sendo adicionados blocos adjacentes, até concluir toda a FPGA. Uma vez que a FPGA esteja funcionando corretamente, foram adicionados os módulos de interface que se comunicam com o sistema principal da FPGA, notoriamente a parte de aquisição e tratamento da entrada, e a parte da comunicação serial do dado processado de saída.

No desenvolvimento dos circuitos "físicos" (ou seja, os circuitos que não são baseados em VHDL), tentou-se manter o mesmo conceito, de ir verificando até que ponto o circuito está funcionando corretamente, e ir adicionando partes até o término do sistema.

## **4.3     Organização**

Este subtópico relacionado à Metodologia de Trabalho foi reservado para falar um pouco das ferramentas utilizadas pelo grupo para facilitar a dispersão da informação e organizar os dados de forma comprehensível. O uso destas ferramentas permitiu um considerável aumento de produtividade, além de facilitar, em geral, a organização do grupo.

### **4.3.1     Ferramentas de apoio**

Geralmente a principal ferramenta utilizada para organizar a comunicação e informação do grupo é o contato por email. Além do email, buscou-se organizar as informações disponíveis em um lugar unificado, de fácil acesso para todos e que estivesse constantemente atualizado.

Além disso, houve uma certa dificuldade na organização das várias informações que necessitam ser compiladas em um relatório. Por isso, foi testado no fim do projeto, o uso de uma ferramenta para organizar idéias, brainstorms.

Como são ferramentas interessantes, serão citadas aqui algumas idéias que ficam também como sugestão para quem precisar gerenciar alguma situação semelhante.

#### **4.3.1.1     Wiki**

O wiki é uma espécie de site http, em que qualquer visitante possui a capacidade de alterar o conteúdo. Isso permite agilidade na troca de informações, uma facilidade para que em algum momento que se acesse o wiki, tenhamos os dados mais atualizados.

Por exemplo, neste projeto foram mantidos no wiki dados como cronograma, contatos realizados para o TF, todas as documentações e links utilizados, uma área de armazenamento com datasheets, manuais e referências úteis, além de vários outros dados.

Quando era necessário obter alguma informação sobre o wiki, por exemplo, o que foi colocado na última apresentação de trabalho de formatura, ou qual o link para um exemplo de utilização de freqüencímetros, todos do grupo sabiam que aquela informação estaria no wiki, não sendo necessário perder tempo com uma busca novamente.

É necessária uma certa organização no uso da ferramenta, e também um comprometimento do grupo em atualizar o wiki com os dados, o que pode ser até uma tarefa cansativa, mas que traz bons retornos.

Figura 10: Tela principal do nosso Wiki.

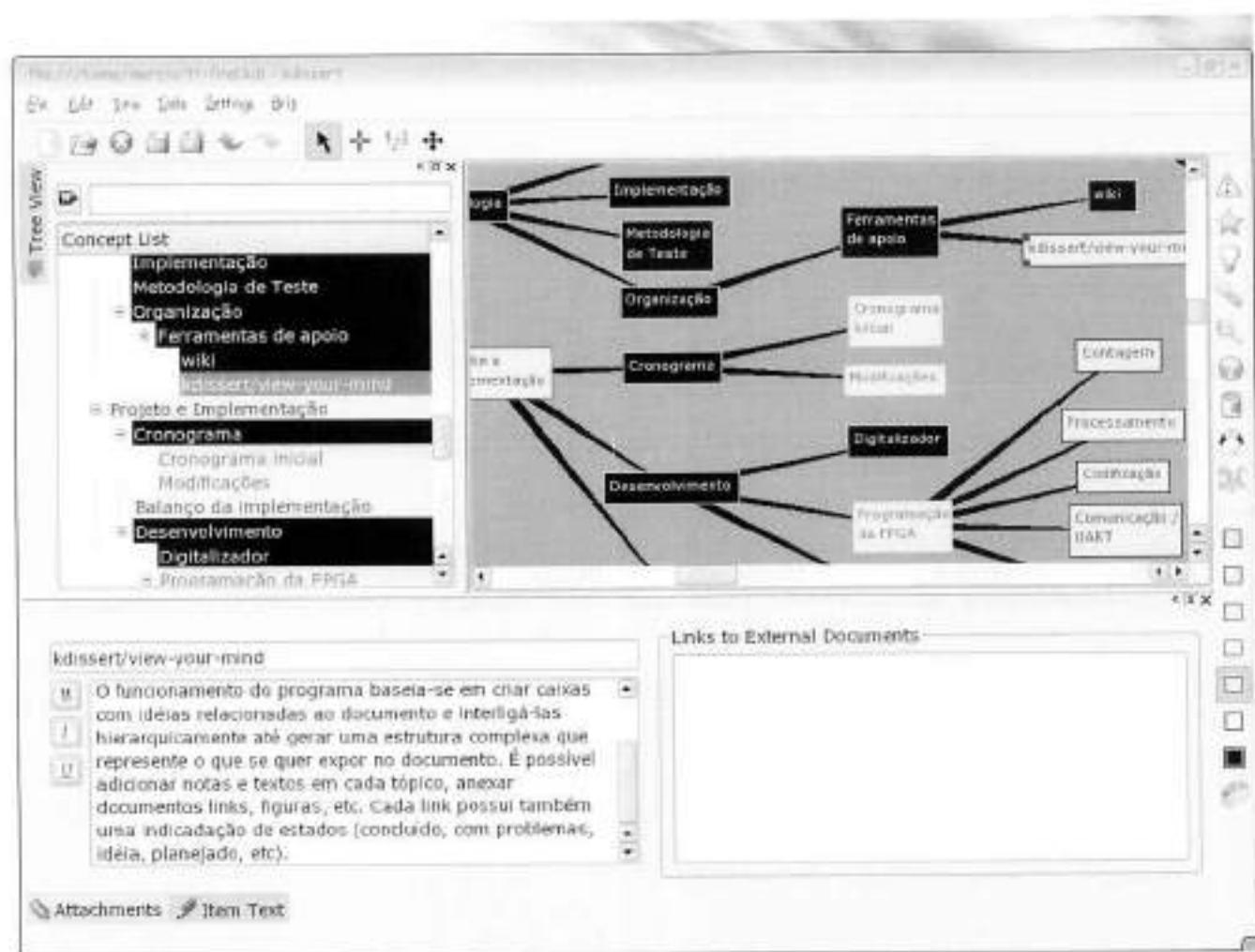

#### 4.3.1.2 *Kdissert/view-your-mind*

O Kdissert é baseado numa técnica chamada "View your mind", mas adaptada para a produção de documentos, tais como dissertações (daí o nome kdissert).

O funcionamento do programa baseia-se em criar caixas com idéias relacionadas ao documento e interligá-las hierarquicamente até gerar uma estrutura complexa que represente o que se quer expor no documento. É possível adicionar notas e textos em cada tópico, anexar documentos links, figuras, etc. Cada link possui também uma indicação de estados (concluído, com problemas, idéia, planejado, etc).

Assim a partir de idéias iniciais pode-se moldar o documento de acordo com as necessidades, e modificar seções inteiras através do religamento de alguns vínculos, de uma forma espacial, o que não seria possível (ou seria muito mais difícil) com uma estrutura de dados seqüencial, como num processador de texto comum.

Figura 11: Tela principal da ferramenta Kdissert/view-your-mind

## 5 Projeto e Implementação

Nesta seção serão detalhadas todas as ações realizadas para a implementação propriamente dita do projeto. Desde as decisões quanto a sua concepção quanto todas as fases da implementação de todos os seus subsistemas. Serão explicados desde testes iniciais de ferramentas importantes utilizadas até os últimos passos do desenvolvimento do sistema final, culminando com uma análise completa de todo este processo.

### 5.1 Pesquisa e concepção

Neste item serão descritas e explicadas várias etapas de pesquisa, experiência e estudo realizadas para a escolha e familiarização com as ferramentas, componentes e demais tecnologias utilizadas no desenvolvimento de todo o sistema. Além disto, serão exploradas também as decisões fundamentais da concepção do sistema consequentes destes trabalhos.

Quando foram definidos os requisitos de projeto junto com os orientadores, concluiu-se que o problema deveria ter uma abordagem diferente dos processadores de sinais convencionais. A problema da medição em alta velocidade necessitaria de um hardware especial para que o problema fosse resolvido. Uma solução comercial pronta do tipo COTS (commercial off the shelf system) certamente não seria adequada.

A aquisição de dados de alta velocidade geralmente é feita utilizando hardware dedicado sob medida. A flexibilidade de usar a FPGA para esse design torna essa opção muito atraente para esse tipo de projeto, além do que geralmente não se fazem largas quantidades para justificar

um design de um chip dedicado. É possível corrigir falhas e fazer upgrades com a simples troca de uma memória ROM.

A escolha do design em FPGA pareceu bem lógico para o desempenho esperado do circuito. Apesar do circuito não ter um throughput de medições muito alto ou exigente, manter o padrão da medida exige um circuito muito rápido, com clock elevado.

Estas foram as principais decisões quanto à concepção do projeto. As demais serão tratadas ao longo dos próximos tópicos.

### **5.1.1 Familiarização com o ISE 7.1 / ModelSim MXE**

Foi utilizado um simulador de design HDL chamado ISE Simulator 7.1i. Ele é produzido pela Xilinx Inc., mesma empresa que produz a FPGA, e basicamente funciona como uma IDE de programação para a FPGA em HDL (VHDL, verilog, etc). Além disso, existe um programa auxiliar chamado ModelSim MXE, que realiza simulações de forma de onda (waveform sim) para o circuito.

Utilizando o ISE Project, o MXE e uma placa de desenvolvimento da (placa de I/O Digital + FPGA), temos um ambiente completo para desenvolver, testar e simular aplicações em FPGA descritas em HDL.

Os programas são complexos e gerenciam todas as partes de um projeto em FPGA. Basicamente, podemos dividir o processo de gerar um programa em HDL com a IDE nas seguintes partes:

- Fazer a descrição do hardware em HDL ou Schematics

- Parsing e compilação do código

- Gerar bloco funcional

- Verificar restrições de tempo de propagação e freqüência máxima de operação

- Síntese de baixo nível baseado na biblioteca de blocos funcionais disponíveis

- Verificação da pinagem do circuito

- Placing e routing dos sinais (alocação física e interligação de blocos)

- Gerar fluxo de dados de programação para PROM ou para download na FPGA

Começamos nos familiarizando com o projeto e simulação com este sistema, além de nos acostumarmos com a programação em VHDL e verilog, e desenvolvendo alguns testes nos mesmos. Um ponto importante é que não é feita a melhor otimização do circuito, pois esta é uma versão gratuita do programa.

Foram realizados vários procedimentos para familiarização com estas ferramentas. Em um deles foi utilizado um pequeno código padrão em VHDL de um divisor padrão IEEE, disponível gratuitamente pela comunidade OpenCores (<http://opencores.org>), para testar o projeto na IDE (Integrated Development Environment) ISE 7.1i.

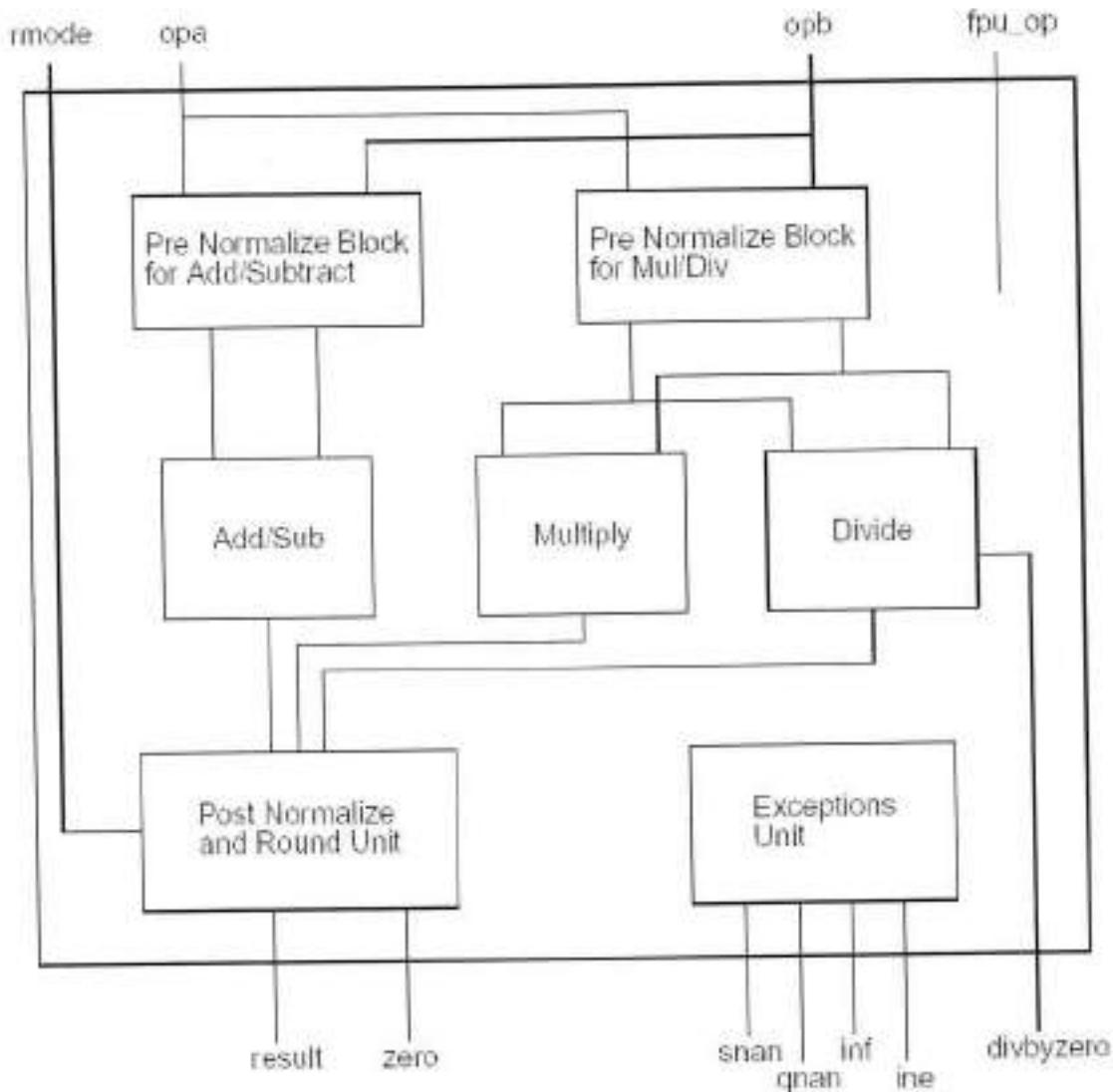

Podemos ver abaixo um diagrama genérico de blocos de um sistema divisor padrão utilizado:

Figura 12: Sistema de divisão usado para teste.

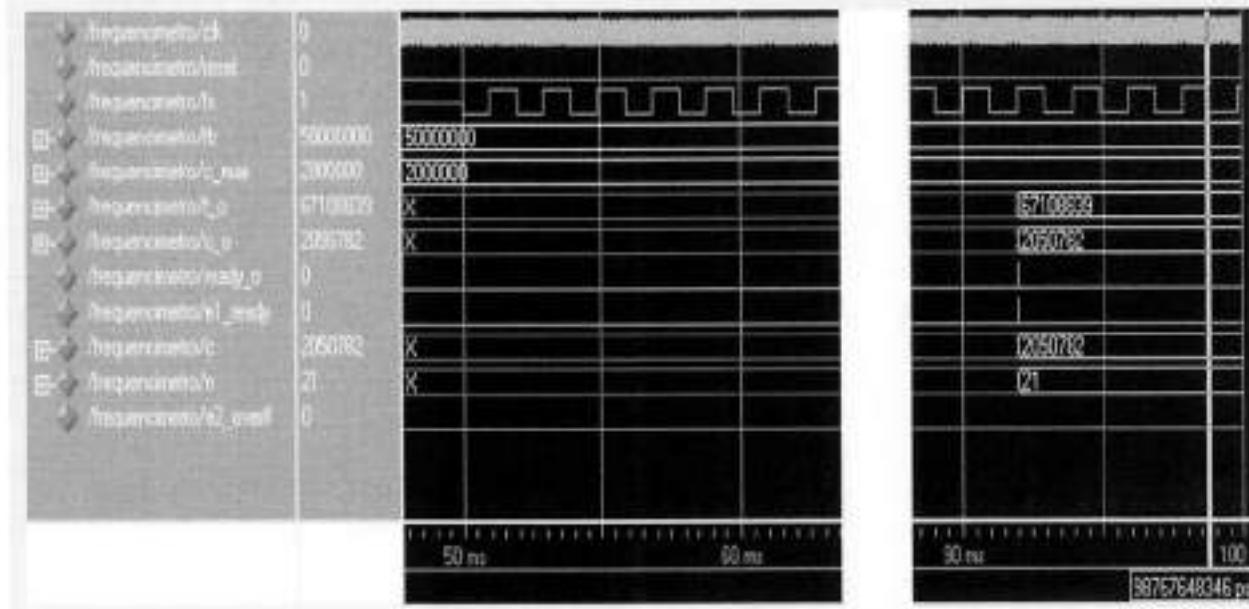

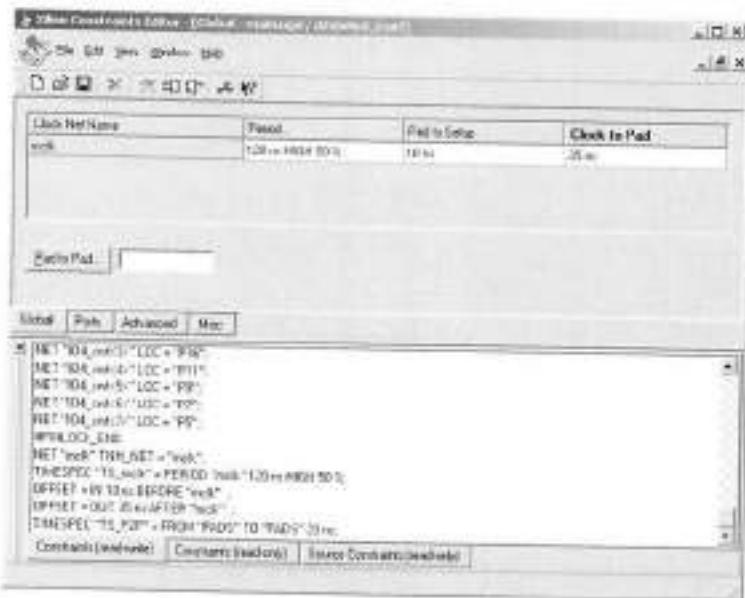

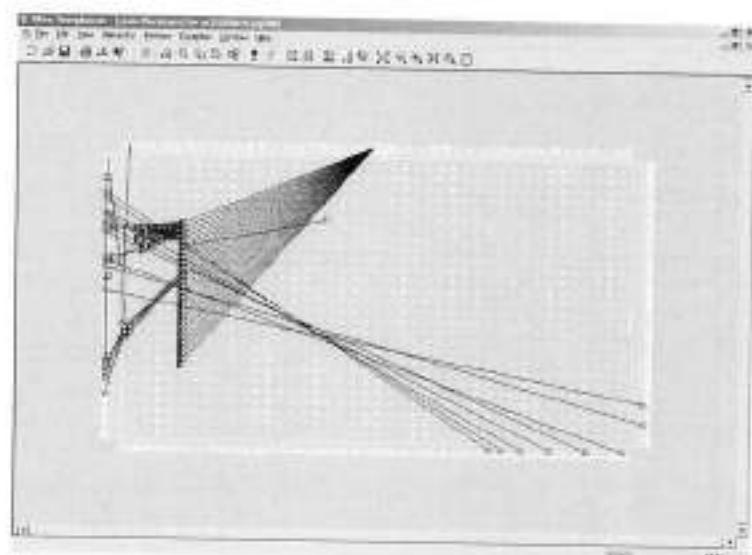

Pôde-se simular o circuito no simulador de waveform ModelSim MXE, testar o funcionamento do circuito e também se familiarizar com o uso do simulador de waveform.

Pôde-se ainda verificar no ISE restrições de projeto, ou criar restrições de tempo de alguns sinais, máxima freqüência de operação, etc, e verificar na simulação de waveform que os requisitos estão sendo atingidos, ou se necessitam de adaptações. O processo completo de teste e geração do código, desde o VHDL até a FPGA pode ser verificado no anexo 1.

## **5.2 Familiarização com a placa Digilent D2SB/DIO4**

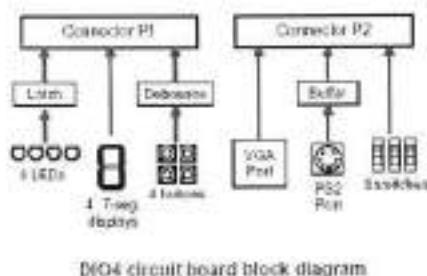

Foi utilizada uma placa de desenvolvimento para a FPGA Spartan lie, emprestada do LSI – USP. A placa contém uma FPGA e seu circuito auxiliar e uma placa de I/O Digital.

Utilizamos o ISE para baixar alguns programas para testar a placa e o funcionamento dos LEDs, display, switches push-buttons. Verificamos que felizmente a placa estava funcionando, e o sistema que faz a gravação na FPGA também funciona corretamente. Este sistema é de alta relevância, pois algo semelhante deve ser feito posteriormente para carregar o programa de uma PROM, ao invés do computador. O programa utilizado também é o ISE 7.1i, e depois de um pouco de problemas com a documentação complicada, conseguimos realizar todos os testes com sucesso.

Outro ponto é que existe uma versão Unix (Linux e Solaris) deste programa, mas ela simplesmente não funciona, apresenta várias falhas, e como possuímos licença gratuita para estudantes, não podemos contar com o suporte. Problemas semelhantes aos nossos estão abertos nos fóruns da Xilinx sem resposta há anos. Notamos uma certa falta de interesse e de usuários dessas versões, dado o número de problemas encontrados, que impossibilitaram o uso da versão

para Linux, infelizmente. Outros problemas com as licenças foram encontradas no decorrer do uso dos programas ISE e MXE, acabando por vários dias com a produtividade dos programadores deste projeto. Apesar disso, pode-se dizer que acabamos nos familiarizando com a maioria dos problemas encontrados no uso dos programas, e conseguimos evoluir com os problemas de codificação em VHDL e alguns códigos em verilog.

Rotina de testes realizada:

- **Instalação dos programas**

- **Teste do ISE 7.1i**

- **Teste do ModelSim MXE**

- **Teste de síntese e compilação de VHDL e Schematic**

- **Teste da placa principal**

- **Teste da placa de I/O Digital**

- **Teste de interação switches/push-buttons**

- **Testes no simulador de wave-form**

- **Teste de um core de FPU**

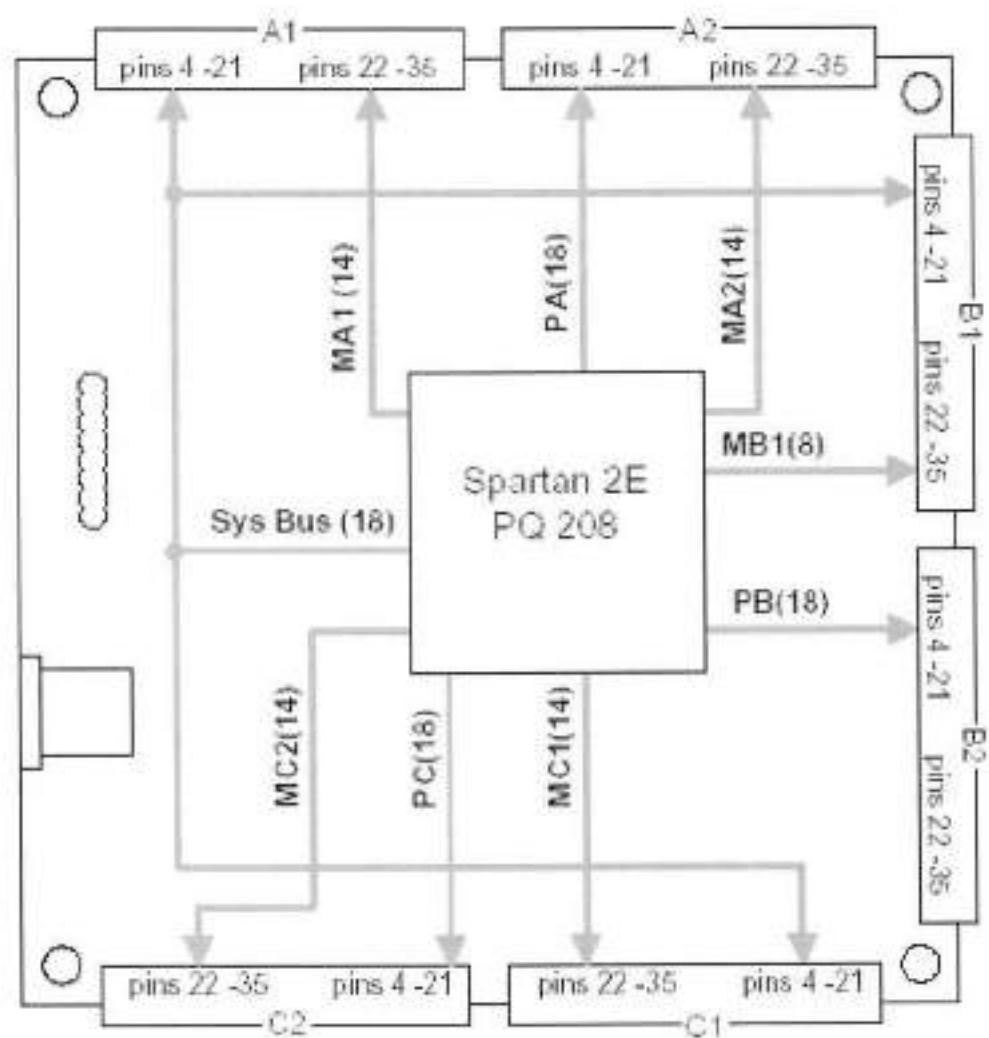

A placa digital é composta por uma parte com a FPGA e as entradas e uma placa de I/O digital. O desenho da placa é dado abaixo, junto com os I/O's digitais providos pela placa auxiliar. Os conjuntos de conectores C1 e C2 da D2SB encaixam nos conjuntos P1 e P2 da DIO.

Figure 4. Expansion Connector Signal Routing

Figura 13: Esquema das ligações da FPGA no kit de desenvolvimento.

### 5.2.1 Estudo dos algoritmos de divisão e modelos

Antes de implementar os circuitos, principalmente à parte do circuito divisor, estudamos alguns algoritmos que poderiam ser utilizados:

- **Método Simples (subtrações sucessivas);**

O método simples não tem nada de muito especial, como o próprio nome sugere. Este método consiste em se realizar subtrações sucessivas do valor do dividendo no divisor, convergindo para o resultado até esgotar o valor do divisor, e a diferença é o resto e o número de operações executadas é o quociente.

- **Divisão bit a bit;**

Este método consiste em utilizar operações bit a bit entre dividendo e divisor para calcular o resultado. A idéia é semelhante ao anterior, mas as operações são realizadas entre binários, e com isso ele é mais eficiente.

- **Método Radix 8;**

O método Radix é uma evolução do Radix 4, que é o algoritmo utilizado nas unidades aritméticas dos processadores Pentium, da Intel. É um algoritmo interativo que consiste em dividir alguns casos em que é possível extraír mais informações do que numa divisão bit a bit sem nenhuma otimização. Através das informações dos últimos restos é possível determinar casos de execução mais otimizados.

- **Divisão de ponto flutuante padrão IEEE.**

Gostaríamos de simular um divisor padrão de uma biblioteca de VHDL do IEEE, para efeitos comparativos em relação aos outros métodos, e verificar eficiência de cada um para os tipos de entrada que vamos ter no freqüencímetro. Este era um estágio para quando tivéssemos os algoritmos em simulação.

### **5.2.2 Estudo de alternativas para otimização de desempenho**

Outro ponto que é importante notar é a filosofia de implementação no hardware. Existem otimizações de projeto e construção que podem influenciar muito no desempenho do circuito.

Duas que estudamos foram o efeito dos algoritmos single clock versus multi clock (detalhados posteriormente) e da implementação dos estágios do divisor através da implementação de um Pipeline.

A implementação em Pipeline é um conceito simples, mas que otimiza o funcionamento do circuito. Basicamente a idéia do pipeline é manter o circuito ocupado o máximo possível, e para isso a informação te que se manter fluindo entre os vários estágios do circuito. Um exemplo disso seria no circuito do freqüencímetro a implementação de pipeline entre o bloco divisor e o bloco de saída usb. Um dado é calculado no divisor e imediatamente enviado para um buffer ou registrador de armazenamento. No ciclo de operações seguinte, enquanto o divisor gera outro resultado, o bloco de saída já envia o dado anterior e prepara-se

para o próximo, ou seja, não ocorre de um dado ser computado, e depois ser enviado e só então começar um novo ciclo de funcionamento. Existiam várias idéias sobre como implementar uma arquitetura pipeline no projeto, ou criar circuitos extras que ajudem no paralelismo (já que são múltiplos instrumentos enviando dados ao mesmo tempo).

Esta outra otimização também envolve diretamente a área disponível para o circuito na FPGA. Um circuito projetado de forma correta em uma simulação pode se comportar diferente quando sintetizado em uma FPGA, sujeita a restrições de área, time constraints, caminho crítico, número de entradas/saídas, etc.

### 5.2.3 Melhorias no processo de medição

Retomando os métodos de medição, não podemos utilizar simplesmente uma medida simples pelo método I, pois isso nos daria uma medida muito ruim. Precisamos levantar os parâmetros do circuito que aceitam modificações, para que possamos melhorar o desempenho.

O método I parece não poder fornecer o melhor resultado possível. Por exemplo, obviamente alguma pessoa observando a situação por 1 minuto notaria que é melhor fazer que a medição dure mais que um período.

Porém, o caso apresentado tem o seu valor, pois serve como base para discutirmos onde podemos modificar o método. Além disso, em um caso mais comum, aquele método poderia ser suficiente, e também possui um valor máximo de *throughput* de medições, e por isso devemos balancear o quanto deve ser modificado e onde para obtermos um bom resultado no final.

Como melhorar o processo de medida:

- Usar pre-scaling

Pre-scaling é uma técnica utilizada em circuitos de alta freqüência que de forma parecida pode ser útil. Não porque medimos em alta freqüência, mas sim porque o intervalo entre medições deve ser pequeno.

O pre-scaling do sinal de entrada poderia diminuir o erro relativo de +/- 1 período. É neste caso equivalente a deixar a medição por mais períodos.

- **Detecção da borda de descida**

Assumimos o erro de +/- 1 período no circuito digital, mas podemos melhorar a estimativa. Podemos também detectar a borda de descida do circuito. Com isso, a incerteza estaria confinada a +/-0.5 período. Podemos pensar que aumentamos a granularidade do circuito para metade do período (pois pela última borda podemos detectar se a medição terminou em alta ou em baixa, isso é trivial em VHDL).

- **Aumentar o clock do sistema**

Aumentar o clock garante que o período de incerteza seja cada vez menor. Apesar de altamente eficaz com 100% de certeza, é o mais delicado parâmetro a ser mexido, pois como sempre, os recursos computacionais são finitos.

Estavamos pensando em utilizar um clock de até 80MHz para o circuito. Nossa FPGA (Xilinx Spartan IIe) suporta circuitos complexos de até 300MHz. Podemos ficar muito mais próximos da margem de tolerância, e passar o circuito para 180–200MHz. Essa é uma boa freqüência porque existem OCXO's com essa freqüência que poderiam fornecer o clock do sistema. Podemos operar com um clock elevado, mesmo com um circuito complexo, desde que não se aumente muito o número de I/O's na FPGA. O desempenho se perde mais rapidamente com o número de I/O's do que com a complexidade do circuito.

Outra coisa a ser considerada é que essa FPGA é relativamente antiga. No site da Xilinx, por exemplo, só é encontrada uma versão nova dessa FPGA (a Spartan III), que deve ter

melhores recursos, que se necessário for, poderia ser utilizada. Além disso, a série Spartan é uma família “low-end” da Xilinx. Se realmente fosse muito necessário, podemos ainda passar para a família Virtex, que é a FPGA de alto desempenho da Xilinx. O ideal seria manter a Spartan IIe, pois possuímos um exemplar, para testes.

- **Uso de cristal de maior freqüência**

Como foi dito anteriormente, podemos aumentar a freqüência do clock do sistema utilizando um oscilador de maior freqüência. Estávamos planejando um oscilador impreciso comum de 20MHz (com um multiplicador de 4x) para o clock, e um sinal de OCXO preciso para medição. Podemos substituir ambos por um OCXO de valor mais alto (algo próximo de 200MHz), e existem OCXO's com essa freqüência. Isso permitiria a melhora na medição, também.

#### **5.2.4 Implementação single clock X multi clock**

Os circuitos geralmente são implementados de uma de duas formas: a single-clock e a multi-clock. O circuito single clock realiza toda a sua operação em apenas um ciclo de clock, enquanto que o multi-clock necessita de vários ciclos de operação para que a operação que ele realiza seja completada.

Cada uma das abordagens possui vantagens de desvantagens. Um circuito single clock é simples de se implementar, mas geralmente é oneroso na quantidade de portas lógicas, além de limitar o circuito a valor baixo de clock, obviamente, já que teremos mais operações sendo realizadas em um menor período de tempo.

O circuito multi-clock tem um planejamento mais complexo, e como vimos, demora vários ciclos de clock para poder dar um resultado. Isso significa esperar um tempo maior pelo

resultado, porém, podemos usar clocks mais elevados, já que esperamos operações simples a serem realizadas em cada ciclo de clock. Além disso, um sistema multi clock pode utilizar pipeline, ou seja, se for possível dividir o processo em sub-operações seqüenciais, podemos antes mesmo que um dado seja inteiramente processado, começar o processamento de outros dados, o que aumenta o throughput do sistema. Tratar de tantas variáveis tem um custo, que é a complexidade do circuito.

No nosso caso, como escolher entre a simplicidade de um circuito single clock ou projetar um multiclock? E qual funcionaria melhor? Essas questões são muito complexas. No nosso caso específico o throughput de saídas de medição não é muito elevado, porém o processamento de sinal necessita do maior clock possível, para diminuir o erro intrínseco de medição.

O cenário parece perfeito para a utilização de um circuito multi clock, porém a complexidade do circuito poderia comprometer o desempenho ou roubar muito tempo (precioso) de outras atividades. O ideal seria manter o projeto direto em single clock, e conciliar este projeto com problema de desempenho do circuito.

Felizmente isso é possível e outra idéia do prof. Wang é implementar o circuito com clocks variáveis. Assim poderíamos ter a aquisição de dados e o controle crítico de dados na maior velocidade possível e outras partes do circuito de baixo desempenho podem ter o projeto simplificado através de implementações single clock.

Isso é possível no nosso caso devido justamente à especificidade do tipo de medição. Para reduzir a significância do erro da medição necessitamos manter a contagem de medição por vários períodos de clock, e somente após todo o processo estar concluído é que processamos o resultado da aquisição. Assim, enquanto é feita uma medição temos muitos ciclos de clock ociosos que podem ser aproveitados.

Através de um divisor de freqüência podemos gerar clocks com maior período para partes específicas do circuito que não poderiam utilizar um clock de alta freqüência. Poderíamos, por exemplo, manter um divisor single clock lento, mas simples, que opera em baixa freqüência processando a última leitura enquanto se faz a aquisição da próxima.

### 5.2.5 Trade-off de desempenho

Para exemplificar o problema de desempenho do circuito que foi exposto acima, vamos mostrar uma equação que ilustra o desempenho de sistemas de arquitetura de computador CISC x RISC, que é análogo ao nosso problema de clocks e desempenho de circuito.

O problema de desempenho típico em hardware digital consiste em medir o desempenho, do circuito. Talvez uma das mais claras figuras de mérito para decidir se o circuito é bom é sua capacidade de entregar respostas rapidamente, ou seja, o chamado "throughput". O throughput é uma combinação de diversos fatores, e representa basicamente quantos programas eu consigo executar em um certo tempo.

Considerando que o tamanho do programa, ou seja, o que o circuito terá que fazer é basicamente constante, independem do método de implementação, temos que atacar a freqüência de operação do clock e o número de instruções. Como vimos, o desempenho do circuito digital está ligado à quantidade de ciclos que se pode executar, a quantidade de operações que se pode realizar em um ciclo e, claro, a quantidade de operações necessárias para que a minha tarefa (programa) seja concluída.

Não é nenhuma surpresa que nenhum desses fatores seja independente um do outro. Balancear as alterações em cada um é a chave para obter o melhor desempenho no projeto. Uma

alteração brusca em um dos quesitos pode parecer uma boa idéia, mas pode afetar bastante um outro quesito e não dar nenhum ganho de desempenho.

### 5.2.6 Montagem da placa

Pesquisamos sobre como fazer a montagem das placas. Quando se fabrica em escala, é possível realizar testes em FPGAs e então quando o projeto está maduro, gerar as máscaras e o chip ASIC para produção em larga escala. Porém, em projetos de poucas unidades isso seria custoso demais. Ao invés disso, a placa final utiliza a própria FPGA, o que se enquadra no nosso caso. Com o desempenho cada vez melhor das FPGAs isso não chega a ser um problema na maioria dos casos hoje em dia.

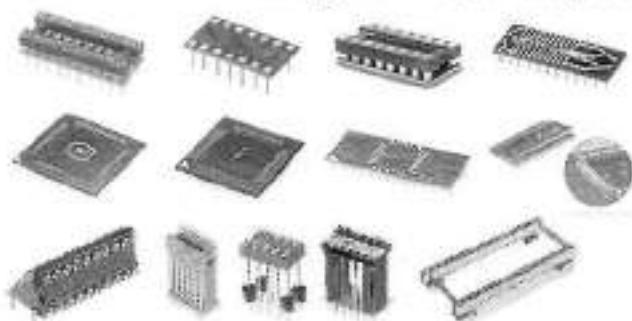

Apesar disso, um problema razoavelmente sério consistiria em como conectar a FPGA na placa, sem comprometer a FPGA em caso de um erro ou falha na placa. Isso é muito pertinente, pois uma FPGA como a nossa atual (Xilinx Spartan IIe) possui mais de 200 pinos de várias funções. Isso impossibilita a solda manual, e soquetes DIP em geral. Não seria indicado também soldar diretamente a FPGA em uma placa, pois se ela sofresse algum dano, a FPGA (que é de longe o componente mais caro na placa) ficaria inutilizada.

Uma solução encontrada foi através da empresa Aries Electronics. Esta empresa faz soquetes, adaptadores e todo tipo de encaixes, soquetes e conexões de chips de vários tipos, inclusive com projetos personalizados. Alguns dos adaptadores ajudam a resolver falhas de projeto, como a falta de espaço para um dissipador em um chip, ou um chip colocado de maneira errônea pode ter suas saídas deslocadas com um shift determinado (por exemplo, de forma que o pino 1 de saída corresponda ao pino 8 de um chip).

Este fabricante faz inclusive soquetes especiais para FPGAs, o que é extremamente interessante para o caso. Abaixo temos alguns exemplos dos produtos:

Figura 14: Exemplos de adaptadores fabricados pela Aries Eletronics.

Como será explicado em outro tópico, acabamos por decidir não fazer a manufatura da placa agora, mas em um estágio futuro do projeto. As complicações na aquisição e importação de componentes e alguns outros fatores mostraram que era preferível focar no desenvolvimento da solução agora e depois então se preocupar com a montagem da placa.

### **5.3 Desenvolvimento**

Na seção de desenvolvimento vamos retomar muitos dos tópicos já relacionados na seção de características funcionais e especificação. Além de retomar as idéias especificadas, acrescentaremos também como foi implementado cada módulo.

Figura 15: Principais módulos desenvolvidos.

### 5.3.1 Digitalizador

O sistema digitalizador, que processa o sinal de entrada da FPGA (que é também a saída do gravímetro) é implementado utilizando um CI LM 339, que é um CI que empacota comparadores baseados em Amp-Op's.

Basicamente utilizamos um dos Amp-Op's do LM339 em aberto, com uma das entradas diferenciais aterradas, e a outra é utilizada para entrada do sinal.

Figura 16: Esquema genérico da “digitalização” do sinal.

Na configuração de comparador é comum, conforme sugestão do datasheet, foi colocado um resistor próximo de 3KOHMs na saída.

Outra peculiaridade do circuito é que esses Amp-Op's não necessitam de alimentação simétrica, coisa que no nosso circuito também não é necessária. Além disso, podemos utilizar como tensão de alimentação valores que vão de 2 a 36 volts. Assim, é possível compatibilizar a saída do CI com sistemas TTL, MOS, CMOS, etc. Utilizamos uma alimentação de 3.3V. Deste modo, a saída já será compatível com o circuito LVTTL da FPGA.

Este circuito converte uma onda senoidal de amplitude 3V e offset nulo em uma onda quadrada com níveis 0V e 3.3V, ou seja, eliminando o semicírculo negativo e saturando o semicírculo positivo no valor da tensão de alimentação.

### **5.3.2 Programação da FPGA**

A FPGA é o cérebro do circuito, e onde foi colocado a maior parte do tempo de projeto. Vamos explicar mais um pouco sobre o trabalho na FPGA, e cobrir os tópicos ainda não completamente cobertos na fase de projeto citada anteriormente.

Inicialmente há uma parte introdutória sobre como foi feito o projeto e alguns instrumentos de teste. Depois entramos em alguns detalhes sobre os módulos.

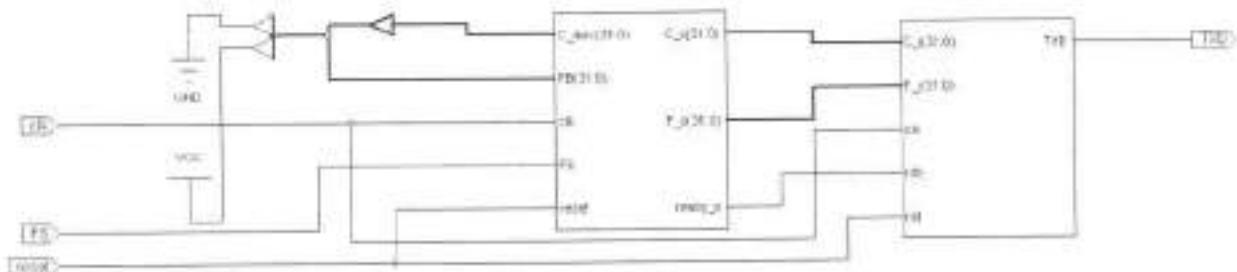

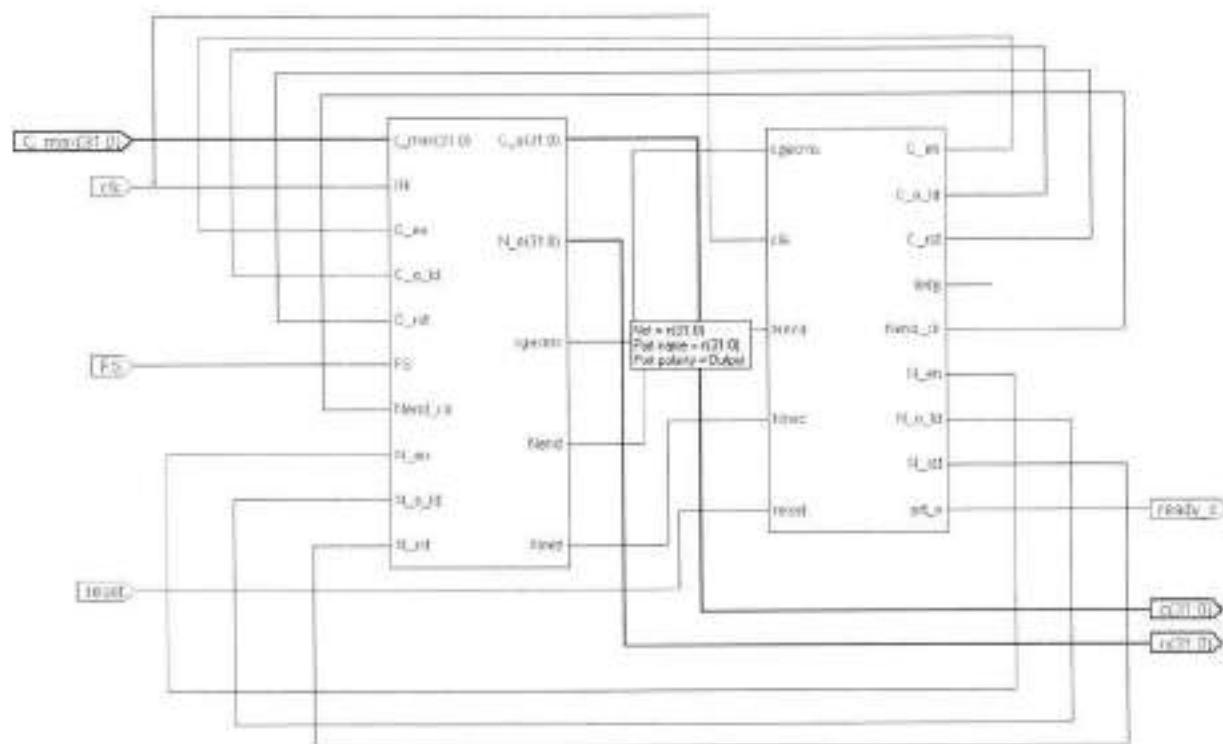

#### **5.3.2.1 A arquitetura UC/FD**

O Fluxo de Dados compreende os componentes para o processamento da informação, como, por exemplo, divisores, multiplicadores, somadores, contadores, comparadores etc, bem como de blocos de memória (registradores) e roteamento (multiplexadores), que serão descritos

em primitivas básicas do chip em questão, através de bibliotecas específicas que o fabricante mantém no ambiente de programação para sua linha de produtos. A síntese e simulação pode ser feita com elementos genéricos, mas a pós síntese as próximas fases devem ser implementadas com as bibliotecas do componente, para que sejam computados parâmetros de desempenho, restrições de tempo de execução, quantidade de sinais, pinagem, etc.

Optamos por implementar em VHDL cada componente separadamente e interconectá-los na descrição estrutural (poderiam ser utilizadas outras descrições), que compõem o Fluxo de Dados. Podemos facilmente detectar erros de design ou programação e temos uma descrição "limpa" do funcionamento. Podemos posteriormente realizar otimizações em diversos estágios da programação para deixar o circuito mais eficiente.

Já a Unidade de Controle, que implementa a máquina de estados do algoritmo, é responsável por gerenciar os dados que estão sendo processados na FD através da troca de sinais de controle e de saída com FC. A UC deve enviar sinais para seleção de entrada, reiniciar processo, enviar saídas, carregar dados, etc. A FD envia sinais de status para a UC, tais como a saída do processamento, que indica que a UC já pode ordenar o processamento de novos dados.