UNIVERSIDADE DE SÃO PAULO – USP

ESCOLA DE ENGENHARIA DE SÃO CARLOS

DEPARTAMENTO DE ENGENHARIA ELÉTRICA E DE

COMPUTAÇÃO

PROJETO FINAL DE CURSO

ESTUDO DE DRIVERS PARA MOSFETS DE

POTÊNCIA DE TECNOLOGIA SIC

Autor: Gabriel Biller Giareta

Orientador: Prof. Dr. Augusto Matheus dos Santos Alonso

São Carlos

2025

AUTORIZO A REPRODUÇÃO TOTAL OU PARCIAL DESTE TRABALHO,

POR QUALQUER MEIO CONVENCIONAL OU ELETRÔNICO, PARA FINS

DE ESTUDO E PESQUISA, DESDE QUE CITADA A FONTE.

Ficha catalográfica elaborada pela Biblioteca Prof. Dr. Sérgio Rodrigues Fontes da

EESC/USP com os dados inseridos pelo(a) autor(a).

G435e Giareta, Gabriel Biller

Estudo de drivers para MOSFETs de potência de

tecnologia Si / Gabriel Biller Giareta; orientador

Augusto Matheus dos Santos Alonso. São Carlos, 2025.

Monografia (Graduação em Engenharia Elétrica com

ênfase em Eletrônica) -- Escola de Engenharia de São

Carlos da Universidade de São Paulo, 2025.

1. MOSFET SiC. 2. Gate driver. 3. Eletrônica de

potência. 4. Wide bandgap. I. Título.

# FOLHA DE APROVAÇÃO

Nome: Gabriel Biller Giareta

Título: "Estudo de Drivers para Mosfets de Potência de Tecnologia SIC"

Trabalho de Conclusão de Curso defendido e aprovado

em 26/06/2025,

com NOTA 8,0 (oito, ), pela Comissão

Julgadora:

Prof. Dr. Augusto Matheus dos Santos Alonso - Orientador

SEL/EESC/USP

Mestre Lucas Jonys Ribeiro Silva - Doutorando -

SEL/EESC/USP

Prof. Dr. Marcos Rogério Fernandes - SEL/EESC/USP

Coordenador da CoC-Engenharia Elétrica - EESC/USP:

Professor Associado José Carlos de Melo Vieira Júnior

## RESUMO

Com a crescente demanda por equipamentos com maiores densidade de potência, eficiência energética e confiabilidade, surge a necessidade de dispositivos eletrônicos com maiores capacidades de potência, frequência e temperatura do que o silício (Si). Por causa de suas características elétricas e térmicas, transístores de materiais como carbeto de silício (SiC) e nitreto de gálio (GaN) preenchem esses requisitos. MOSFETs SiC são ideais para aplicações de média e alta potência, no entanto os maiores transientes atingidos exigem um maior cuidado para o chaveamento desses transístores. Este trabalho apresenta uma análise sobre o MOSFET SiC e seus *gate drivers*, passando pelas características que motivam o uso de técnicas mais avançadas de chaveamento e também estudando essas técnicas. São realizados levantamentos bibliográficos da literatura e do mercado sobre técnicas e topologias de *gate drivers* para MOSFETs SiC, e por fim sendo simulados computacionalmente alguns dos circuitos que empregam essas técnicas, tendo seus resultados em testes de duplo-pulso comparados a um *gate driver* convencional. Os *gate drivers* ativos apresentaram menores sobressinais de tensão e corrente, menores atrasos de chaveamento e menor *crosstalk*.

**Palavras-chave:** *wide bandgap*, MOSFET SiC, *gate driver*, eletrônica de potência.

## ABSTRACT

With the increasing demand for hardware with higher power density, energy efficiency and reliability, there comes a need for electronic devices with greater power, frequency and temperature capabilities than silicon (Si). Because of their electrical and thermal properties, transistors made from materials such as silicon carbide (SiC) and gallium nitride (GaN) meet these requirements. SiC MOSFETs are ideal for medium- and high-power applications, however the higher transients they produce require greater care in their switching. This work presents an analysis of SiC MOSFETs and their *gate drivers*, covering the characteristics that motivate the use of more advanced switching techniques and studying these techniques as well. A literature and market review is conducted on techniques and topologies of *gate drivers* for SiC MOSFETs, and at last some of the circuits employing these techniques are simulated computationally, with their results in double-pulse tests compared to those of a conventional *gate driver*. The active *gate drivers* exhibited lower voltage and current overshoots, shorter switching delays, and reduced crosstalk.

**Keywords:** wide bandgap, SiC MOSFET, gate driver, power electronics.

## Sumário

|         |                                                                             |    |

|---------|-----------------------------------------------------------------------------|----|

| 1       | <b>Introdução</b> . . . . .                                                 | 12 |

| 1.1     | <i>Vantagens técnicas e aplicações de tecnologias WBG</i> . . . . .         | 12 |

| 1.2     | <i>Objetivos</i> . . . . .                                                  | 14 |

| 2       | <b>Características e <i>Gate Drivers</i> de MOSFETs SiC</b> . . . . .       | 15 |

| 2.1     | <i>Características de operação de MOSFETs SiC</i> . . . . .                 | 15 |

| 2.1.1   | Propriedades de condução . . . . .                                          | 15 |

| 2.1.2   | Propriedades parasitas . . . . .                                            | 16 |

| 2.1.3   | Propriedades térmicas . . . . .                                             | 18 |

| 2.1.4   | Propriedades de chaveamento . . . . .                                       | 19 |

| 2.2     | <i>Características de gate drivers para MOSFETs SiC</i> . . . . .           | 20 |

| 2.2.1   | Métodos de controle de potência no <i>gate</i> . . . . .                    | 20 |

| 2.2.1.1 | Controle direto da potência . . . . .                                       | 21 |

| 2.2.1.2 | Controle indireto da potência . . . . .                                     | 22 |

| 2.2.2   | Estratégias para controle de potência no <i>gate</i> . . . . .              | 22 |

| 2.2.2.1 | Técnicas de malha aberta . . . . .                                          | 23 |

| 2.2.2.2 | Técnicas de malha fechada . . . . .                                         | 23 |

| 2.2.3   | Técnicas de proteção . . . . .                                              | 23 |

| 2.2.3.1 | Proteção de sobrecorrente e curto-circuito . . . . .                        | 23 |

| 2.2.3.2 | Proteção de baixa tensão de <i>gate</i> - UVLO . . . . .                    | 24 |

| 2.2.3.3 | Proteção de <i>crosstalk</i> . . . . .                                      | 25 |

| 3       | <b>Análise Bibliográfica de Topologias de <i>Gate Drivers</i></b> . . . . . | 26 |

| 3.1     | <i>Topologias de gate drivers na literatura</i> . . . . .                   | 26 |

| 3.1.1   | Tensão variável . . . . .                                                   | 26 |

| 3.1.2   | Resistência variável . . . . .                                              | 29 |

| 3.2     | <i>Topologias de gate drivers no mercado</i> . . . . .                      | 32 |

| 3.2.1   | <i>Gate drivers da Infineon Technologies</i> . . . . .                      | 33 |

| 3.2.2   | <i>Gate drivers da Texas Instruments</i> . . . . .                          | 34 |

| 3.3     | <i>Discussão</i> . . . . .                                                  | 35 |

| 4       | <b>Análise Computacional de Topologias de <i>Gate Drivers</i></b> . . . . . | 36 |

| 4.1     | <i>Metodologia</i> . . . . .                                                | 36 |

| 4.1.1   | <i>Hardware</i> . . . . .                                                   | 37 |

| 4.1.1.1 | Tensão variável . . . . .                                                   | 37 |

| 4.1.1.2 | Resistência variável . . . . .                                              | 38 |

| 4.1.1.3 | <i>Gate driver convencional</i> . . . . .                                   | 40 |

|            |                            |    |

|------------|----------------------------|----|

| <i>4.2</i> | <i>Resultados</i>          | 40 |

| 4.2.1      | Desempenho no acionamento  | 43 |

| 4.2.2      | Desempenho no desligamento | 45 |

| 4.2.3      | <i>Crosstalk</i>           | 47 |

| <i>4.3</i> | <i>Discussão</i>           | 49 |

| 5          | Conclusão                  | 50 |

| 6          | Referências                | 52 |

## Lista de ilustrações

|                                                                                                                                                                                            |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figura 1 – Nichos de aplicação de dispositivos semicondutores de potência [23]. . . . .                                                                                                    | 13 |

| Figura 2 – Comparação de corrente de <i>drain</i> ( $I_d$ ) por tensão $V_{gs}$ entre um MOSFET SiC e um IGBT Si (ROHM Semiconductor) [12]. . . . .                                        | 16 |

| Figura 3 – MOSFET SiC e seus elementos parasitas. . . . .                                                                                                                                  | 17 |

| Figura 4 – Ciclo de chaveamento do MOSFET SiC. Modificado de [24]. . . . .                                                                                                                 | 19 |

| Figura 5 – Diagrama de blocos simplificado de um <i>gate driver</i> de topologia convencional [26]. . . . .                                                                                | 21 |

| Figura 6 – Diagrama de blocos simplificado de um <i>gate driver</i> de topologia de resistência variável [25]. . . . .                                                                     | 21 |

| Figura 7 – Estratégias para controle de potência no <i>gate</i> : malha aberta (esquerda) e malha fechada (direita) [25]. . . . .                                                          | 22 |

| Figura 8 – Métodos de proteção de curto-circuito: DESAT (esquerda) [28], <i>shunt</i> (centro) [28] e por indutância parasita de <i>source</i> com terminal Kelvin (direita) [27]. . . . . | 24 |

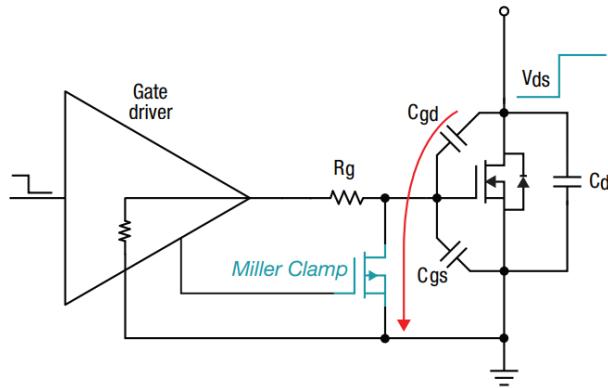

| Figura 9 – Diagrama de blocos de um <i>gate driver</i> com <i>Miller clamp</i> [23]. . . . .                                                                                               | 25 |

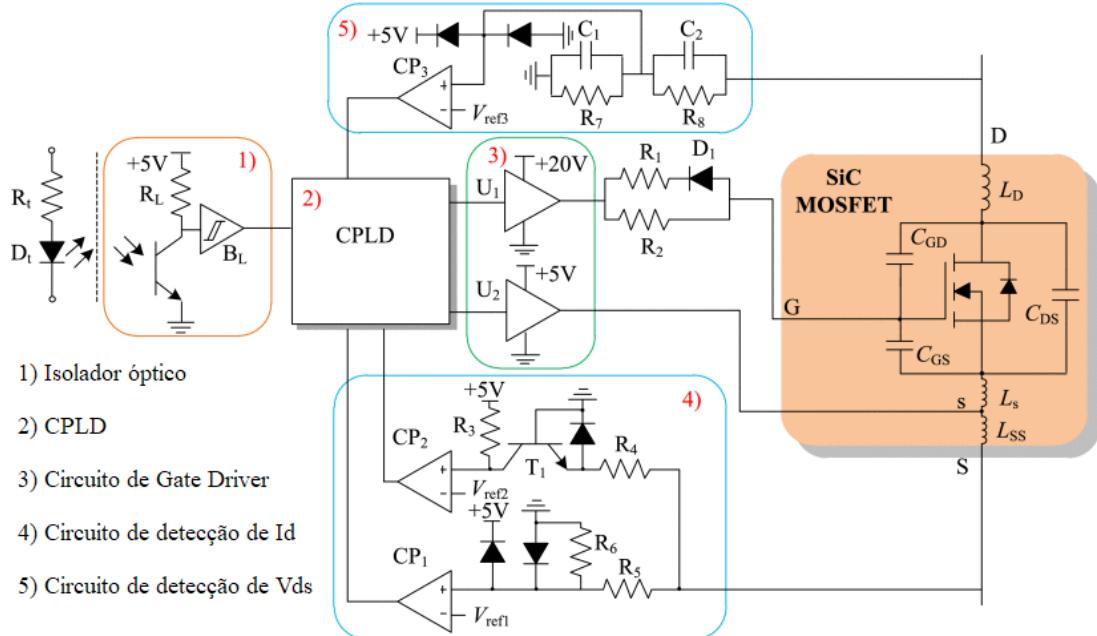

| Figura 10 – Diagrama de blocos do AGD de tensão variável [13]. . . . .                                                                                                                     | 26 |

| Figura 11 – Modos de operação do AGD de tensão variável no acionamento. (a) $V_{gs} = 20V$ (b) $V_{gs} = 15V$ [13]. . . . .                                                                | 27 |

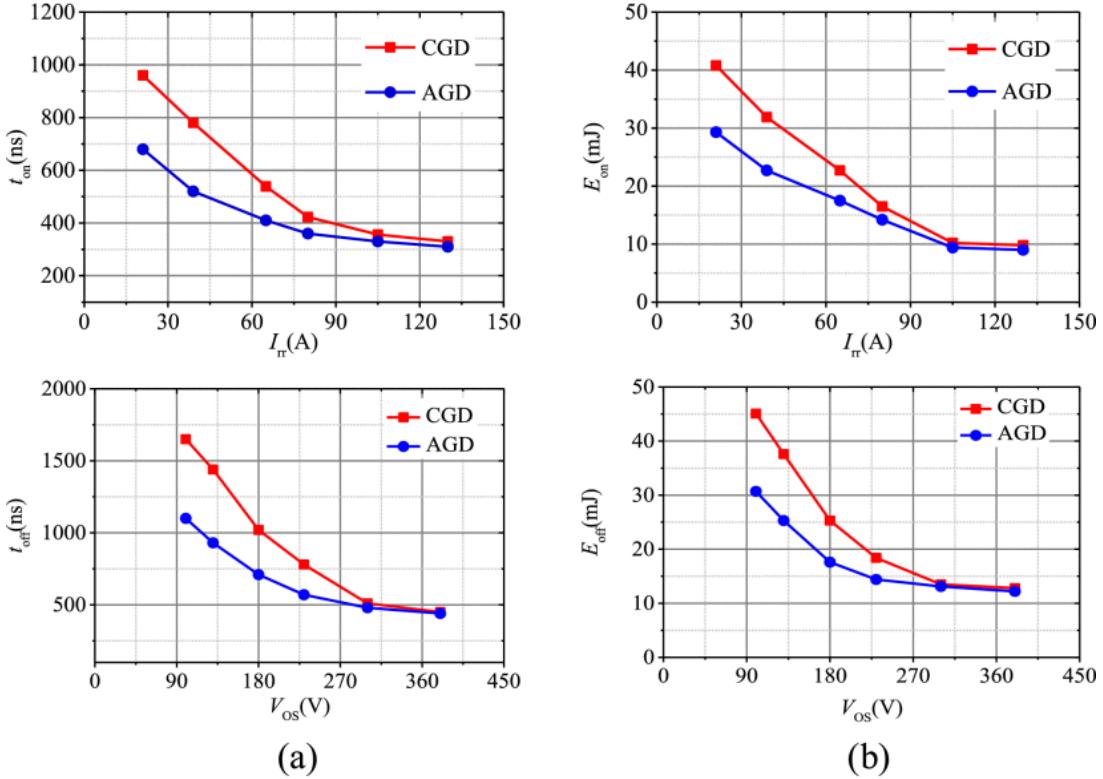

| Figura 12 – Análise de (a) tempo e (b) perdas de chaveamento em função do sobressinal de $I_d$ (acima) ou de $V_{ds}$ (abaixo) no AGD de tensão variável [13]. . . . .                     | 28 |

| Figura 13 – Diagrama de blocos do AGD de resistência variável [14]. . . . .                                                                                                                | 29 |

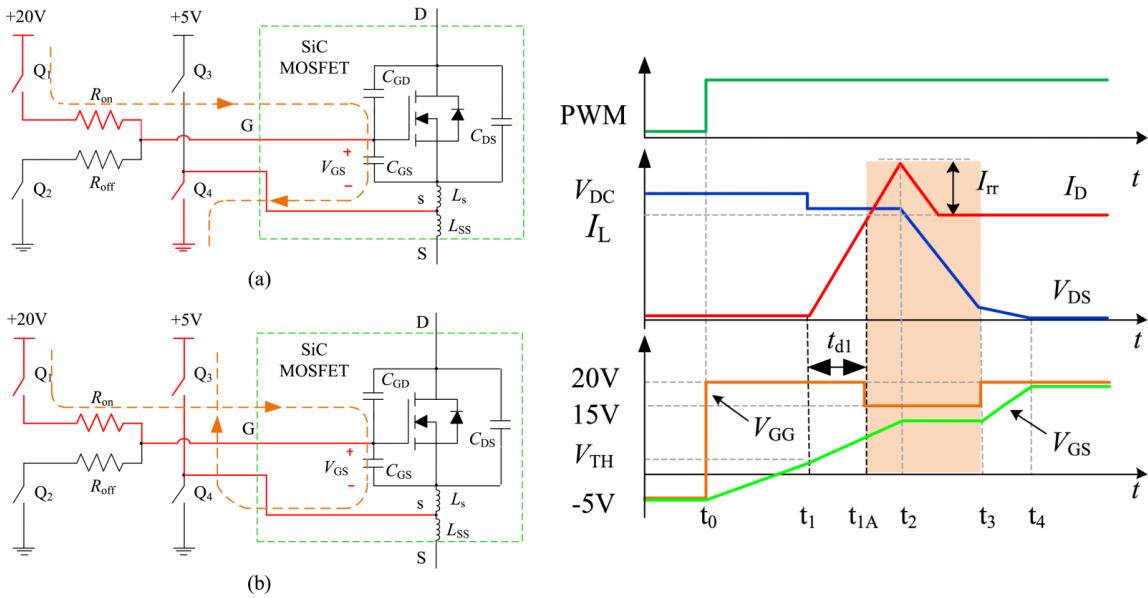

| Figura 14 – Modos de operação do AGD de resistência variável [14]. . . . .                                                                                                                 | 30 |

| Figura 15 – Formas de onda para acionamento (esquerda) e desligamento (direita) para (a) CGD e (b) AGD de resistência variável [14]. . . . .                                               | 31 |

| Figura 16 – <i>Gate drivers</i> modulares dos fabricantes Microchip [15] (esquerda) e Toshiba [16] (direita). . . . .                                                                      | 32 |

| Figura 17 – Diagrama de blocos do <i>driver</i> 1ED3241MC12H, da família 2L-SRC da Infineon [18]. . . . .                                                                                  | 33 |

| Figura 18 – Esquemático simplificado do <i>driver</i> UCC5881-Q1, da Texas Instruments [19]. . . . .                                                                                       | 34 |

| Figura 19 – Circuito de simulação da topologia de tensão variável. . . . .                                                                                                                 | 38 |

| Figura 20 – Circuito de simulação da topologia de resistência variável. . . . .                                                                                                            | 39 |

| Figura 21 – Circuito de simulação da topologia convencional. . . . .                                                                                                                       | 40 |

|                                                                                                                                                                                                                                                                                                                                                                                               |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figura 22 – Formas de ondas no acionamento de $V_{gs}$ , $I_g$ , $V_{ds}$ e $I_d$ (cima para baixo) para os AGDs de tensão variável (verde) e resistência variável (azul). $R_g = 10\Omega$ e $L_{loop} = 100nH$ . . . . .                                                                                                                                                                    | 41 |

| Figura 23 – Formas de ondas no desligamento de $V_{gs}$ , $I_g$ , $V_{ds}$ e $I_d$ (cima para baixo) para os AGDs de tensão variável (verde) e resistência variável (azul). $R_g = 10\Omega$ e $L_{loop} = 100nH$ . . . . .                                                                                                                                                                   | 42 |

| Figura 24 – Formas de ondas de $V_{gs}$ , $I_g$ , $V_{ds}$ e $I_d$ (cima para baixo) para o CGD. Esquerda: acionamento. Direita: desligamento. $R_{g,vvar} = 10\Omega$ e $L_{loop} = 100nH$ . . . . .                                                                                                                                                                                         | 43 |

| Figura 25 – Formas de ondas de $I_d$ e $V_{ds}$ no acionamento para o AGDs de tensão variável (verde), de resistência variável (azul) e o CGD (vermelho). MOSFET <i>NXP</i> : a) $R_g = 10\Omega$ e $L_{loop} = 100nH$ . b) $R_g = 7.5\Omega$ e $L_{loop} = 100nH$ . c) $R_g = 10\Omega$ e $L_{loop} = 300nH$ . MOSFET <i>Microchip</i> : d) $R_g = 10\Omega$ e $L_{loop} = 100nH$ . . . . .  | 44 |

| Figura 26 – Formas de ondas de $I_d$ e $V_{ds}$ no desligamento para o AGDs de tensão variável (verde), de resistência variável (azul) e o CGD (vermelho). MOSFET <i>NXP</i> : a) $R_g = 10\Omega$ e $L_{loop} = 100nH$ . b) $R_g = 7.5\Omega$ e $L_{loop} = 100nH$ . c) $R_g = 10\Omega$ e $L_{loop} = 300nH$ . d) MOSFET <i>Microchip</i> : $R_g = 10\Omega$ e $L_{loop} = 100nH$ . . . . . | 46 |

| Figura 27 – <i>Crosstalk</i> ( $V_{gs}$ no MOSFET de alta) no acionamento (acima) e desligamento (abaixo) do MOSFET de baixa para o AGD de tensão de variável (verde), de resistência variável (azul) e o CGD (vermelho) nos testes a) e d). . . . .                                                                                                                                          | 48 |

## **Lista de tabelas**

|                                                                                                   |    |

|---------------------------------------------------------------------------------------------------|----|

| Tabela 1 – Comparaçāo entre as propriedades elētricas dos semicondutores (Si x SiC) [12]. . . . . | 15 |

| Tabela 2 – Desempenho das topologias no acionamento. . . . .                                      | 43 |

| Tabela 3 – Desempenho das topologias no desligamento. . . . .                                     | 45 |

| Tabela 4 – <i>Crosstalk</i> relativo das topologias. . . . .                                      | 47 |

## Lista de abreviaturas e siglas

|             |                                                                 |

|-------------|-----------------------------------------------------------------|

| Si          | Silício                                                         |

| SiC         | Carbeto de silício                                              |

| GaN         | Nitreto de gálio                                                |

| MOSFET      | Transístor de efeito de campo de semicondutor de óxido metálico |

| IGBT        | Transístor bipolar de <i>gate</i> insulado                      |

| BJT         | Transístor bipolar de junção                                    |

| WBG         | <i>Wide bandgap</i>                                             |

| PCI         | Placa de circuito impresso                                      |

| CGD         | <i>Gate driver</i> convencional                                 |

| AGD         | <i>Gate driver</i> ativo                                        |

| IEM         | Interferência eletromagnética                                   |

| CI          | Circuito integrado                                              |

| UVLO        | Proteção de baixa tensão de <i>gate</i>                         |

| SCWT        | Duração máxima de curto-circuito                                |

| CPLD        | Dispositivo lógico complexo programável                         |

| PWM         | Modulação por largura de pulso                                  |

| $V_{gs}$    | Tensão <i>gate-source</i>                                       |

| $V_{gs,h}$  | Tensão <i>gate-source</i> do MOSFET complementar                |

| $V_{gs,th}$ | Tensão limiar de ativação                                       |

| $V_{ds}$    | Tensão <i>drain-source</i>                                      |

| $V_{ce}$    | Tensão coletor-emissor                                          |

| $I_c$       | Corrente de coletor                                             |

| $I_d$       | Corrente de <i>drain</i>                                        |

|              |                                                      |

|--------------|------------------------------------------------------|

| $I_g$        | Corrente de <i>gate</i>                              |

| $dv/dt$      | Gradiente de tensão                                  |

| $di/dt$      | Gradiente de corrente                                |

| $C_{gd}$     | Capacitância <i>gate-drain</i>                       |

| $C_{gs}$     | Capacitância <i>gate-source</i>                      |

| $C_{ds}$     | Capacitância <i>drain-source</i>                     |

| $C_{iss}$    | Capacitância de entrada                              |

| $C_{oss}$    | Capacitância de saída                                |

| $Q_g$        | Carga de <i>gate</i>                                 |

| $R_{ds, on}$ | Resistência <i>drain-source</i> de condução          |

| $R_g$        | Resistência de <i>gate</i>                           |

| $R_g, h$     | Resistência de <i>gate</i> do MOSFET complementar    |

| $R_g, on$    | Resistência de <i>gate</i> de acionamento            |

| $R_g, off$   | Resistência de <i>gate</i> de desligamento           |

| $R_g, vvar$  | Resistência de <i>gate</i> do AGD de tensão variável |

| $R_{shunt}$  | Resistência <i>shunt</i>                             |

| $L_s$        | Indutância de <i>source</i>                          |

| $L_{loop}$   | Indutância parasita da malha de potência             |

## 1 Introdução

Eletrônica de potência é a área de conhecimento relacionada ao uso de dispositivos eletrônicos para controlar, converter e condicionar potência elétrica, almejando-se maior eficiência, maior confiabilidade e maior disponibilidade sob menores custos, pesos e tamanhos.

Ao longo das décadas, várias tecnologias de eletrônica de potência foram desenvolvidas e aplicadas nas mais diversas situações. Com a revolução dos materiais semicondutores, tornaram-se de grande destaque os dispositivos de silício (Si), sobretudo os transístores, que são capazes de chavear uma grande potência a partir de um baixo sinal de entrada.

Por possuírem alta impedância de entrada, transístores do tipo MOSFET (transistor de efeito de campo de semicondutor de óxido metálico), surgidos na década de 50, necessitam de pouca potência de entrada para serem ativados, tornando-os os transístores mais eficientes. Porém, eles apresentam baixa densidade de potência, fazendo com que possuam custos mais elevados para aplicações de alta demanda. Assim, MOSFETs Si dominam há muito tempo o mercado de aplicações de baixa e média potência [30].

Transístores do tipo IGBT (transistor bipolar de *gate* insulado), introduzidos na década de 80, unem a alta impedância de entrada dos MOSFETs à maior capacidade de corrente dos BJTs (transistor bipolar de junção). No entanto, sua limitação encontra-se na maior carga necessária para sua ativação, fazendo com que o dispositivo suporte menores frequências de chaveamento e tornando-o menos eficiente para baixas e médias potências. Devido a essas características, IGBTs Si dominam o mercado de alta potência [30].

Com a crescente demanda por eletrificação em aplicações do dia-a-dia, como veículos elétricos, eletrodomésticos e conversores de energia alternativa, equipamentos com maiores densidade de potência, eficiência energética e confiabilidade a partir de um baixo custo tornam-se ainda mais urgentes. Assim, surge a necessidade de dispositivos eletrônicos com maiores capacidades de potência, frequência e temperatura do que o silício.

Materiais de *wide bandgap* (WBG), como carbeto de silício (SiC) e nitreto de gálio (GaN), possuem vantagens substanciais em relação ao Si devido às suas propriedades físicas inerentes [31], preenchendo esses requisitos. No entanto, apesar das vantagens técnicas, há também novos desafios que surgem com aplicações mais exigentes. Transientes e temperaturas mais severos requerem maior controle e proteção dos dispositivos, como *gate drivers* mais avançados e placas de circuito impresso (PCI) mais otimizadas.

### 1.1 Vantagens técnicas e aplicações de tecnologias WBG

Materiais WBG possuem naturalmente uma maior tensão de ruptura, fazendo então com que maiores níveis de dopagem possam ser atingidos e os dispositivos possuam cama-

das mais finas [29]. Isso permite aos dispositivos WBG obterem maiores velocidades de deriva, fazendo com que eles possam ser chaveados a frequências maiores do que materiais de Si.

Embora materiais WBG possuam características gerais superiores ao Si, cada um deles possui propriedades distintas que precisam ser consideradas em suas respectivas aplicações. Transístores GaN possuem as melhores características elétricas, como maior frequência de operação, maior velocidade de comutação e menor resistência de condução, porém possuem propriedades térmicas inferiores ao Si, fazendo com que não sejam adequados para aplicações de alta potência [31]. Por outro lado, a tecnologia SiC possui a melhor condutividade térmica, e somando isso às suas propriedades elétricas superiores às do Si [12] e sua maior disponibilidade no mercado em relação a transístores GaN, os transístores SiC tornam-se a escolha ideal para aplicações de alta demanda energética e alta eficiência.

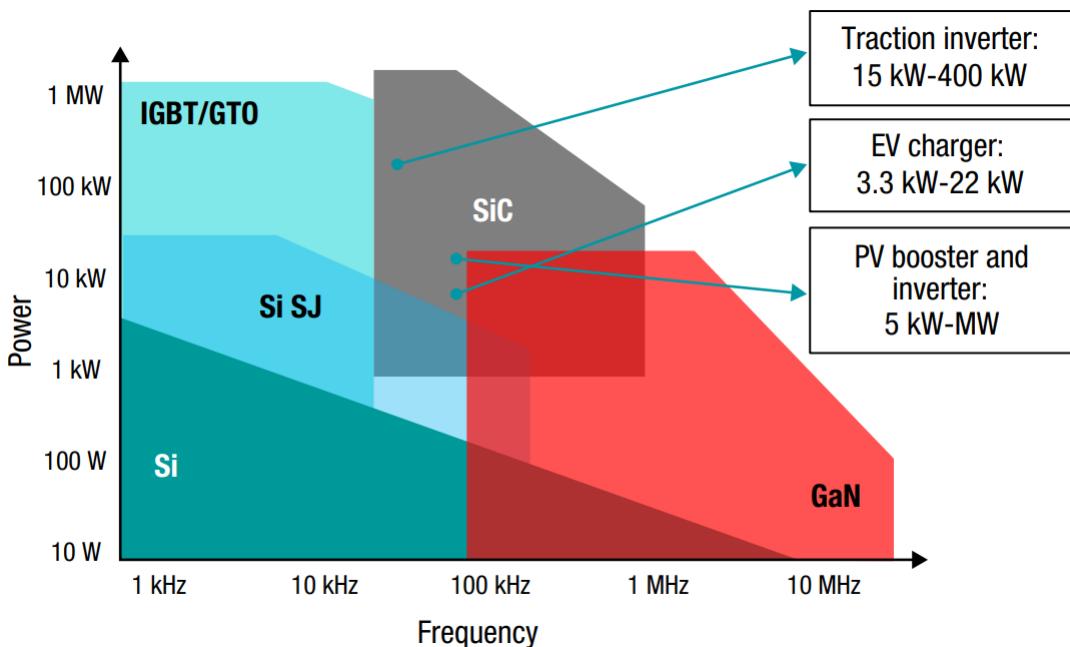

Transístores SiC, em especial MOSFETs, ocupam atualmente os nichos de média e alta potência ( $>3\text{kW}$ ), alta frequência ( $>40\text{kHz}$ ) e alta temperatura, que é preenchido majoritariamente por drivers para motores industriais e automotivos [1], inversores de energia renovável [2]-[5], carregadores de baterias para veículos elétricos e híbridos [6], fontes de potência industriais [7] e aquecedores por indução [8]. Na figura 1 são apresentados os nichos de aplicação de transístores SiC, por potência e frequência.

Figura 1 – Nichos de aplicação de dispositivos semicondutores de potência [23].

MOSFETs SiC hoje são considerados a melhor opção para aplicações de potência de até 10kV [9]. Dispositivos bipolares SiC, no entanto, sofrem de altas perdas de condução

devido à alta tensão da junção PN ( $>2V$ ) e problemas de degradação da junção PN devido a altas temperaturas [9], porém desenvolvimentos recentes alegam ter resolvido o problema da degradação, fazendo com que bipolares SiC se tornem um possível interesse futuro para aplicações de alta tensão ( $>10kV$ ) [10].

Dentre os possíveis caminhos de projeto, o de alta eficiência é o mais buscado atualmente para transístores SiC. Em seguida, projetos mais alinhados a alta frequência de comutação permitem maior densidade de potência, sendo úteis para aplicações mais compactas. Por fim, projetos voltados a alta temperatura encontram seus nichos primariamente em aplicações automotivas e aeroespaciais [11].

## 1.2 *Objetivos*

Considerando o que foi mencionado anteriormente, este trabalho tem interesse na problemática do uso de transístores SiC em aplicações de alta potência e frequência, tendo foco no estudo de *gate drivers* para MOSFETs SiC e suas topologias específicas.

Assim, serão realizados estudos bibliográficos detalhados sobre as características da tecnologia SiC e as motivações que levam ao uso de drivers especiais, assim como serão avaliadas as topologias já consolidadas na academia e no mercado.

## 2 Características e *Gate Drivers* de MOSFETs SiC

Neste capítulo será introduzido o MOSFET SiC e suas características especiais, que o levam a necessitar de técnicas mais avançadas para que seu chaveamento seja realizado adequadamente. *Gate drivers* que aplicam essas técnicas apresentam melhores desempenhos de chaveamento em conjunto com melhor segurança e confiabilidade, os quais também serão vistos aqui.

### 2.1 Características de operação de MOSFETs SiC

Eficiência de condução, eficiência de chaveamento, tensão de ruptura, tamanho e custo são as características mais importantes para transístores empregados em conversores de potência. Essas características são relacionadas com as propriedades elétricas da tecnologia e do material semicondutor. Na tabela 1 são comparados os parâmetros elétricos do Si e do SiC.

Tabela 1 – Comparaçāo entre as propriedades elétricas dos semicondutores (Si x SiC) [12].

| Parāmetro                         | Unidade                | Si   | SiC  | Característica                                          |

|-----------------------------------|------------------------|------|------|---------------------------------------------------------|

| Energia de largura de banda       | eV                     | 1.12 | 3.26 | Maior temperatura de junção / menor corrente de fuga    |

| Mobilidade de elétrons            | cm <sup>2</sup> /V.s   | 1400 | 900  | Maior frequência / velocidade de chaveamento            |

| Campo de ruptura                  | V/cm x 10 <sup>6</sup> | 0.3  | 3    | Maior tensão de ruptura / menor resistência de condução |

| Velocidade de deriva de saturação | cm/s x 10 <sup>7</sup> | 1    | 2.7  | Maior frequência / velocidade de chaveamento            |

| Condutividade térmica             | W/cm.K                 | 1.5  | 4.9  | Melhor operação em altas temperaturas                   |

#### 2.1.1 Propriedades de condução

Como pode ser visto na tabela anterior, o SiC é superior ao Si em praticamente todas as propriedades, com exceção da mobilidade de elétrons. De fato, na tecnologia atual o Si consegue acelerar elétrons a uma velocidade maior do que o SiC, ambos a um mesmo campo elétrico. Porém, como o SiC suporta campos elétricos até 10 vezes maiores do que o Si, a resistência de condução ( $R_{ds,on}$ ) por unidade de área pode ser muito menor no SiC, permitindo dispositivos capazes de atingir maiores frequências de chaveamento com menores perdas de condução.

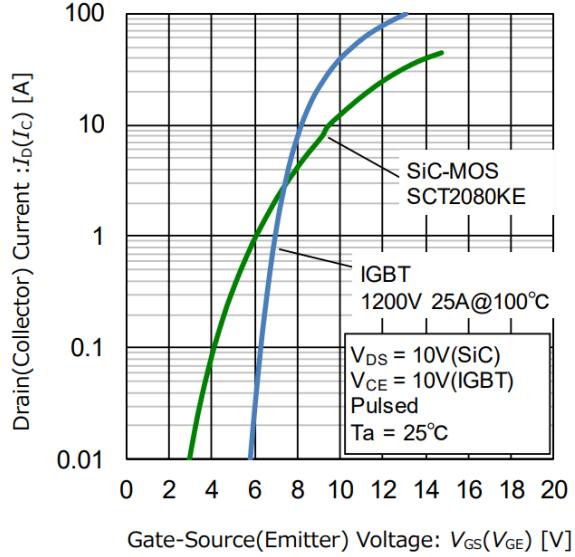

No entanto, as vantagens possuem seu custo. MOSFETs SiC possuem baixa transcondutância, fazendo com que eles necessitem de maior tensão *gate-source* ( $V_{gs}$ ) para que atinjam a saturação, que ocorre por volta dos 15V a 20V. Em contraponto, o Si já atinge

saturação entre os 8V a 10V, fazendo com que dispositivos SiC necessitem de *drivers* específicos, mesmo comparados a IGBTs Si (figura 2).

Figura 2 – Comparaçāo de corrente de *drain* ( $I_d$ ) por tensāo  $V_{gs}$  entre um MOSFET SiC e um IGBT Si (ROHM Semiconductor) [12].

Ao mesmo tempo, a tensāo limiar de ativaçāo ( $V_{gs,th}$ ) dos MOSFETs SiC é similar ou inferior à do Si, com  $V_{gs,th}$  próxima de 2.5V, e, somado às altas velocidades de chaveamento, MOSFETs SiC necessitam de  $V_{gs}$  negativa para que desliguem completamente, entre -2V a -5V. Isso se torna um problema, já que MOSFETs SiC suportam uma māxima  $V_{gs}$  negativa menor (em módulo), de cerca de -5V a -10V, surgindo novos desafios.

Além disso,  $V_{gs,th}$  pode sofrer deslocamento negativo de mais de 0.5V quando o transistors é exposto a  $V_{gs}$  negativo por longos períodos [12]. Porém, para  $V_{gs}$  positivo, MOSFETs SiC apresentam maior estabilidade de  $V_{gs,th}$  do que dispositivos Si.

### 2.1.2 Propriedades parasitas

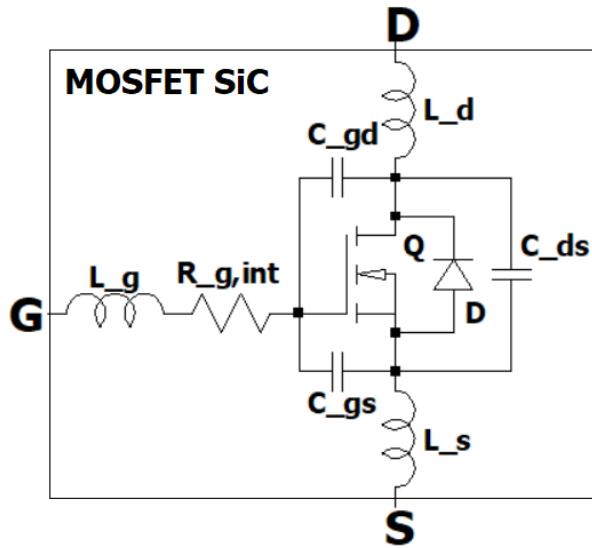

Dentre as resistências, capacitâncias e indutâncias parasitas presentes nos terminais de quaisquer componentes elétricos, no caso dos MOSFETs (figura 3) destacam-se a capacitânciā *gate-drain* ( $C_{gd}$ ), e a capacitânciā *gate-source* ( $C_{gs}$ ), que somadas sāo a capacitânciā de entrada ( $C_{iss}$ ). Essas capacitâncias determinam a carga  $Q_g$  necessária a ser introduzida no *gate* para que o dispositivo acione completamente. Devido ao MOSFET SiC possuir uma área menor que o Si, suas capacitâncias e  $Q_g$  também sāo menores, fazendo com que o dispositivo seja acionado mais rapidamente a uma mesma corrente de *gate*  $I_g$ .

Figura 3 – MOSFET SiC e seus elementos parasitas.

A capacidade  $C_{gd}$  também denota a região do plateau Miller, que é a região mais crítica do chaveamento do dispositivo. Por se tratar duma região onde ambos  $I_d$  e  $V_{ds}$  estão elevados, o driver deve fornecer sua máxima potência para que  $C_{gd}$  seja carregada mais rapidamente e as perdas sejam minimizadas. Por outro lado, os altos  $dv/dt$  e  $di/dt$  proporcionados pelo MOSFET SiC agravam surtos e oscilações que ressoam com os elementos parasitas, que podem danificar o dispositivo e o circuito do driver. Sendo assim, é necessário um comprometimento entre velocidade/eficiência e contenção de surtos e oscilações.

A capacidade  $C_{ds}$  juntamente com  $C_{gd}$  formam a capacidade de saída  $C_{oss}$ , que age como uma capacidade em série na malha de potência.  $C_{oss}$  ressoa com as indutâncias e o diodo de corpo, intensificando sobressinais de  $I_d$  e aumentando tempos de chaveamento e perdas, porém reduzindo sobressinais de tensão.

As indutâncias ressoam com os outros elementos causando oscilações e perdas no sistema. Por estarem mais presentes nos circuitos e terminais do que no MOSFET, boas técnicas de projeto podem reduzir alguns de seus problemas. Alguns transístores possuem terminais distintos de *source* entre o circuito do *gate* e o de potência, reduzindo influências das indutâncias parasitas.

Além dos elementos reativos, a resistência de *gate*  $R_g$  também é um parâmetro que influencia diretamente no projeto do driver. Ao contrário da capacidade, a resistência aumenta com a diminuição da área da seção, fazendo com que MOSFETs SiC tenham maior  $R_g$  interna e necessitem de maior corrente  $I_g$ . Nem sempre isso é um problema, já que normalmente é utilizada uma resistência de *gate* externa para conter surtos de  $I_d$ . Porém, devido ao plateau Miller e ao caráter assimétrico do MOSFET SiC, também é

comum haver circuitos de *drivers* que atravessam a  $R_g$  externa em determinada região do chaveamento.

O fenômeno de maior interesse causado pelos elementos parasitas do MOSFET SiC é o *crosstalk*, que acontece quando dois MOSFETs são chaveados em uma ponte. *Crosstalk* positivo é o mais problemático pois ele pode causar o acionamento accidental do MOSFET complementar, ocasionando em um curto-círcuito que pode danificar todo o circuito de potência. Ele ocorre quando surge um alto  $dv/dt$  positivo em um MOSFET que está desligado devido ao acionamento do outro MOSFET da ponte. Esse  $dv/dt$  faz surgir uma corrente em  $C_{gd}$  que deve fluir por  $R_g$  e  $C_{gs}$ , fazendo com que a tensão no *gate* suba para além de  $V_{gs,th}$ . *Crosstalk* negativo ocorre devido ao gradiente de  $di/dt$  na indutância de *source*  $L_s$ , fazendo com que surja tensão negativa em  $V_{gs}$ , com risco de ruptura entre os terminais de *gate* e *source*.

Para finalizar as propriedades parasitas, o diodo de corpo do MOSFET SiC, devido à largura da região de deriva do SiC ser muito menor que do Si, possui uma carga de recuperação reversa de natureza majoritariamente capacitiva, e não bipolar. Isso faz com que o tempo e a corrente de recuperação reversa sejam menores, reduzindo perdas. Porém, o alto  $di/dt$  do MOSFET somado à natureza capacitiva do diodo acentuam oscilações LC.

### 2.1.3 Propriedades térmicas

Assim como nos MOSFETs Si, a resistência da camada de deriva dos MOSFETs SiC também aumenta aproximadamente duas vezes quando a temperatura aumenta em 100°C. Porém, como a camada de deriva ocupa uma menor proporção da  $R_{ds,on}$ , a resistência de condução de MOSFETs SiC é mais estável com o aumento de temperatura, reduzindo perdas em alta potência. No entanto, como a tensão de ruptura depende da espessura da camada de deriva, dispositivos SiC se aproximam do Si conforme a tensão nominal aumenta.

Também como no Si, os elementos parasitas mantêm-se basicamente estáveis com a variação de temperatura. Desse modo, as características de chaveamento de MOSFETs SiC não se alteram com a temperatura.

No entanto, devido às menores espessuras do canal e da camada de óxido para um mesmo nível de tensão e corrente, o MOSFET SiC apresenta maior densidade de corrente de curto-círcito e menor capacidade de transferência térmica, o que leva o dispositivo a suportar menores durações máximas de curto-círcuito (SCWT), podendo ser tão baixos quanto 1-2 $\mu$ s, assim necessitando de proteções externas contra altas correntes.

### 2.1.4 Propriedades de chaveamento

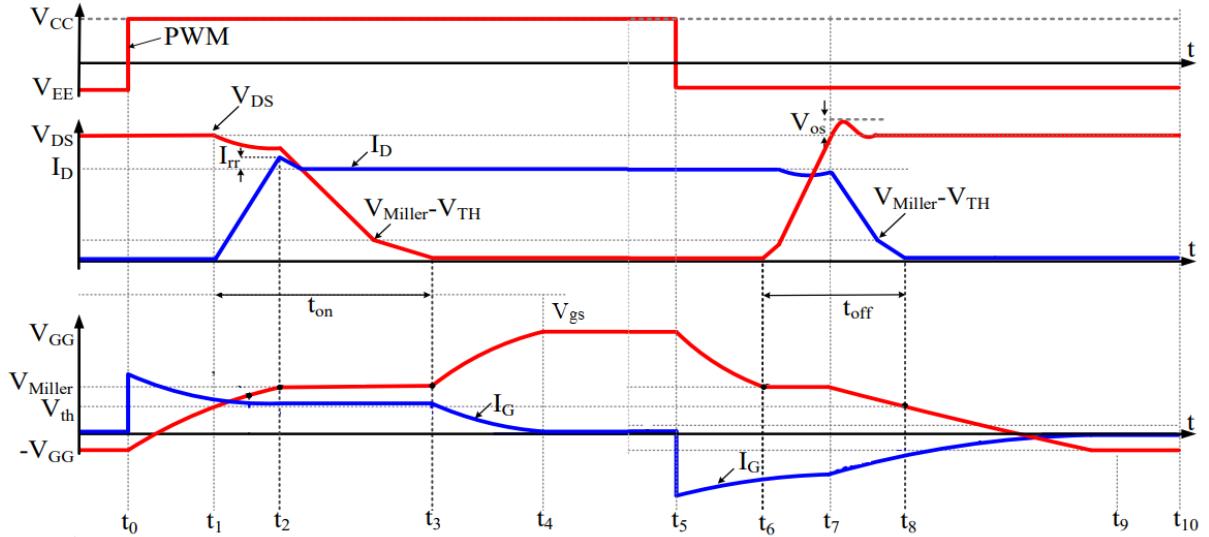

O perfil do chaveamento não difere tanto do Si, com exceção da maior tensão de açãoamento e tensão negativa de desligamento. Para melhor identificar as necessidades especiais do MOSFET SiC, é necessário entender o seu ciclo de chaveamento, que pode ser visto na figura 4.

Figura 4 – Ciclo de chaveamento do MOSFET SiC. Modificado de [24].

$t_0$  a  $t_1$ :  $V_{gs}$  passa de seu off-state até  $V_{gs,th}$  enquanto  $C_{gs}$  carrega através da corrente que flui por  $R_g$ .

$t_1$  a  $t_2$ :  $V_{gs}$  passa de  $V_{gs,th}$  até a tensão do plateau Miller, que ocorre em maior valor do que no Si.  $I_d$  começa a subir enquanto  $V_{ds}$  se mantém alto.

$t_2$  a  $t_3$ :  $V_{gs}$  se mantém no plateau Miller enquanto  $C_{gd}$  é carregado.  $I_d$  sofre um sobressinal causado pela corrente de recuperação reversa ( $I_{rr}$ ) do diodo de corpo do par MOSFET, que depende de  $di/dt$  e ressoa com as capacitâncias e indutâncias da malha.  $V_{ds}$  abaixa até seu valor mínimo, enquanto  $R_{ds}$  se mantém relativamente alto.

$t_3$  a  $t_4$ :  $V_{gs}$  carrega até seu máximo valor, reduzindo  $R_{ds}$  e colocando o transistão em seu estado de condução completa.

$t_5$  a  $t_6$ :  $V_{gs}$  reduz até o plateau Miller enquanto os capacitores de entrada descarregam.

$t_6$  a  $t_7$ :  $V_{gs}$  se mantém no plateau Miller enquanto  $C_{gd}$  descarregam e  $V_{ds}$  aumenta até seu valor máximo.  $I_d$  se mantém alta enquanto  $R_{ds}$  aumenta.

$t_7$  a  $t_8$ :  $V_{gs}$  abaixa até  $V_{gs,th}$  enquanto  $C_{gs}$  termina de descarregar e  $I_d$  abaixa, transferindo-se para o diodo de corpo do par MOSFET.  $V_{ds}$  sofre um sobressinal causado por  $dv/dt$  que ressoa com os elementos parasitas da malha.

$t_8$  a  $t_9$ :  $V_{gs}$  atinge seu valor mínimo, garantindo o desligamento completo do transístor.

Algumas dificuldades técnicas surgem dessas características. Maiores  $di/dt$  reduzem perdas no chaveamento, porém elas são causadoras de oscilações que podem danificar os transístores no passar do tempo. Além de danos diretos ao dispositivo, devido ao baixo  $V_{gs,th}$  e maior impedância do *gate*, as oscilações também podem causar acionamento ou desligamento não-intencionais do MOSFET através de acoplamento por  $C_{gd}$  e  $C_{gs}$ , aumentando as perdas e desafios.

## 2.2 Características de *gate drivers* para MOSFETs SiC

Dadas as principais características do MOSFET SiC, agora é possível estabelecer quais requisitos o driver deve atender para satisfazer a operação eficiente e segura do dispositivo, que estão elencados abaixo.

1. Fornecer tensão  $V_{gs}$  assimétrica de pelo menos -5V a 20V, garantindo o acionamento e desligamento completo do transístor.

2. Fornecer alta corrente de *gate* para compensar a alta  $R_g$ , permitindo o carregamento rápido de  $C_{iss}$  e reduzindo perdas de chaveamento.

3. Fornecer um caminho de baixa impedância durante o desligamento, reduzindo o risco de acionamento não-intencional do par MOSFET.

4. Baixas indutâncias e capacitâncias parasitas, reduzindo oscilações e *crosstalk*.

5. Monitoramento de baixa tensão *gate-source*  $V_{gs}$  (under-voltage lockout - UVLO) e sobrecorrente de *drain*  $I_d$ , evitando danos ao dispositivo.

6. Isolamento entre as linhas de sinal e potência, evitando danos e ruídos no circuito de controle causados pelos altos gradientes de tensão e corrente.

Devido às necessidades especiais da tecnologia, várias técnicas de malha aberta, malha fechada, realimentação, proteção, imunidade a ruído, dentre outras são utilizadas pensando em se otimizar cada aspecto do chaveamento. Nesta subseção serão discutidas as principais técnicas existentes para o projeto de *gate drivers* para MOSFETs SiC.

### 2.2.1 Métodos de controle de potência no *gate*

*Drivers* convencionais com tensão e resistência de *gate* fixas para acionamento e desligamento (CGD - figura 5) são raramente utilizados devido ao baixo desempenho. Vários métodos foram desenvolvidos pensando em se controlar a potência no *gate* do transístor, e, consequentemente, controlar os gradientes  $dv/dt$  e  $di/dt$  e a interferência eletromagnética

(IEM), tudo isso enquanto se é mantida uma boa eficiência energética no chaveamento. Drivers que incorporam esses métodos são chamados de *gate drivers* ativos (AGD).

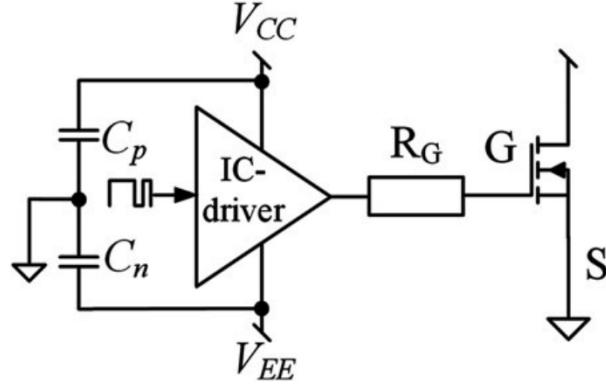

Figura 5 – Diagrama de blocos simplificado de um *gate driver* de topologia convencional [26].

O mais comum é atingir esse objetivo variando-se diretamente  $R_g$ ,  $V_{gs}$  ou  $I_g$ , mas técnicas com elementos reativos no circuito do driver também são utilizadas para se controlar indiretamente a potência no *gate*, cada um com suas vantagens e desvantagens.

#### 2.2.1.1 Controle direto da potência

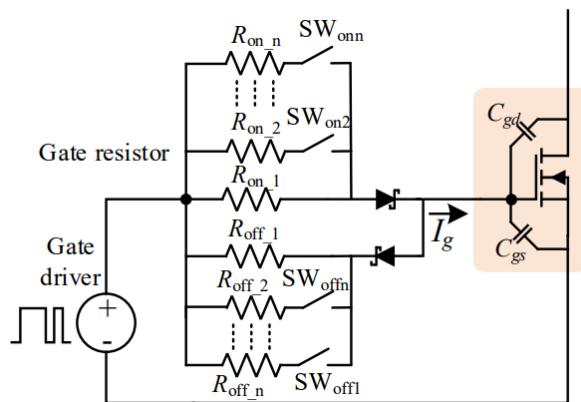

A técnica mais comum e simples de controle do *gate* de MOSFETs SiC é utilizando-se resistências  $R_g$  diferentes em determinadas etapas do chaveamento, reduzindo a potência no *gate* e os gradientes  $dv/dt$  e  $di/dt$  onde se ocorrem os surtos e oscilações e aumentando no restante para se diminuir a duração do chaveamento e as perdas. Ela pode ser realizada de maneira simples a partir da combinação de resistores em paralelo, como visto na figura 6.

Figura 6 – Diagrama de blocos simplificado de um *gate driver* de topologia de resistência variável [25].

O método de  $V_{gs}$  variável consiste na associação de fontes de tensão para se obter um  $V_{gs}$  ideal em cada etapa do chaveamento. A vantagem dessa técnica em relação à anterior é que um controle gradual da potência no *gate* pode ser obtido, porém exigindo circuitos maiores e mais caros.

Menos utilizados devido à maior complexidade de controle e de circuitos, métodos de  $I_g$  variável utilizam fontes de corrente para modular a potência no *gate*. Sua vantagem está na maior eficiência energética, já que podem eliminar a potência dissipada em  $R_g$ .

### 2.2.1.2 Controle indireto da potência

Circuitos ressonantes e reativos aproveitam-se das propriedades temporais de indutores e capacitores para acelerarem o carregamento do *gate* em determinadas etapas, essencialmente simulando fontes de tensão e corrente variáveis. Eles permitem menores tempos de subida e descida e energia regenerativa, reduzindo perdas no driver, porém aumentando o *dead time* e introduzindo atrasos de propagação. Esses circuitos também podem interagir com os elementos parasitas do MOSFET e da malha de potência, o que os tornam menos viáveis em aplicações de maior ruído.

### 2.2.2 Estratégias para controle de potência no *gate*

Para que se possa controlar as variáveis de interesse corretamente, é necessário saber o momento exato em que será realizada uma variação da potência no *gate*. Falhas na identificação desse momento podem piorar o processo de chaveamento e aumentar perdas, surtos e duração.

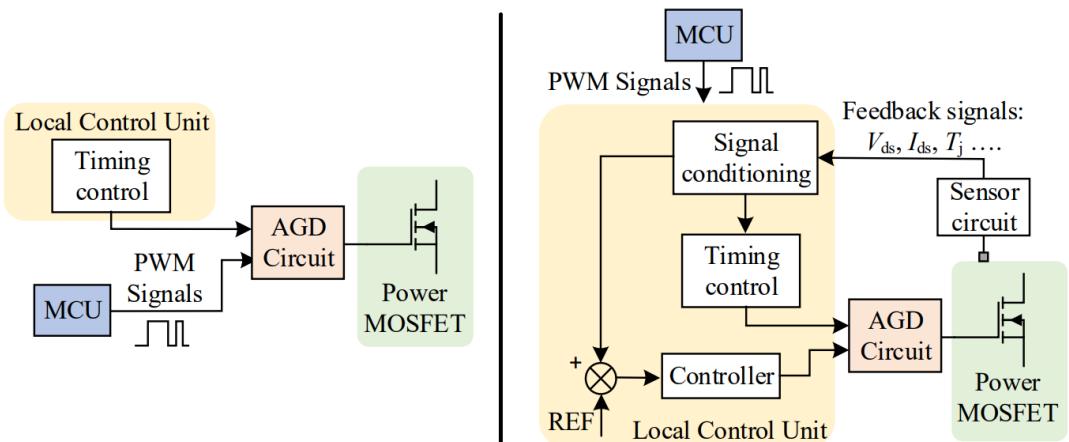

Figura 7 – Estratégias para controle de potência no *gate*: malha aberta (esquerda) e malha fechada (direita) [25].

### 2.2.2.1 Técnicas de malha aberta

Técnicas de malha aberta (figura 7) envolvem o controle do *gate* a partir de tempos fixos no chaveamento, baseando-se em temporizadores para a diferenciação entre cada etapa. Naturalmente, técnicas de malha aberta não são adaptativas e funcionam melhor em aplicações específicas onde a carga é fixa e os circuitos não sofrem de variações de temperatura ou de IEM externa. Elas também exigem a estabilidade dos componentes do circuito, o que se torna um desafio dada a pouca maturidade da tecnologia SiC.

### 2.2.2.2 Técnicas de malha fechada

Técnicas mais avançadas controlam  $dv/dt$  e  $di/dt$  em uma malha fechada (figura 7) utilizando a realimentação de parâmetros do circuito, como por exemplo  $V_{ds}$ ,  $I_d$ ,  $dv/dt$ ,  $di/dt$ , temperatura, degradação do material, etc. Podem ser de implementação simples com circuitos de controle analógicos ou controlados por CIs (circuitos integrados) digitais e indo até mesmo a redes neurais artificiais.

Circuitos mais simples comparam os parâmetros medidos a referências fixas, enquanto circuitos mais complexos adaptam a referência a partir de dados externos como a variação da carga ou até mesmo por estimativa a partir de modelos matemáticos do transístor.

### 2.2.3 Técnicas de proteção

Técnicas de proteção consistem em monitorar e manter o funcionamento adequado do circuito durante seu uso, tomando as medidas necessárias ou até mesmo desligando-o em caso de falhas.

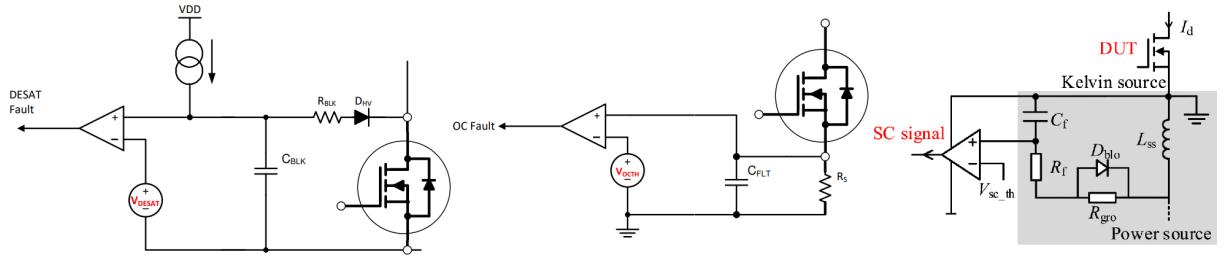

#### 2.2.3.1 Proteção de sobrecorrente e curto-circuito

Devido à menor SCWT de MOSFETs SiC, torna-se crucial a implementação de técnicas de proteção de sobrecorrente, como por exemplo as mostradas na figura 8. Maiores  $di/dt$  exigem técnicas de proteção com maior imunidade a ruído, e a imaturidade do processo de fabricação de dispositivos SiC leva a uma significante dispersão de parâmetros. Além disso, a curva característica  $I_d$  por  $V_{ds}$  de MOSFETs SiC não se comporta de maneira auto-limitante como em IGBTs Si, dificultando a detecção de sobrecorrente. Sendo assim, para prevenir falhas corretamente é necessário o comprometimento entre menores tempos de resposta e imunidade a ruído, somado ao desafio da confiabilidade.

Figura 8 – Métodos de proteção de curto-circuito: DESAT (esquerda) [28], *shunt* (centro) [28] e por indutância parasita de *source* com terminal Kelvin (direita) [27].

O método mais clássico, conhecido como DESAT, foi importado de IGBTs Si e se baseia na detecção de dessaturação pelo monitoramento de  $V_{ce}$ , desligando o IGBT caso  $V_{ce}$  ultrapasse um limiar durante um tempo maior do que o predeterminado, enquanto  $I_c$  se mantém constante durante o curto-circuito. Ele também necessita de alto tempo de resposta para evitar disparos acidentais durante o acionamento do transístor. Como MOSFETs SiC não possuem clara região de dessaturação, esse método apresenta menor confiabilidade e desempenho.

Métodos de melhor desempenho envolvem o monitoramento direto ou indireto da corrente de *drain*, e apresentam baixos tempos de resposta e alta confiabilidade. Suas desvantagens variam de acordo com o método de monitoramento, como maiores perdas no caso de resistores *shunt* e maior complexidade e tamanho para métodos magnéticos.

Alguns dispositivos possuem terminais específicos para medição integrada. Ela pode ser feita de maneira direta através de um resistor *shunt* em série a um canal isolado do dispositivo que conduz apenas uma fração de  $I_d$ , diminuindo perdas, ou de maneira indireta através da tensão na indutância parasita de *source* em dispositivos com terminais de *source* distintos para sinal e potência. A desvantagem é o custo do MOSFET no primeiro caso (*SENSEFET*) e a baixa imunidade a ruído no segundo (*Kelvin source*).

Por fim, além da detecção, o driver deve ser ainda mais cauteloso ao realizar o desligamento de um curto-circuito, já que os maiores  $di/dt$  podem danificar o semicondutor. Drivers mais avançados possuem o recurso de *soft turn-off*, ou desligamento suave, que controla a velocidade com que o transístor desliga.

#### 2.2.3.2 Proteção de baixa tensão de gate - *UVLO*

Considerando a curva de condução de MOSFETs SiC, eles necessitam de alto  $V_{gs}$  para que  $R_{ds}$  seja suficientemente baixo. Monitorar a tensão no driver torna-se essencial para que não ocorram danos no transístor devido à alta dissipação de potência quando  $V_{gs}$  não é adequado.

Esses circuitos são de simples implementação, sendo na maioria das vezes feitos com comparadores e outros componentes analógicos. Costumam ser de tensão de referência fixa, predefinida durante a etapa de projeto, que depende do MOSFET específico a ser utilizado.

#### 2.2.3.3 Proteção de crosstalk

*Crosstalk* é um fenômeno de extrema importância em MOSFETs SiC que ocorre devido aos maiores  $dv/dt$  e  $di/dt$  ao interagirem com os elementos parasitas do MOSFET complementar numa meia-ponte.

O método de proteção externa para *crosstalk* é conhecido como *Miller clamp* (figura 9), e consiste em acionar um caminho de baixa impedância para a corrente em  $C_{gd}$  enquanto o MOSFET complementar está desligado, atravessando  $R_g$  e conectando o transístor diretamente à tensão de desligamento.

Figura 9 – Diagrama de blocos de um *gate driver* com *Miller clamp* [23].

A adição de uma capacitância em  $C_{gs}$  pode auxiliar passivamente quando se interessa apenas *crosstalk* positivo (como quando se desliga o MOSFET sem tensão negativa), porém aumentando perdas e o tempo de chaveamento. Para apenas *crosstalk* negativo, transístores com *Kelvin source* e otimização de *layout* são as proteções mais efetivas sem que se prejudique o desempenho do sistema.

*Drivers* ativos (AGD) de resistência ou tensão variáveis executam essa proteção internamente de maneira direta por modulação do *gate* e de maneira indireta por redução de  $dv/dt$  e  $di/dt$ .

### 3 Análise Bibliográfica de Topologias de *Gate Drivers*

Neste capítulo serão discutidas e analisadas topologias básicas que empregam uma ou mais técnicas mencionadas anteriormente, presentes na literatura e no mercado. Parâmetros como eficiência, controle de IEM e aplicações serão avaliados.

#### 3.1 Topologias de *gate drivers* na literatura

Na última década vários estudos foram realizados visando-se operar adequadamente transístores de tecnologia SiC, sejam propondo melhorias a partir de técnicas empregadas em outros dispositivos ou criando novas topologias para atingir esse objetivo. Abaixo foram selecionados dois estudos que exemplificam e servem de guia para a elaboração de *gate drivers* para MOSFETs SiC.

##### 3.1.1 Tensão variável

Em [13] o autor desenvolve um circuito baseado em tensão variável no *gate*. O *driver* opera em quatro níveis de tensão: -5V, 0V, 15V e 20V, e utiliza a realimentação de  $I_d$  e  $V_{ds}$  junto a um temporizador para realizar a seleção de nível.

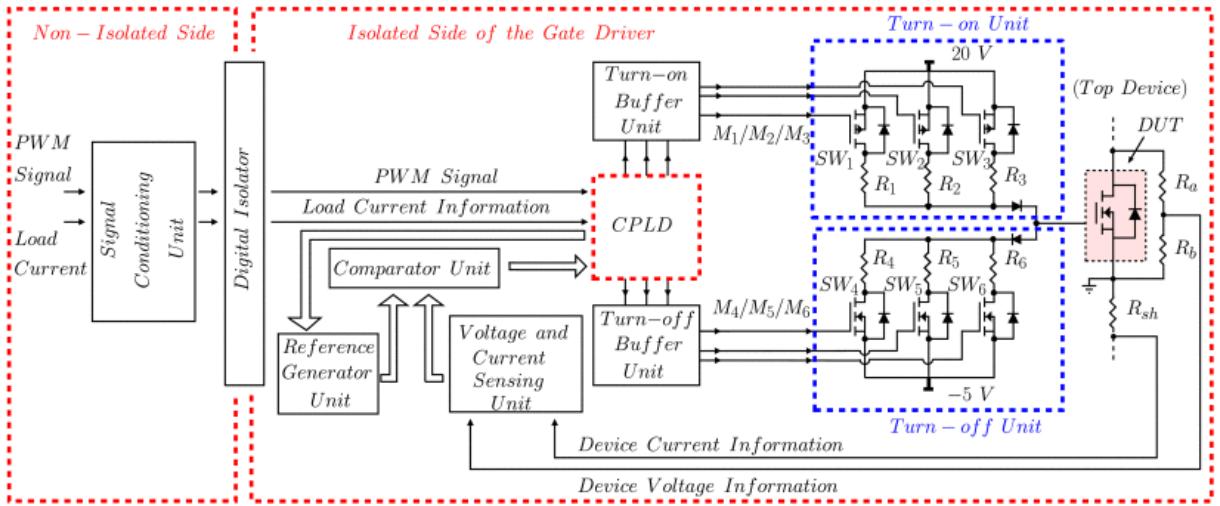

Figura 10 – Diagrama de blocos do AGD de tensão variável [13].

O *hardware* (figura 10) é composto por um optoacoplador para isolamento, um dispositivo lógico complexo programável (CPLD) para controle de resposta rápida, um circuito de detecção de  $V_{ds}$  e um de detecção indireta de  $I_d$  baseado na indutância de *source* que

utilizam três comparadores de alta velocidade, e dois *drivers* de MOSFET Si de alta velocidade e potência. O autor afirma que a implementação é de menor custo do que um módulo CGD adicionado de um circuito de amortecimento (snubber), em especial em aplicações de alta potência, além de ser de baixa complexidade por não necessitar de fonte de tensão negativa.

Após iniciar o chaveamento em potência máxima (20V) para o rápido carregamento de  $C_{iss}$ , o circuito executa a detecção de  $I_d$  indiretamente através da indutância de *source*, que serve de parâmetro para iniciar a contagem de um timer  $t_{d1}$  assim que  $I_d$  começa a subir em  $t_1$ . O timer indica o tempo no chaveamento em que  $I_d$  está próxima de seu máximo e  $V_{gs}$  prestes a entrar no plateau Miller. Então, em  $t_{1A}$ , o *driver* diminui sua tensão para 15V para reduzir  $di/dt$  e consequentemente o surto de corrente em  $I_d$ . Após o circuito detectar que  $V_{ds}$  atingiu sua referência em  $t_3$ , a tensão máxima de *gate* é aplicada novamente para garantir a condução total do MOSFET SiC. Os modos de operação no acionamento podem ser vistos na figura 11. O desligamento é realizado de maneira análoga.

Figura 11 – Modos de operação do AGD de tensão variável no acionamento. (a)  $V_{gs} = 20V$  (b)  $V_{gs} = 15V$  [13].

O autor avalia o AGD em comparação a um CGD de resistência e tensão fixas, realizando testes de duplo-pulso sob diferentes resistências de *gate* (em ambos os *drivers*), temperaturas de operação e correntes de carga. O autor optimiza os temporizadores para cada experimento, visando um comprometimento entre eficiência e contenção de surtos.

Na figura 12 o autor mostra o resultado de testes realizados mantendo-se um mesmo

sobressinal de corrente no acionamento e um mesmo sobressinal de tensão no desligamento, obtidos através da variação de  $R_g$  em ambos CGD e AGD.

Figura 12 – Análise de (a) tempo e (b) perdas de chaveamento em função do sobressinal de  $I_d$  (acima) ou de  $V_{ds}$  (abaixo) no AGD de tensão variável [13].

Sob uma tensão de 500V e uma carga de 280A, o *driver* gera 28% menos perdas de energia e aciona em um tempo 29% menor, para um sobressinal de corrente de 21A. Para um sobressinal de tensão de 100V, o *driver* desliga o MOSFET SiC com 32% menos perdas e em 33% menor tempo. Para chaveamentos mais rápidos os *drivers* começam a convergir, já que não há o devido controle de  $dv/dt$  e  $di/dt$ , porém o AGD em questão se mostra superior em todos os testes.

Os resultados mostram que o circuito proposto mantém suas características em variações de temperatura e carga, já que os atrasos causados por essas variações são corrigidos pelo circuito de realimentação. O autor menciona que variação de carga causa desvio em relação ao temporizador ótimo, porém diz que o desvio para cargas pequenas é negligenciável quando o *driver* está otimizado para cargas maiores.

O estudo também mostra uma análise do espectro de frequências de  $V_{ds}$  e  $I_d$ , onde o AGD reduz efetivamente a geração de IEM na faixa de 1MHz a 10MHz, e em especial na frequência de ressonância do circuito em 9.2MHz, com uma atenuação de até 7dB.

No entanto, o autor não informa as perdas adicionais no circuito do *driver*, e também não é especificado se o circuito é funcional apenas em módulos de transístores com *Kelvin source*, já que o terminal e as indutâncias parasitas são necessárias para o funcionamento do circuito de realimentação. Também não é comentado sobre nenhum método de proteção, que é um caminho claro a se aprofundar caso o engenheiro decida utilizar essa topologia.

### 3.1.2 Resistência variável

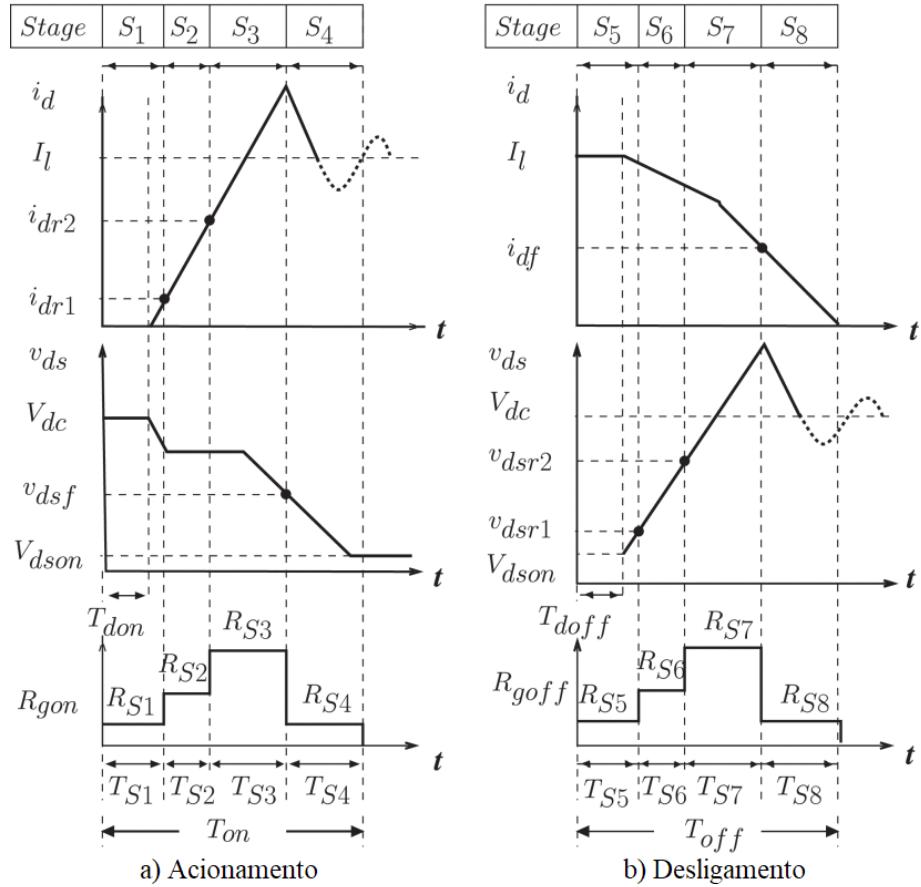

Em [14] é proposta uma topologia mais avançada, baseada em multiestágios de  $R_g$  variável. O *driver* possui tensões de *gate* fixas de -5V e 20V, e quatro etapas distintas de acionamento e quatro de desligamento, cada etapa com seu nível de resistência. Além de sensores de  $V_{ds}$  e  $I_d$ , o *driver* também pode utilizar dados externos da corrente de carga, permitindo ajustes de referência em casos de carga variável.

Além dos condicionadores de sinais e isolamento, o artigo divide a topologia em quatro unidades principais, que podem ser vistas na figura 13. Uma unidade de monitoramento direto de ambos  $V_{ds}$  e  $I_d$  com resistor *shunt* para maior precisão, uma unidade comparadora com três referências distintas para ambas tensão e corrente, um CPLD para controle lógico, e por fim a unidade de chaveamento com três linhas de acionamento e três de desligamento, com *buffers* a MOSFETs de sinal com suas respectivas resistências.

Figura 13 – Diagrama de blocos do AGD de resistência variável [14].

O chaveamento é dividido em quatro etapas sequenciais, cada uma com um objetivo. Na primeira etapa o *driver* fornece potência máxima ( $R_g = 1.6\Omega$ ) para reduzir o tempo de atraso. Em seguida, a resistência de *gate* é aumentada até um valor intermediário ( $6\Omega$ )

para controlar os gradientes de  $dv/dt$  ou  $di/dt$ . Na terceira etapa  $R_g$  atinge seu valor máximo ( $15\Omega$ ) para minimizar sobressinais. Por fim  $R_g$  volta a ser baixa ( $1.7\Omega$ ) para reduzir o tempo total de chaveamento e a impedância do *gate* durante a condução plena do MOSFET SiC. Os quatro níveis de resistência são obtidos a partir de combinações das linhas de resistores ( $R_{1,4} = 10\Omega$ ,  $R_{2,5} = 15\Omega$  e  $R_{3,6} = 2\Omega$ ). A troca de etapas ocorre quando  $V_{ds}$  ou  $I_d$  atingem valores-chave, que variam de acordo com parâmetros do transístor ou do circuito. O chaveamento pode ser visto na figura 14.

Figura 14 – Modos de operação do AGD de resistência variável [14].

O *driver* é avaliado em testes de duplo-pulso em relação a um CGD de resistência fixa igual a  $10\Omega$ , ambos sob mesma tensão de 600V e carga de 20A. Os tempos de cada estágio no AGD são otimizados para o melhor comprometimento entre sobressinal, perdas e tempo de chaveamento.

Sob uma mesma indutância parasita da malha de potência  $L_{loop}$  de  $350nH$ , é possível ver na figura 15 as formas de onda do chaveamento de CGD e AGD. Houve uma redução de 50% para 20% no sobressinal de corrente no acionamento e redução de 5ns na duração do chaveamento, com perdas de 0.22mJ para o CGD e 0.18mJ para o AGD. Para o desligamento, houve uma redução de 45% para 20% no surto de tensão e a mesma redução

de duração, além de uma clara atenuação nas oscilações, com perdas 0.9mJ para o CGD e 0.6mJ para o AGD.

O autor realiza o mesmo teste para diferentes indutâncias parasitas e variando  $R_g$  do CGD e  $R_{2,5}$  do AGD. Em todos os casos o AGD se mostra superior ao CGD em contenção de sobressinais e eficiência energética. No entanto, o artigo não menciona técnicas de proteção de sobrecorrente ou UVLO e também não realiza análise de custos.

Figura 15 – Formas de onda para acionamento (esquerda) e desligamento (direita) para (a) CGD e (b) AGD de resistência variável [14].

O desempenho do AGD também é avaliado em um inversor que alimenta um motor de indução sob tensão de 400V, corrente de 8A rms e frequência de chaveamento de 20kHz. Devido à natureza variável da carga, o AGD recebe informação externa da corrente no motor, que é utilizada para gerar referências precisas para o circuito comparador.

Pela carga possuir alta capacitância, o *driver* não é capaz de restringir  $di/dt$  suficientemente. A primeira solução proposta é utilizar um filtro RL em série com a carga para ambos CGD e AGD, promovendo uma redução de sobressinal de corrente de 100% no caso do CGD para 50% no AGD. A segunda consiste em modificar o AGD fundindo os estágios de 1 a 3 e utilizando uma alta resistência ( $100\Omega$ ), reduzindo o sobressinal para

apenas 10%, porém aumentando a duração do acionamento para 200ns e perdas para 1mJ, valores significativamente maiores.

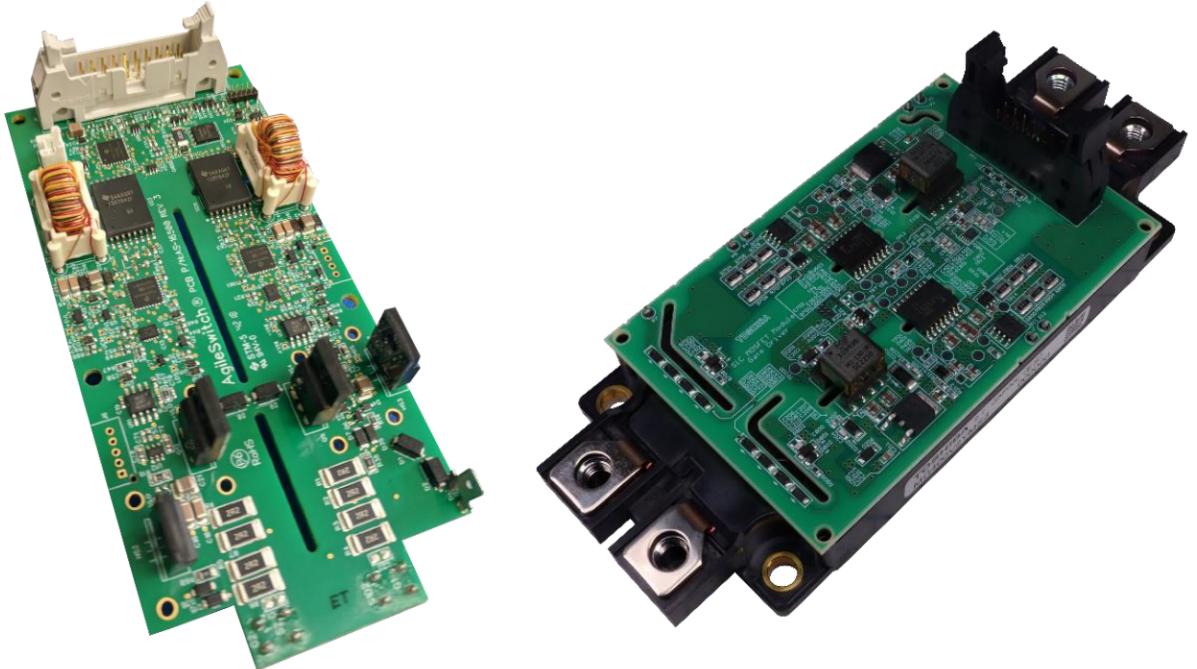

### 3.2 Topologias de gate drivers no mercado

*Gate drivers* específicos para MOSFETs SiC presentes no mercado são encontrados em dois tipos: módulos funcionais completos ou chips com recursos variados porém que demandam componentes periféricos externos.

Módulos (figura 16) são placas de circuitos que possuem todos os blocos necessários para o funcionamento seguro do *driver*, como fontes de potência, isolamento e condicionamento de sinal, funções de proteção, monitoramento e realimentação, dentre outros. Vários desses recursos costumam ser programáveis, seja por *software* ou *hardware*.

Figura 16 – *Gate drivers* modulares dos fabricantes Microchip [15] (esquerda) e Toshiba [16] (direita).

No entanto, *drivers* modulares possuem um alto custo (dezenas de dólares), fazendo com que chips de circuitos integrados sejam os mais populares no mercado. Diversos fabricantes os produzem nos mais variados níveis de complexidade, normalmente custando abaixo de 1 dólar para os mais simples ou até cerca de 10 dólares para *drivers* com mais recursos.

Devido à tecnologia SiC exigir atenção especial, sites das grandes fabricantes de CIs costumam ter páginas específicas que agrupam *gate drivers* e outros chips dedicados a

MOSFETs SiC, facilitando a procura do projetista. Além disso, elas quase sempre fornecem notas de aplicação e outros recursos que podem auxiliar no projeto de um *gate driver*. Abaixo são apresentadas as linhas de dois fabricantes: *Infineon Technologies* e *Texas Instruments*.

### 3.2.1 Gate drivers da Infineon Technologies

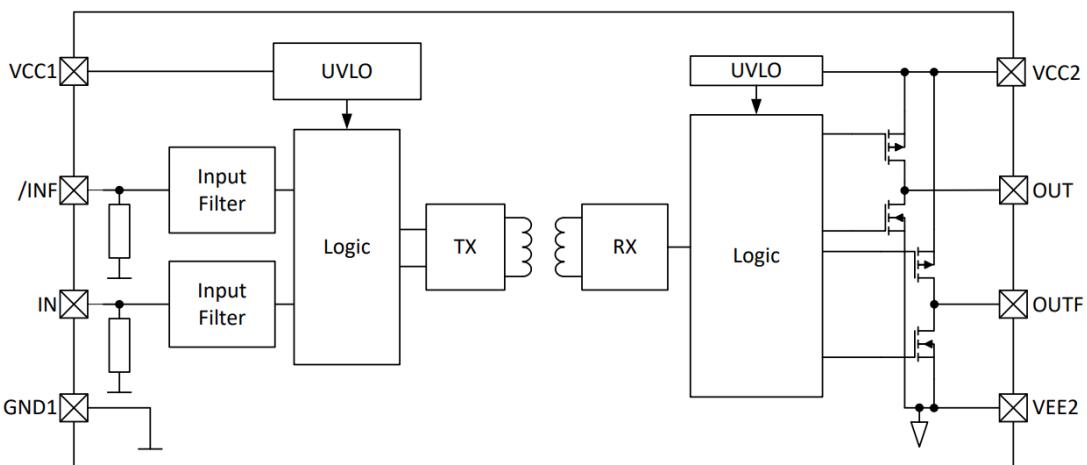

A fabricante de componentes *Infineon* possui famílias dedicadas a MOSFETs SiC em sua linha de *gate drivers* *EiceDRIVER™*. Alguns dispositivos suportam classes de tensão de até 2300V, com uma capacidade de *driver* de até 20A em  $I_g$  e 40V em  $V_{gs}$ . Todos eles possuem isolamento galvanizado e UVLO.

A família mais simples é a X3 Compact, com CIs de 8 terminais e um canal. Das opções disponíveis, o projetista pode escolher alguns recursos em detrimento de outros, dentre eles: isolamento funcional ou reforçado; saídas separadas para acionamento e desligamento ou *Miller clamp* ativo; maiores  $I_g$  e  $V_{gs}$  ou menores atrasos de propagação. Toda a família ainda possui uma gama de tensões de UVLO fixas que podem ser escolhidas, com exceção de um único membro com UVLO ajustável por resistores externos. Os custos variam entre aproximadamente 1.5 dólar a 3 dólares, dependendo da escolha.

A única família com controle variável da potência no *gate* é a 2L-SRC, também de 8 terminais e um canal, com isolamento reforçado e duas opções de corrente de *gate*. A família possui uma versão com controle de potência para acionamento e desligamento e outra com controle apenas de acionamento porém com *Miller clamp*. O controle é de resistência variável, com o *driver* (figura 17) ligando um novo  $R_g$  em OUTF em paralelo à saída preferencial OUT para aumentar a potência no *gate*, utilizando um sinal externo em /INF. Os *drivers* custam em média 3 dólares.

Figura 17 – Diagrama de blocos do *driver* 1ED3241MC12H, da família 2L-SRC da *Infineon* [18].

Outras famílias mais complexas apresentam recursos como DESAT rápido compatível com SiC, desligamento suave, monitoramento e reportagem de falhas, comunicação serial, dois canais e ajuste de parâmetros. Em [17] a empresa fornece um documento com uma breve apresentação da linha e alguns de seus recursos, além de sugestões de projeto como por exemplo otimização de PCIs e o uso de transístores da *Infineon* da linha *CoolSiC™*, a qual a empresa diz ter parâmetros superiores, dentre eles maior  $V_{gs,th}$ , menor  $V_{gs}$  para condução completa e não necessitarem de  $V_{gs}$  negativo para desligamento.

Por fim, os únicos circuitos e componentes externos no lado do chaveamento que os *drivers* necessitam para a operação de MOSFETs SiC são fontes de alimentação e resistores  $R_g$ , além de outros eventuais componentes passivos para ajuste de parâmetros.

### 3.2.2 Gate drivers da Texas Instruments

A *Texas Instruments* possui uma das maiores linhas de *gate drivers* para MOSFETs SiC, com opções não-isoladas ou com isolamento capacitivo, o qual a empresa diz ser superior a indutivo ou óptico. Alguns *drivers* suportam classes de transístor de até 2121V, com 20A de  $I_g$  e 36V em  $V_{gs}$ .

Assim como na concorrente, todos os *drivers* possuem UVLO, e também há diversas famílias com recursos que podem ser escolhidos, como *Miller clamp*, saídas separadas, proteção de sobrecorrente, reportagem de falhas, ajuste de alguns parâmetros, dentre outros, disponíveis em uma gama de correntes  $I_g$  e tempos de chaveamento e propagação, em um ou dois canais.

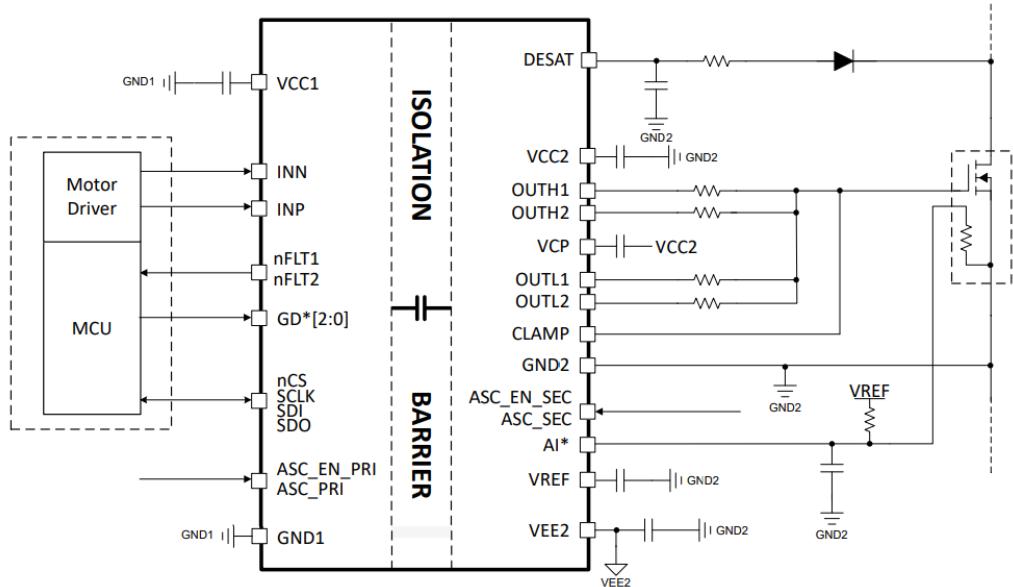

Figura 18 – Esquemático simplificado do *driver* UCC5881-Q1, da *Texas Instruments* [19].

O *driver* mais completo da companhia é o UCC5881-Q1 (figura 18), que conta com controle de potência com três níveis de  $R_g$  separadamente para acionamento e desligamento em até 20A de  $I_g$  e 30V de  $V_{gs}$ , proteção de sub e sobretensão, proteção de sobrecorrente por DESAT ou  $R_{shunt}$ , proteção de temperatura, *Miller clamp*, desligamento suave, conversores analógico-digitais e comparadores digitais integrados, reportagem de falhas e parâmetros e comunicação serial. O *driver* possui um custo aproximado de 10 dólares, porém tem baixa disponibilidade no mercado por ser um produto recente.

### 3.3 Discussão

Apesar da recente idade da tecnologia, já existe uma imensa variedade de *drivers* na literatura utilizando e explicando diversos conceitos úteis para o chaveamento de MOS-FETs SiC. No mercado, no entanto, é raro encontrar *drivers* que diretamente permitam o controle da potência no *gate*, porém a grande maioria é carregado de recursos úteis como UVLO, camada de isolamento, *Miller clamp* e baixo atraso de propagação e com preços competitivos, e as opções mais completas muitas vezes possuem um valor não muito distante das mais simples.

A união das topologias presentes na literatura a circuitos integrados de *gate drivers* disponíveis no mercado pode simplificar a elaboração do projeto e também deixá-lo mais robusto ao integrar os mecanismos internos de proteção do CI a uma lógica de chaveamento que promove maior eficiência e vida-útil ao transístor.

## 4 Análise Computacional de Topologias de *Gate Drivers*

Visando-se observar as características do MOSFET SiC em funcionamento, foram feitas simulações de topologias de *gate drivers* aplicadas em situações de carga fixa em testes de duplo-pulso.

Três topologias foram estudadas, sendo uma de resistência variável, uma de tensão variável e um *gate driver* convencional. Parâmetros como resistência de *gate* ( $R_g$ ) e indutância parasita de malha ( $L_{loop}$ ) foram variados para se observar as mudanças de comportamento no circuito. Além disso, também foi avaliado o fenômeno de *crosstalk*.

Por ser de interesse do estudo apenas a resposta do transístor em razão da topologia do *gate driver*, a estratégia de disparo escolhida para os AGDs foi de temporizadores com tempos fixos obtidos experimentalmente, simplificando os circuitos. Também foram realizados alguns experimentos utilizando outro modelo de transístor.

### 4.1 Metodologia

Os circuitos foram simulados no *software LTspice* e utilizando modelos matemáticos de MOSFET SiC e *gate driver* obtidos diretamente do site dos fabricantes.

As topologias de AGD escolhidas foram baseadas nos estudos mencionados na seção anterior, de tensão variável e resistência variável. Os circuitos foram simplificados removendo-se os blocos de detecção e comparação e adotando-se uma estratégia de controle de malha aberta com temporizadores fixos. Ambas topologias foram projetadas para dois estágios de potência, sendo o estágio 1 o de máxima potência e o estágio 2 o de mínima.

A estratégia de controle adotada possui três etapas. Inicialmente mantém-se máxima potência de *gate* para se diminuir o tempo de atraso. Em seguida, quando  $I_d$  atinge o limiar escolhido de 15% de  $I_d$  de operação no acionamento (ou  $V_{ds}$  no desligamento), o *driver* entra no estágio de menor potência de *gate*, reduzindo oscilações e surtos. Por fim, quando  $I_d$  ou  $V_{ds}$  atingem seu máximo sobressinal, o *driver* volta a entregar máxima potência ao *gate* para garantir a operação ideal do transístor.

Para se manter os testes justos, a parametrização dos elementos dos circuitos foi baseada em todas as topologias possuírem uma mesma perda de chaveamento (diferentes para acionamento e desligamento), dada uma situação escolhida de  $R_g$ ,  $L_{loop}$  e semicondutores, e então avaliadas as demais diferenças de comportamentos entre as topologias a partir de uma mesma perda energética. A topologia base escolhida foi a de tensão variável, que, a partir de seu  $R_{g, vvar}$ , serviu de parâmetro para se definir experimentalmente os  $R_g$  do CGD e do AGD de resistência variável.

Os indicadores de desempenho avaliados foram sobressinais de  $I_d$  ou  $V_{ds}$  (de aciona-

mento e desligamento, respectivamente), atraso de chaveamento (considerado quando  $I_d$  atinge 30A no acionamento e 0A no desligamento) e *crosstalk*. Os testes foram realizados em quatro situações, sendo a), b) e c) para o transístor da *NXP* e d) para o transístor da *Microchip*:

- a)  $R_{g,vvar} = 10\Omega$  e  $L_{loop} = 100nH$ .

- b)  $R_{g,vvar} = 7.5\Omega$  e  $L_{loop} = 100nH$ .

- c)  $R_{g,vvar} = 10\Omega$  e  $L_{loop} = 300nH$ .

- d)  $R_{g,vvar} = 10\Omega$  e  $L_{loop} = 100nH$ .

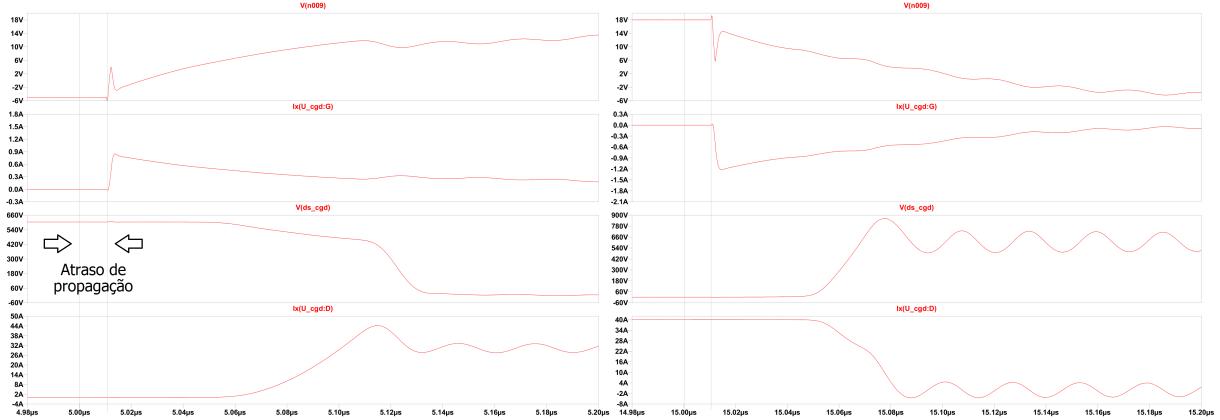

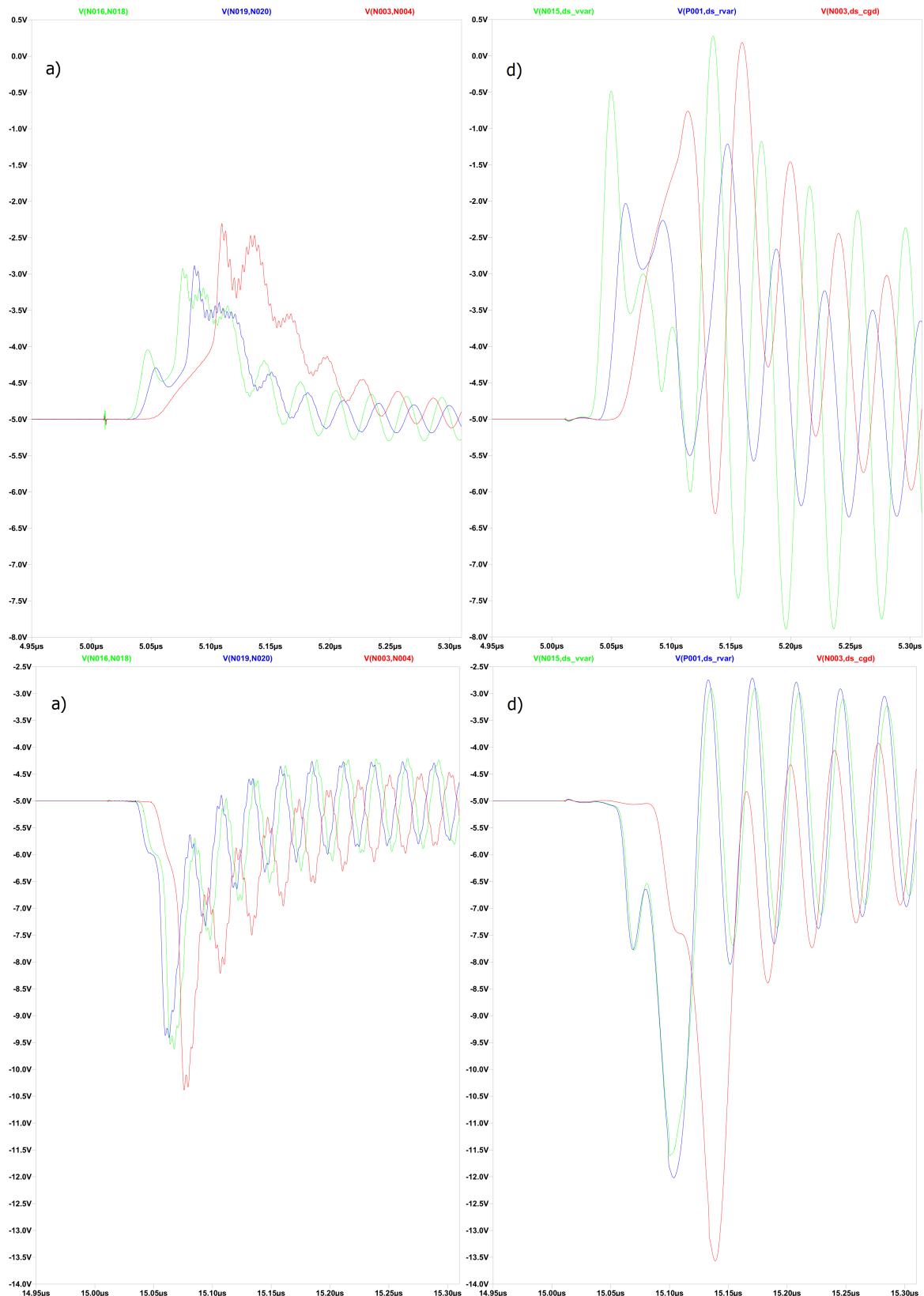

Para a avaliação de *crosstalk*, foi considerado um  $R_{g,h}$  no lado de alta equivalente ao  $R_g$  de desligamento visto pelo transístor sob teste, assim como uma tensão  $V_{gs,h}$  de desligamento de -5V, que seriam os valores tipicamente vistos quando o MOSFET complementar está desligado.

#### 4.1.1 Hardware

As simulações foram realizados sob uma configuração de teste de duplo-pulso com carga fixa de  $300\mu H$  e  $8.5\Omega$  e capacitância parasita de  $50pF$  submetida a 600V de tensão e chaveada a 50kHz com 50% de fator de trabalho, resultando numa corrente de carga de regime permanente de 30A no início do acionamento. A malha de potência também possui uma indutância parasita, que varia a depender do teste realizado.

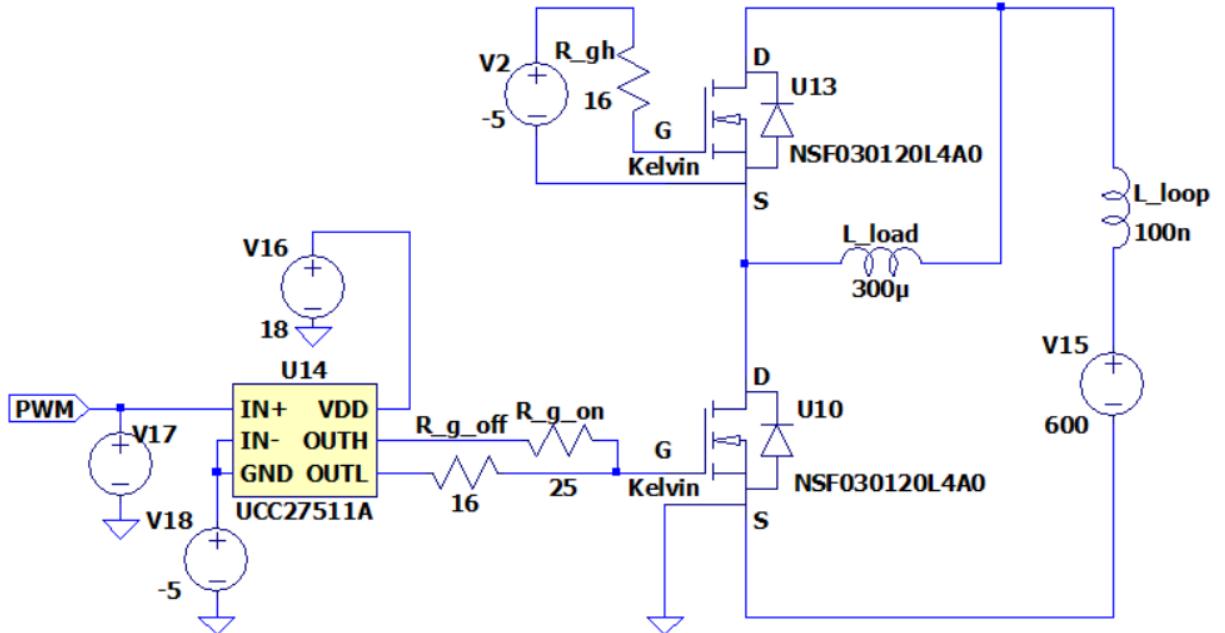

O principal MOSFET SiC utilizado foi o NSF030120L4A0 [20], de 1200V e  $R_{ds}$  de  $30m\Omega$  e carga  $Q_g$  de 113nC sob  $V_{gs}$  típico de -5/+18V, com terminal de *Kelvin source*, da *NXP*. Como *buffer* foi escolhido o *driver* UCC27511A [21], da *Texas Instruments*, um *driver* não-isolado com tensão de operação de +4.5/+18V e capacidade de 4A de corrente de acionamento e até 8A de desligamento, com saídas separadas entre os dois, e atraso de propagação típico de 13ns.

Também foram realizados testes com o MSC025SMA120B [22], de 1200V e  $R_{ds}$  de  $25m\Omega$  e carga  $Q_g$  de 232nC sob  $V_{gs}$  típico de -5/+20V, sem terminal de *Kelvin source*, da *Microchip*. Devido a limitações do *driver* e para manter os testes equivalentes, esse transístor foi operado com  $V_{gs}$  máxima de 18V.

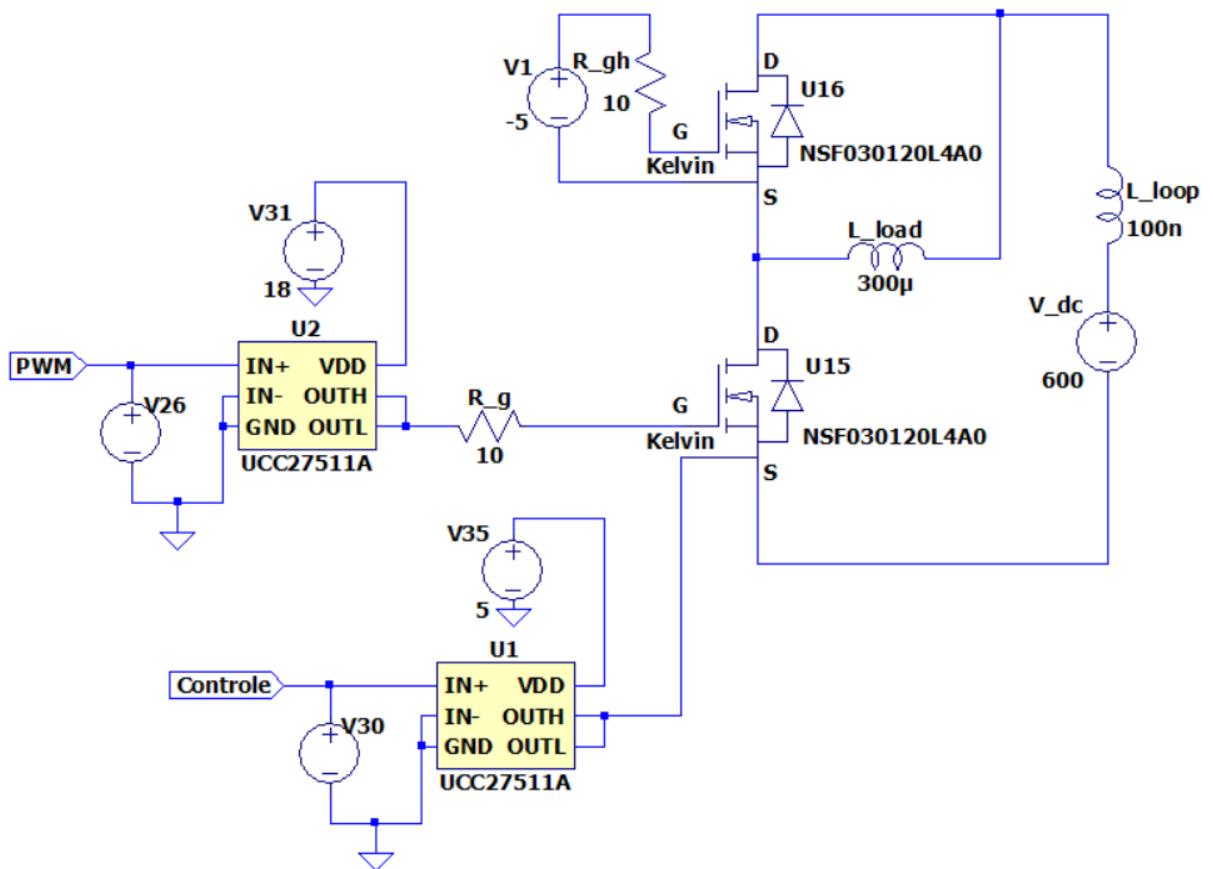

##### 4.1.1.1 Tensão variável

A topologia de tensão variável utilizada foi a mesma vista em [13], seguindo os mesmos modos de operação. As únicas modificações foram nos tempos escolhidos, que seguem de

acordo com o mencionado anteriormente nessa seção, e nos níveis de tensão de acionamento, que passaram a ser de 13V e 18V, adequando-se ao recomendado do MOSFET SiC utilizado. Os níveis de tensão de desligamento foram mantidos em -5V e 0V.

O CI conectado diretamente no *gate* pode receber o sinal de PWM sem alterações, ligando e desligando o MOSFET normalmente. O CI conectado no terminal de *source* (*Kelvin* ou comum) executa o controle de nível, aumentando ou reduzindo a potência conforme necessário.

Este circuito, que pode ser visto na figura 19, serve de parâmetro para os demais dentro de um mesmo tipo de teste. Ou seja, a partir de seu  $R_g$  previamente definido, os  $R_g$  dos outros circuitos foram escolhidos de modo a se igualarem nas perdas energéticas de chaveamento.

Figura 19 – Circuito de simulação da topologia de tensão variável.

#### 4.1.1.2 Resistência variável

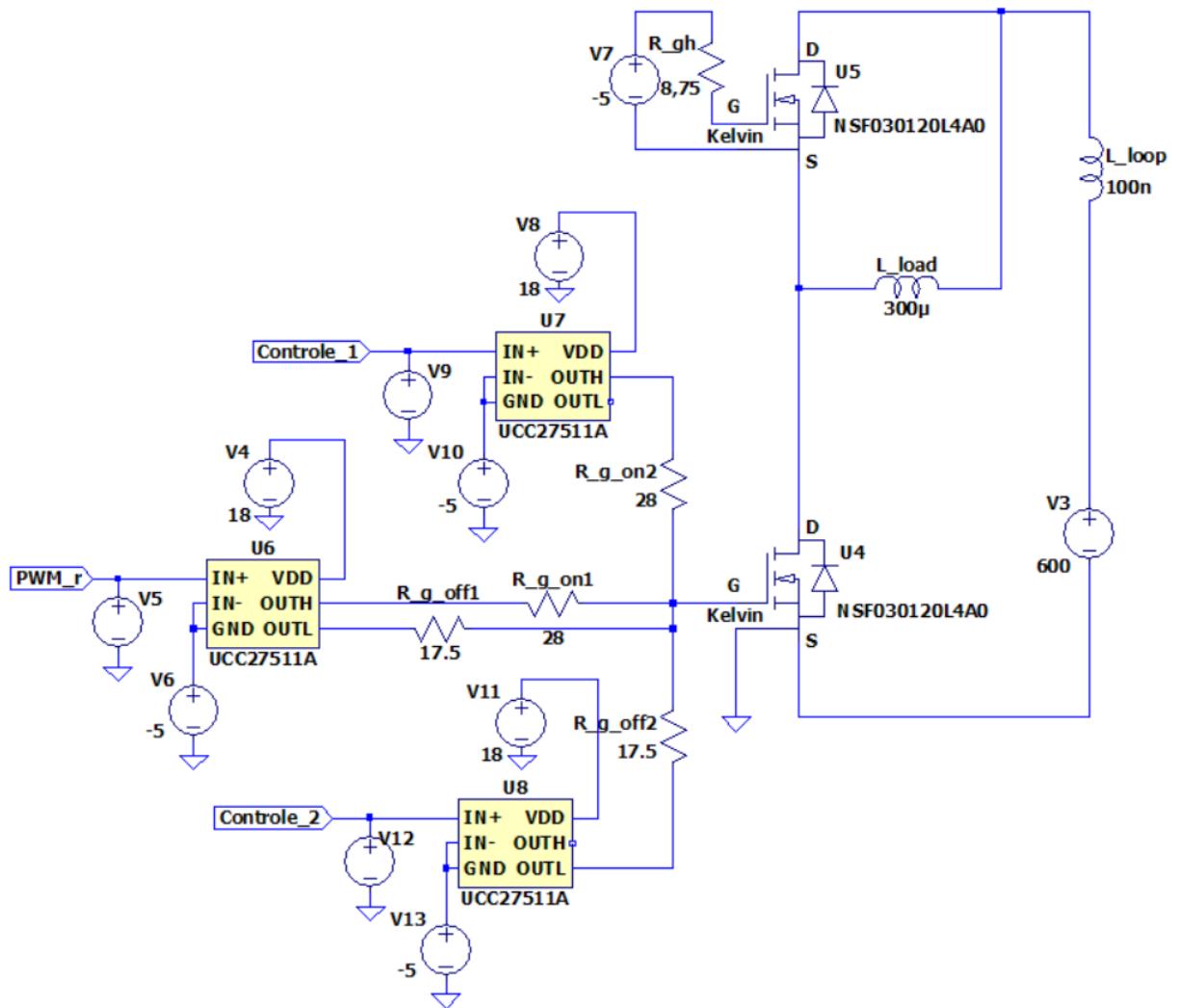

O *gate driver* de resistência variável segue a topologia de [14] simplificada para apenas dois níveis de resistência durante uma comutação, ao invés de quatro.

O circuito (figura 20) se aproveita das saídas separadas do *driver* discreto (OUTL e OUTH) para ligar uma resistência em paralelo apenas em seu devido momento, mantendo a saída em alta impedância quando ela não deve ser usada. Essa configuração não seria possível caso o CI fosse de única saída, já que os braços de resistência paralelas sempre estariam ativos para um lado ou para o outro.

Ao mesmo tempo o PWM sem alterações é injetado no *gate* através do CI conectado convencionalmente, fazendo desse circuito uma modificação simples de projeto em relação ao CGD, contando apenas com os adicionais em paralelo. As resistências paralelas foram mantidas iguais ao braço principal para fins de uniformidade e simplificação.

Figura 20 – Circuito de simulação da topologia de resistência variável.

#### 4.1.1.3 Gate driver convencional

O último circuito simulado foi o da topologia convencional de *gate driver* (figura 21), com valores distintos de  $R_{g, on}$  e  $R_{g, off}$  para que as perdas energéticas sejam equivalentes ao circuito parâmetro.

Figura 21 – Circuito de simulação da topologia convencional.

## 4.2 Resultados

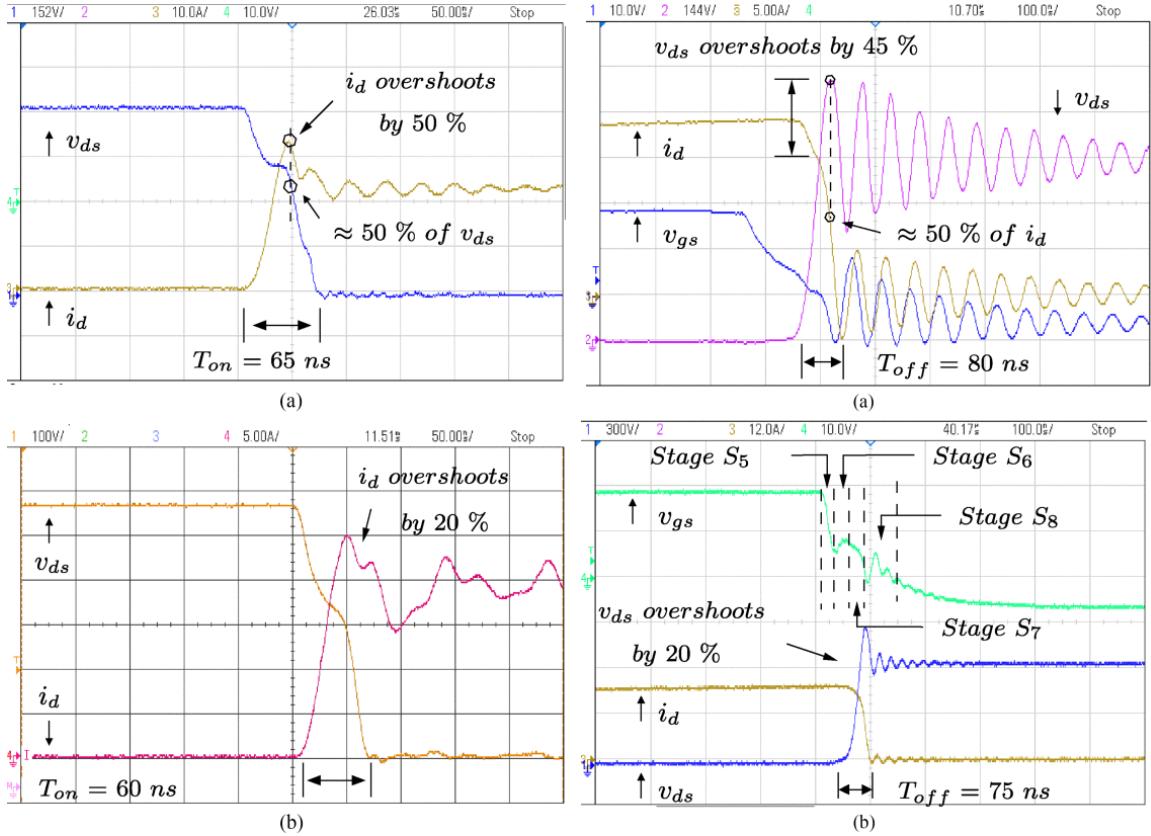

As topologias foram implementadas no *software* de simulação e foram encontrados graficamente os tempos de troca de estágios e  $R_g$ , de acordo os valores definidos anteriormente de  $I_d$ ,  $V_{ds}$  e da situação a), b), c) ou d). As formas de onda foram registradas sob intervalos de tempo de 0.1ns.

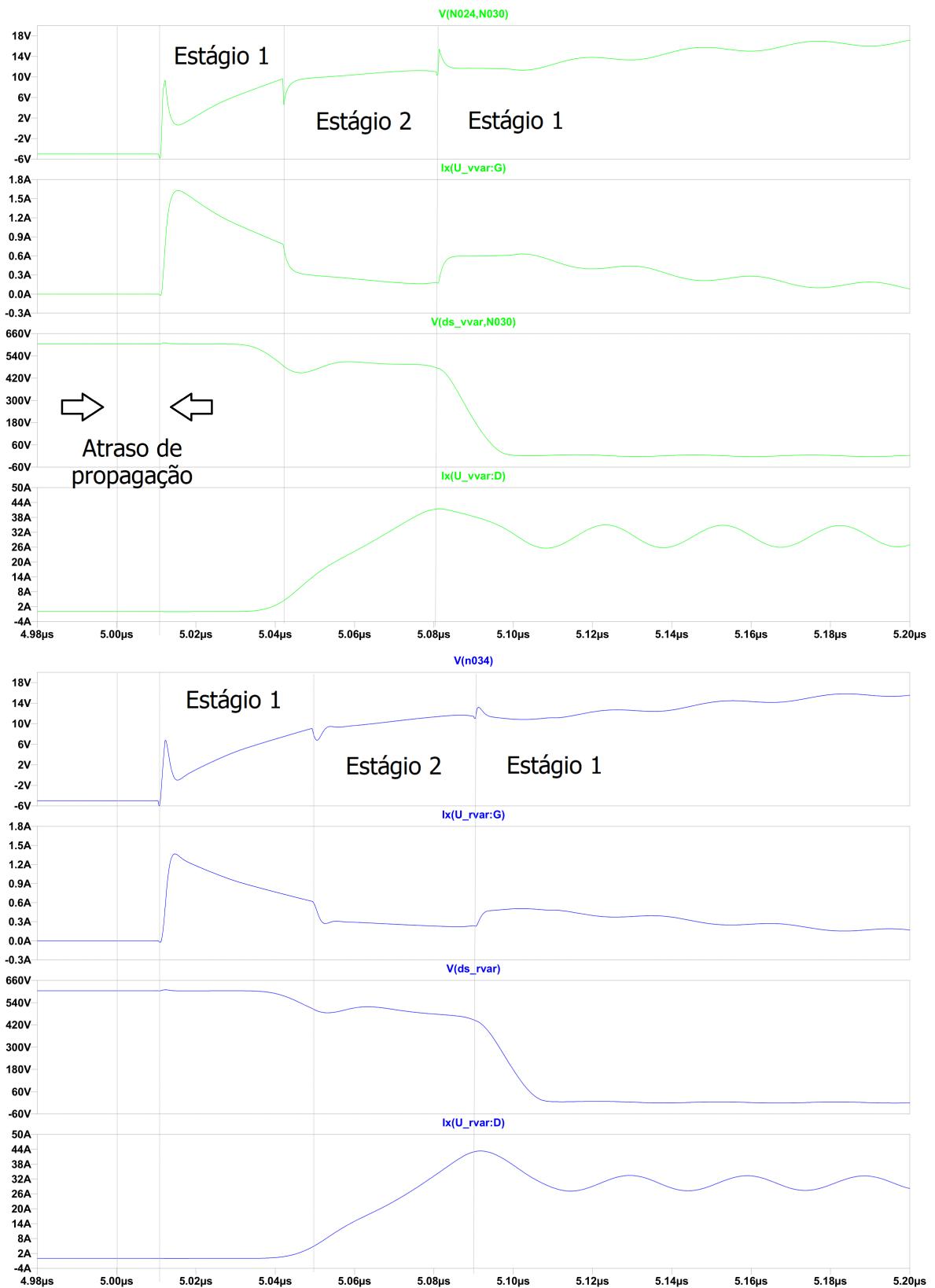

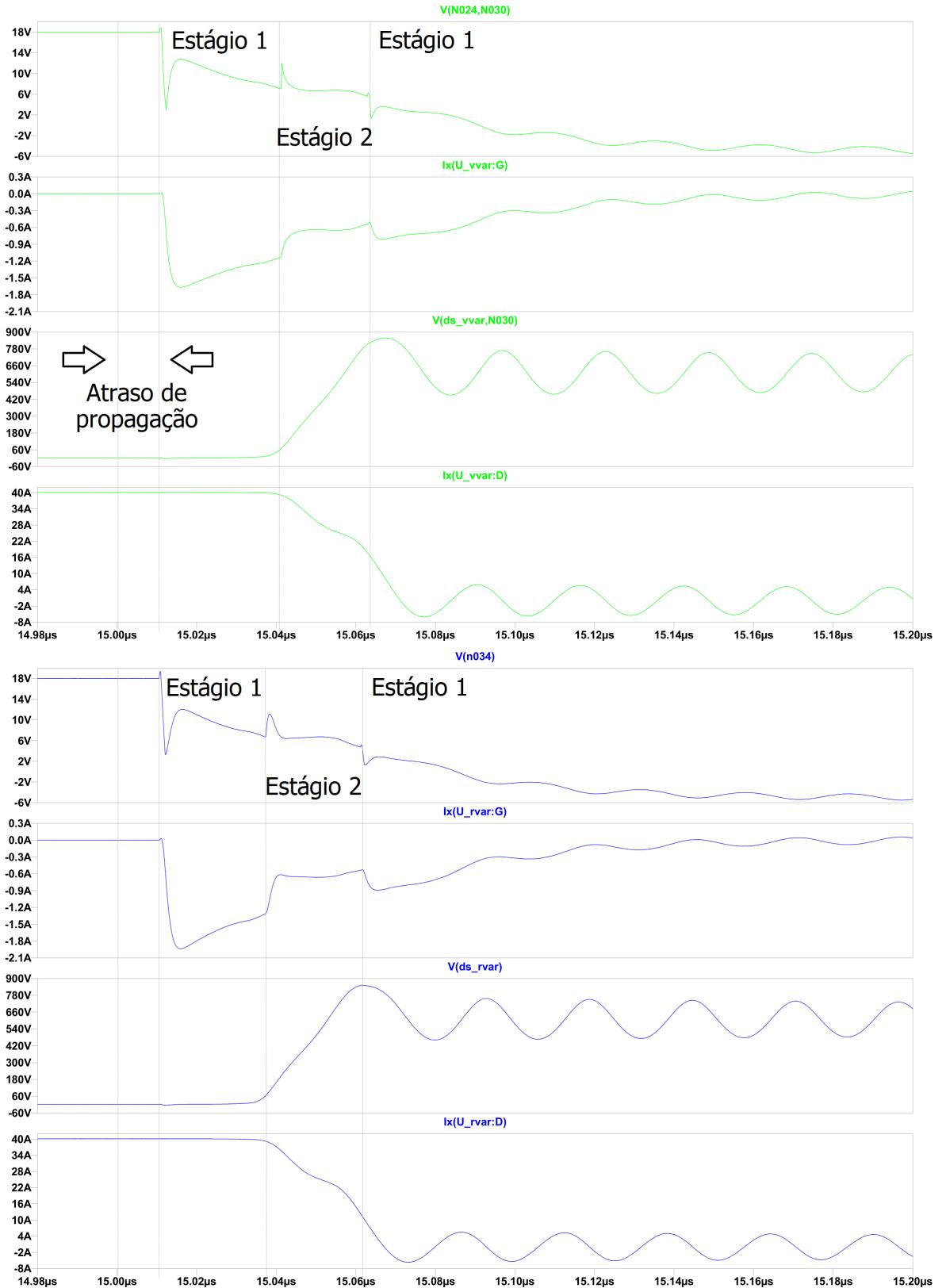

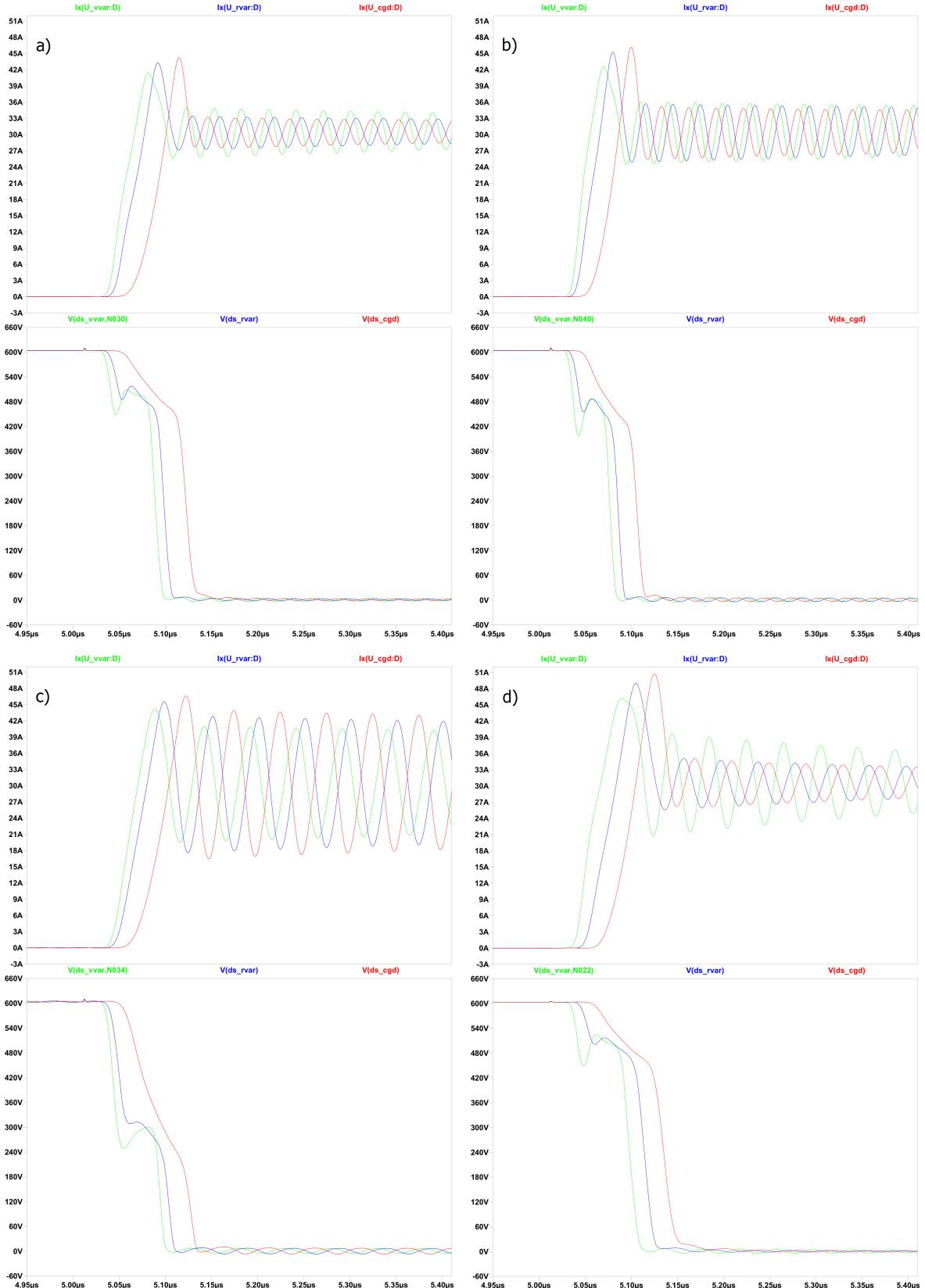

Nas figuras 22, 23 e 24 é possível visualizar as formas de ondas generalizadas para  $V_{gs}$ ,  $I_g$ ,  $V_{ds}$  e  $I_d$  para os AGD e também para o CGD, utilizando os circuitos parametrizados em  $R_g = 10\Omega$ . Nas imagens foram destacadas as trocas de estágio e o atraso de propagação do CI, que se manteve em aproximadamente 10ns.

O comportamento dos circuitos é de acordo com o esperado, sendo possível de se observar, principalmente em  $I_g$ , a troca de estágios dos AGDs e a semelhança entre os métodos, que buscam atingir o mesmo resultado porém com princípios diferentes. Os desempenhos dos *drivers* serão analisados e comparados a seguir.

Figura 22 – Formas de ondas no acionamento de  $V_{gs}$ ,  $I_g$ ,  $V_{ds}$  e  $I_d$  (cima para baixo) para os AGDs de tensão variável (verde) e resistência variável (azul).  $R_g = 10\Omega$  e  $L_{loop} = 100nH$ .

Figura 23 – Formas de ondas no desligamento de  $V_{gs}$ ,  $I_g$ ,  $V_{ds}$  e  $I_d$  (cima para baixo) para os AGDs de tensão variável (verde) e resistência variável (azul).  $R_g = 10\Omega$  e  $L_{loop} = 100nH$ .

Figura 24 – Formas de ondas de  $V_{gs}$ ,  $I_g$ ,  $V_{ds}$  e  $I_d$  (cima para baixo) para o CGD. Esquerda: açãoamento. Direita: desligamento.  $R_{g,vvar} = 10\Omega$  e  $L_{loop} = 100nH$ .

#### 4.2.1 Desempenho no açãoamento

Os circuitos foram simulados nas quatro situações, que tiveram suas perdas energéticas de a) 0.655mJ, b) 0.550mJ, c) 0.410mJ e d) 0.890mJ. As resistências de *gate* do AGD de resistência variável e do CGD foram ajustadas para que suas perdas se igualassem a esses valores. Foram coletados os dados de atraso de chaveamento e de sobressinal de  $I_d$ , visando-se avaliar o desempenho de cada topologia em cada situação. Os dados e as formas de ondas comparativas podem ser vistas logo abaixo na tabela 2 e na figura 25.

Tabela 2 – Desempenho das topologias no açãoamento.

| Teste                   | Atraso de chaveamento (ns) | Sobressinal de $I_d$ (A) | Sobressinal de $I_d$ (%) |

|-------------------------|----------------------------|--------------------------|--------------------------|

| a) tensão variável      | 66.5                       | 41.408                   | 38.03                    |

| a) resistência variável | 77                         | 43.307                   | 44.36                    |

| a) convencional         | 100.5                      | 44.237                   | 47.46                    |

| b) tensão variável      | 55                         | 42.563                   | 41.88                    |

| b) resistência variável | 65.5                       | 45.267                   | 50.89                    |

| b) convencional         | 86                         | 46.155                   | 53.85                    |

| c) tensão variável      | 60                         | 44.190                   | 47.30                    |

| c) resistência variável | 80                         | 45.552                   | 51.84                    |

| c) convencional         | 103.5                      | 46.618                   | 55.39                    |

| d) tensão variável      | 66                         | 46.197                   | 53.99                    |

| d) resistência variável | 83                         | 48.983                   | 63.28                    |

| d) convencional         | 104                        | 50.723                   | 69.08                    |

Figura 25 – Formas de ondas de  $I_d$  e  $V_{ds}$  no acionamento para o AGDs de tensão variável (verde), de resistência variável (azul) e o CGD (vermelho). MOSFET NXP: a)  $R_g = 10\Omega$  e  $L_{loop} = 100nH$ . b)  $R_g = 7.5\Omega$  e  $L_{loop} = 100nH$ . c)  $R_g = 10\Omega$  e  $L_{loop} = 300nH$ . MOSFET Microchip: d)  $R_g = 10\Omega$  e  $L_{loop} = 100nH$ .

Como pode ser visto acima, o desempenho do AGD de tensão variável se mostra superior em questão de atraso e sobressinais, com o CGD possuindo a pior performance e o AGD de resistência variável tendo um bom desempenho em atraso e sendo mediano em questão de sobressinal.

Ao mesmo tempo, no entanto, o AGD de tensão variável não suprime oscilações tão bem quanto os demais em situações de menores indutâncias parasitas [a), b) e d)], porém sendo superior quando  $L_{loop} = 300nH$ , indicando que talvez ele seja mais adequado em situações reais com mais ruídos presentes. O AGD de resistência variável apresenta desempenho similar a ligeiramente superior ao CGD quando o quesito é supressão de oscilações.

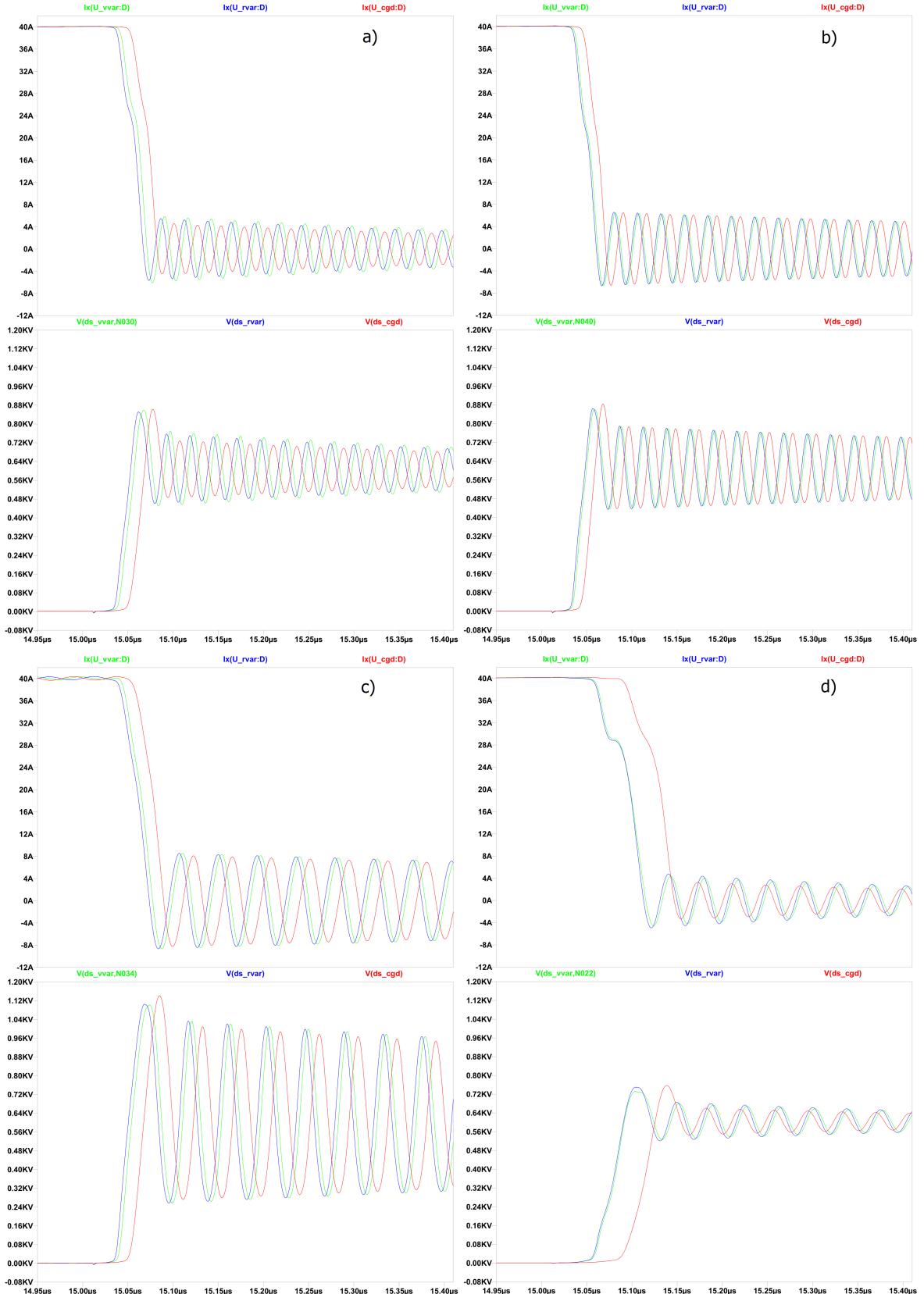

#### 4.2.2 Desempenho no desligamento

Os mesmos procedimentos do acionamento foram realizados no desligamento, e foram obtidas as perdas energéticas de a) 0.300mJ, b) 0.240mJ, c) 0.455mJ e d) 0.495mJ. Os dados coletados podem ser vistos na tabela 3 e na figura 26.

Para o desligamento, o AGD de resistência variável leva a vantagem sobre os demais em atraso e sobressinal, porém com menor discrepância entre o segundo colocado, que é o AGD de tensão variável, com quase o mesmo desempenho. O CGD possui um sobressinal não muito distante dos AGDs, porém conta com um grande atraso.

Porém, o CGD se mostra superior em supressão de oscilações nos testes com o transístor da *NXP*, com o AGD de tensão variável novamente se saindo melhor na situação de maior indutância parasita e pior quando  $L_{loop}$  é baixo. Para o teste d) os resultados se invertem, com o AGD de tensão variável sendo superior e o CGD em último, mostrando a influência das características dinâmicas do semicondutor na ação do *driver*.

Tabela 3 – Desempenho das topologias no desligamento.

| Teste                   | Atraso de chaveamento (ns) | Sobressinal de $V_{ds}$ (V) | Sobressinal de $V_{ds}$ (%) |

|-------------------------|----------------------------|-----------------------------|-----------------------------|

| a) tensão variável      | 71                         | 858.29                      | 43.05                       |

| a) resistência variável | 67                         | 851.74                      | 41.96                       |

| a) convencional         | 82                         | 862.73                      | 43.79                       |

| b) tensão variável      | 62                         | 859.99                      | 43.33                       |

| b) resistência variável | 60                         | 864.16                      | 44.03                       |

| b) convencional         | 70.5                       | 883.86                      | 47.31                       |

| c) tensão variável      | 77                         | 1101.4                      | 83.57                       |

| c) resistência variável | 73                         | 1105.4                      | 84.23                       |

| c) convencional         | 89                         | 1141.0                      | 90.17                       |

| d) tensão variável      | 115                        | 731.91                      | 21.99                       |

| d) resistência variável | 113                        | 750.02                      | 25.00                       |

| d) convencional         | 147                        | 757.58                      | 26.26                       |