FABIO CORREIA KUNG

KENZO MARCELO OKAMURA

RAFAEL ANICET ZANINI

USBTV:

A TV Digital no seu computador

São Paulo

2007

FABIO CORREIA KUNG

KENZO MARCELO OKAMURA

RAFAEL ANICET ZANINI

**USBTv:

A TV Digital no seu computador**

Monografia apresentada à Escola

Politécnica da Universidade de São

Paulo para obtenção do título de

Bacharel em Engenharia.

Área de Concentração:

Engenharia de Computação

São Paulo

2007

FABIO CORREIA KUNG

KENZO MARCELO OKAMURA

RAFAEL ANICET ZANINI

**USBTv:

A TV Digital no seu computador**

Monografia apresentada à Escola

Politécnica da Universidade de São

Paulo para obtenção do título de

Bacharel em Engenharia.

Área de Concentração:

Engenharia de Computação

Orientador: Prof. Dr. Moacyr Martucci

Junior

São Paulo

2007

*Às nossas famílias e companheiras,

pelo apoio e compreensão em mais

uma etapa de nossas vidas. Aos

mestres, pelo conhecimento e pela

inspiração em nossos caminhos.*

"Pequenas oportunidades são muitas vezes o começo de grandes empreendimentos."

---

Demóstenes

Político e pensador grego

(384 a.C. - 322 a.C)

## **Resumo**

A TV digital desempenhará papel importante no processo de inclusão digital previsto pelo Governo Brasileiro. Com o intuito de contribuir para o desenvolvimento da mesma no país, este trabalho apresenta a especificação e implementação de um dispositivo de captura de TV digital via USB. São detalhados os requisitos técnicos e escolhas de projeto realizadas para a implementação do dispositivo, que foi baseado em um kit de desenvolvimento USB com uma FPGA como unidade de tratamento e processamento de sinais. O dispositivo opera em diferentes sistemas operacionais, uma vez que a portabilidade é um dos objetivos deste trabalho. Os resultados são apresentados através de aplicações que realizam a reprodução dos vídeos no computador e também sua gravação em dispositivos de armazenamento. O trabalho aborda também a integração do dispositivo ao padrão brasileiro de TV Digital, além de analisar e caracterizar os diferentes tipos de aplicações e níveis de interatividade possíveis de serem utilizados com o middleware brasileiro Ginga. Por fim, são discutidas e propostas algumas aplicações interativas que utilizam a conexão normal à Internet como canal de interatividade, expandindo assim a usabilidade dos serviços disponíveis na Internet para as aplicações de TV digital, agregando maior valor às aplicações interativas possíveis de serem desenvolvidas.

Palavras-chave: Engenharia. Engenharia da Computação. TV Digital. USB. Canal de Retorno.

## **Abstract**

The Digital TV has appeared as the new paradigm for interaction between viewers and TV shows. Its development in the country also represents the great effort the Brazilian government has shown for digital inclusion. The aim of this project is to specify and develop a portable device for Digital TV signal capturing through the USB protocol. The technical requirements and project specifications are detailed through this paper, which includes the complete description of the necessary steps for developing the device. It is based on an USB development kit, which counts on an FPGA for dealing and processing of the digital signals. The device can be used on several operating systems, which guarantees the portability desired for this project. The main results are shown through example applications that use the device as main source for displaying and recording video streams, delivered by a transport stream generator device. This paper also describes the use of the device with the Brazilian Digital TV standard (SBTVD), besides analyzing different kinds of interactivity possible to exist on Digital TV applications running over the Brazilian middleware Ginga. In conclusion, this paper presents and discusses new applications that may use an existing connection to the Internet as the return channel, bringing the services already available on the Internet to the Digital TV world and expanding their functional capabilities and visual appeal.

**Keywords:** Engineering. Computer Engineering. Digital TV. USB. Return Channel.

# **Lista de Figuras**

|      |                                                                               |    |

|------|-------------------------------------------------------------------------------|----|

| 2.1  | <i>Quadro resumo para o plano de transição da TV Digital no Brasil</i>        | 7  |

| 2.2  | <i>Sensibilidade da evolução do preço ao preço inicial</i>                    | 8  |

| 2.3  | <i>Sensibilidade da difusão segundo o preço inicial do terminal de acesso</i> | 8  |

| 3.1  | <i>Diagrama de blocos da aplicação principal</i>                              | 13 |

| 3.2  | <i>Diagrama de blocos do hardware completo para a aquisição do sinal</i>      | 14 |

| 3.3  | <i>Processo de simplificação para este projeto</i>                            | 15 |

| 3.4  | <i>Parte do cabeçalho dos pacotes</i>                                         | 17 |

| 3.5  | <i>Diagrama do Canal de Interatividade</i>                                    | 20 |

| 3.6  | <i>Aplicação SMS utilizando interatividade intermitente.</i>                  | 22 |

| 3.7  | <i>Aplicação de e-mail com interatividade permanente.</i>                     | 23 |

| 4.1  | <i>Descrição da metodologia de desenvolvimento ágil Scrum</i>                 | 29 |

| 5.1  | <i>Visão geral da arquitetura do dispositivo USB</i>                          | 31 |

| 5.2  | <i>Topologia da arquitetura USB</i>                                           | 32 |

| 5.3  | <i>Gerador de TS da Rohde &amp; Schwarz com interface SPI</i>                 | 34 |

| 5.4  | <i>Camadas da interface ASI</i>                                               | 35 |

| 5.5  | <i>Interface de transmissão paralela (SPI)</i>                                | 36 |

| 5.6  | <i>Formato de transmissão de pacotes de 188 bytes</i>                         | 36 |

| 5.7  | <i>Interconexão entre transmissor e receptor dos sinais</i>                   | 37 |

| 5.8  | <i>Geração de sinal lógico a partir dos sinais analógicos</i>                 | 37 |

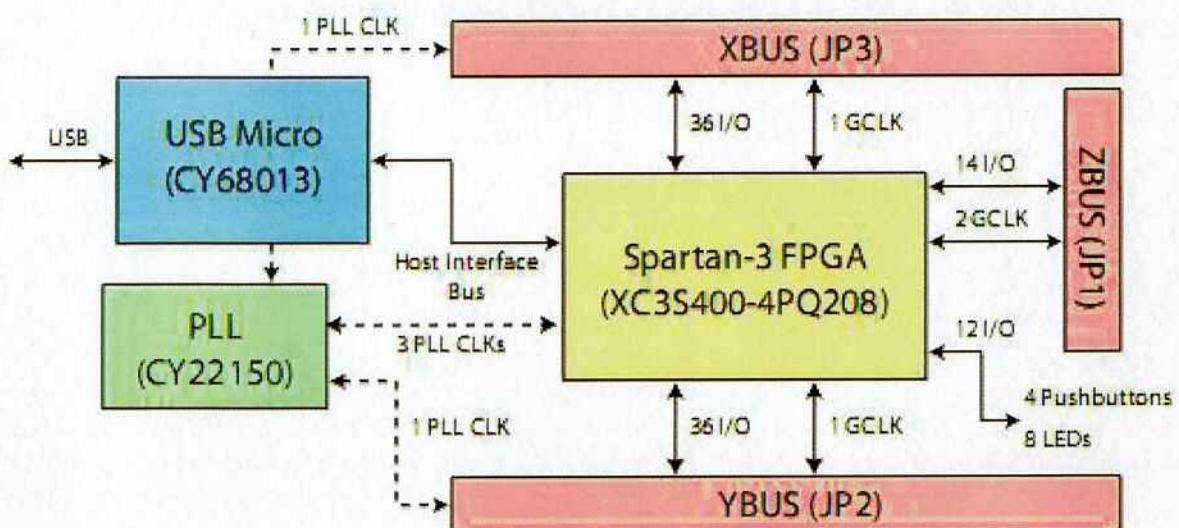

| 5.9  | <i>Kit de Desenvolvimento XEM3001 da Opal Kelly</i>                           | 39 |

| 5.10 | <i>Diagrama dos blocos funcionais do Kit de Desenvolvimento XEM3001</i>       | 39 |

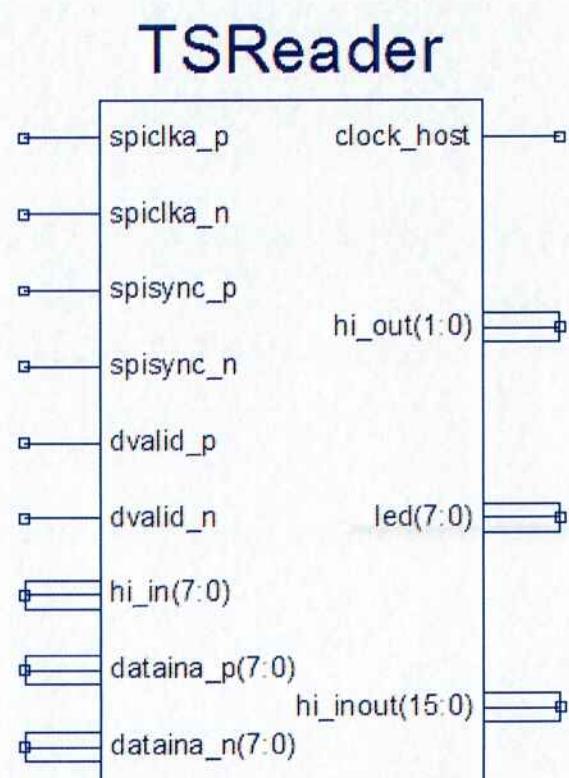

| 5.11 | <i>Visão geral da arquitetura lógica desenvolvida em VHDL</i>                 | 41 |

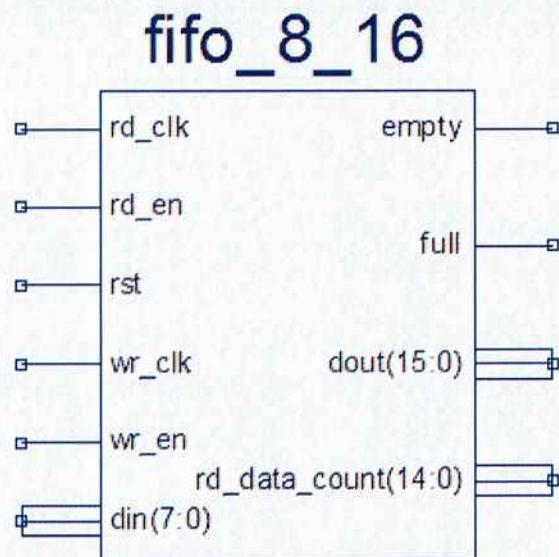

| 5.12 | <i>Diagrama lógico da unidade FIFO desenvolvida</i>                           | 43 |

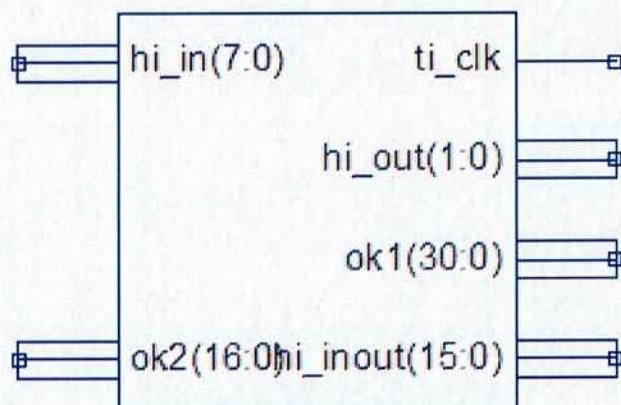

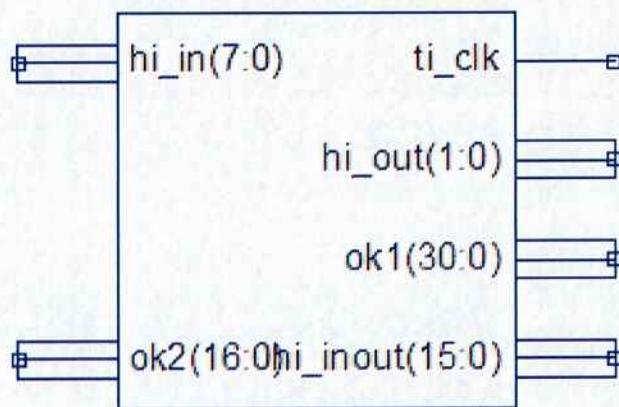

| 5.13 | <i>Diagrama lógico do módulo de interface com o controlador USB</i>           | 44 |

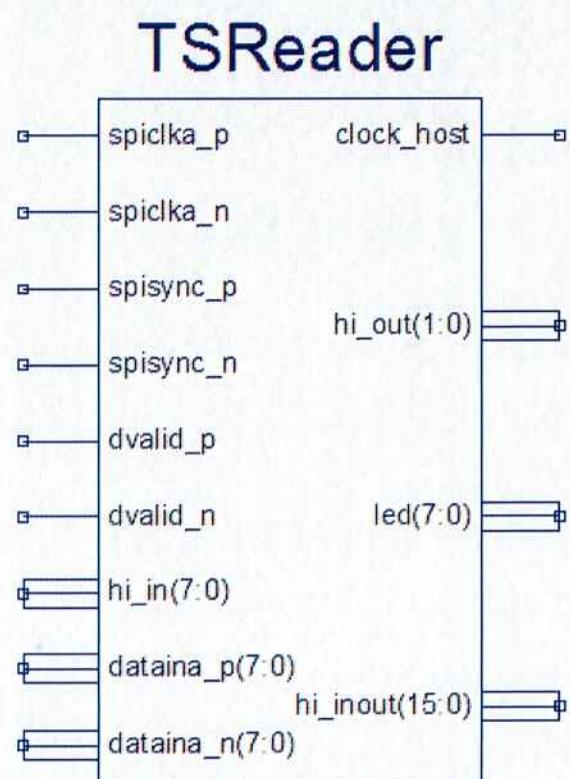

| 5.14 | <i>Diagrama lógico do principal módulo do dispositivo</i>                     | 46 |

| 5.15 | <i>Requisição de bytes ao FIFO pelo programa cliente</i>                      | 48 |

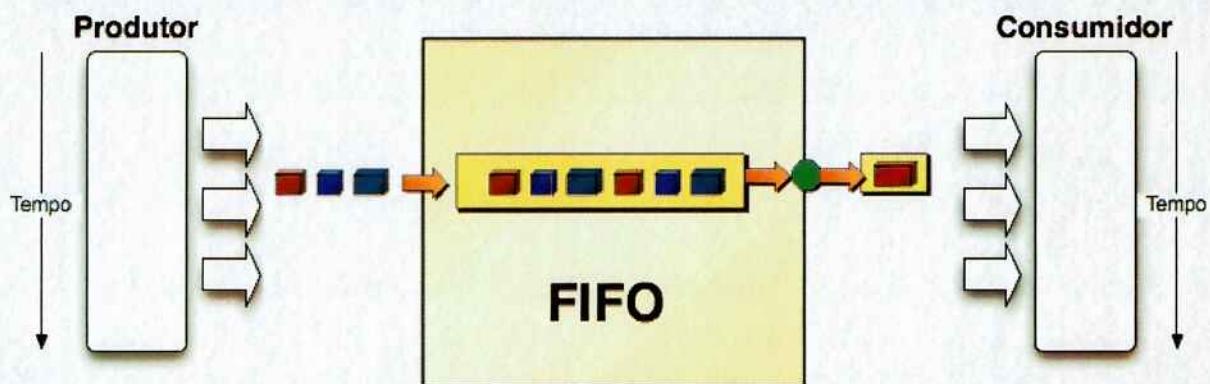

| 5.16 | <i>Duas threads (produtora e consumidora) manipulando o buffer</i>            | 48 |

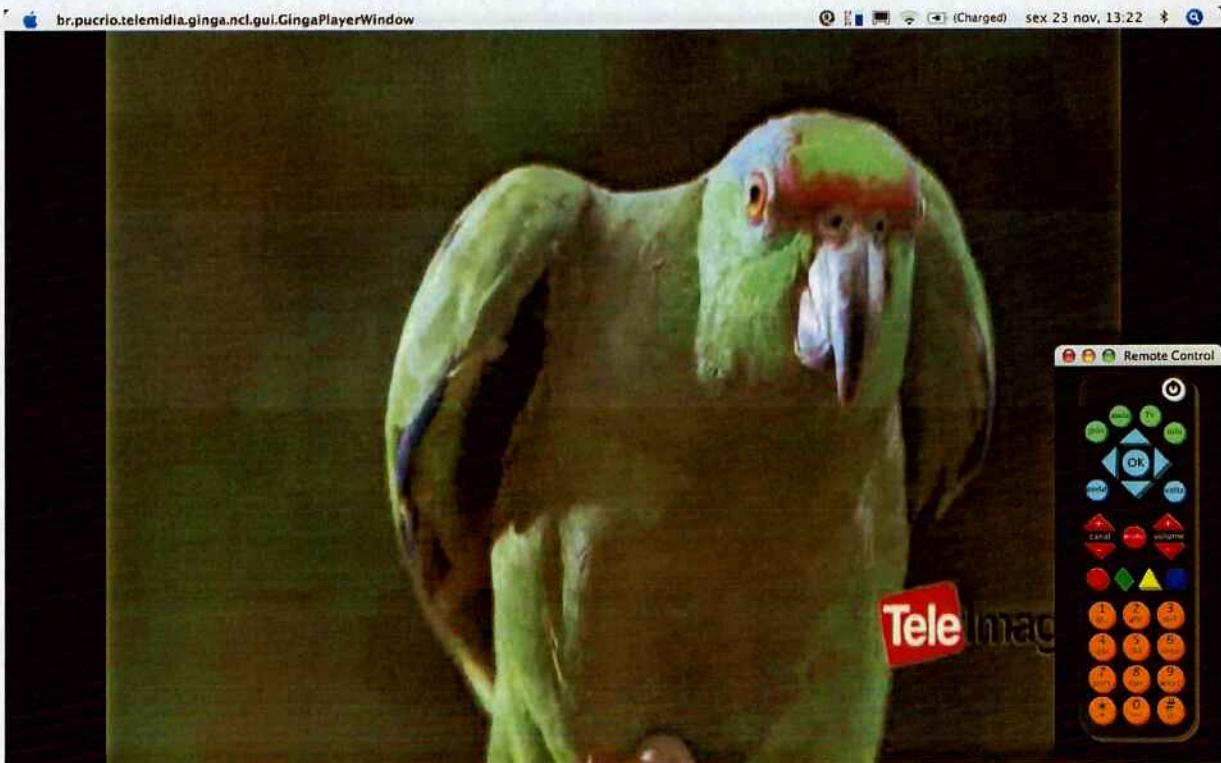

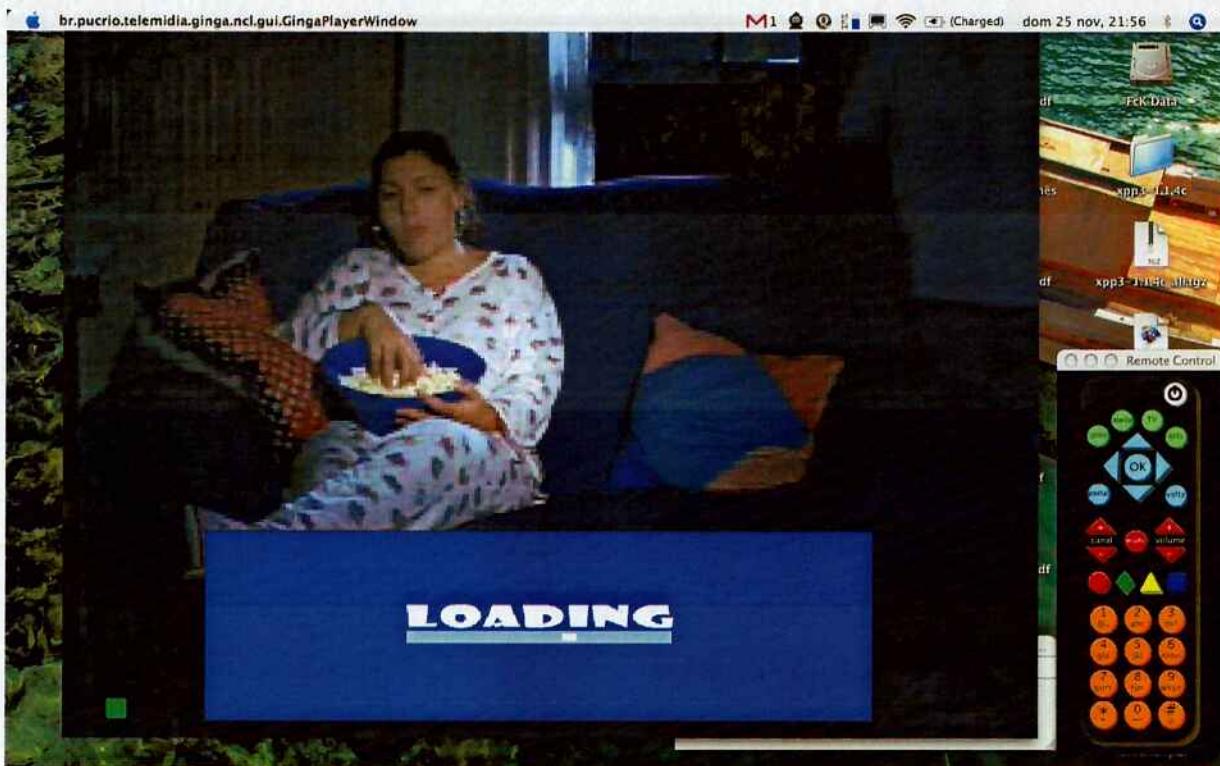

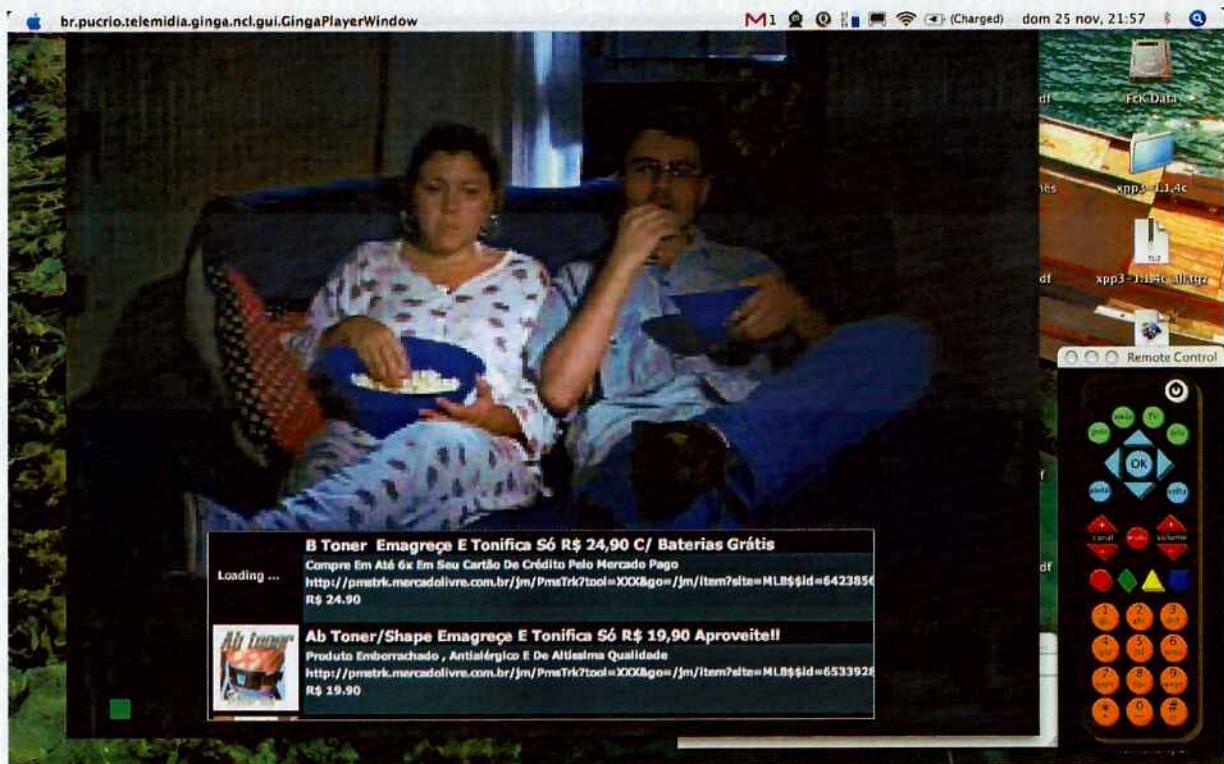

| 5.17 | <i>Reprodução de um Transport Stream lido através do USBTv no Ginga</i>       | 51 |

| 5.18 | <i>Definição de mídia video/mpeg-ts em NCL para ser reproduzida com o VLC</i> | 52 |

| 5.19 | <i>Definição de mídia video/usbtv em NCL</i>                                  | 52 |

| 5.20 | <i>O popular jogo Space Invaders</i>                                          | 53 |

| 5.21 | <i>Exemplo de uso de classes Java em um documento NCL</i>                     | 54 |

|      |                                                                                          |    |

|------|------------------------------------------------------------------------------------------|----|

| 5.22 | <i>Expondo métodos da classe como propriedades em um documento NCL . . . . .</i>         | 54 |

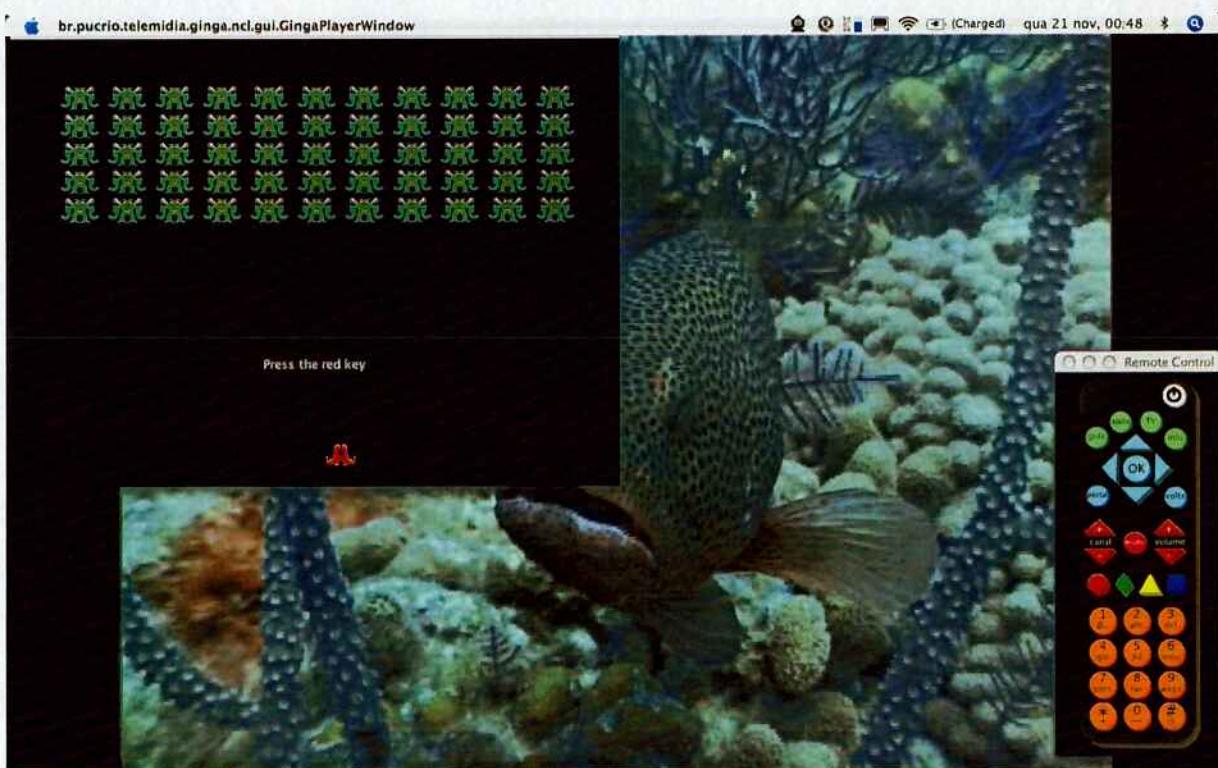

| 5.23 | <i>Space Invaders rodando no Ginga, junto com a exibição de um TS . . . . .</i>          | 55 |

| 5.24 | <i>Produtos relacionados a emagrecimento, em um filme sobre obesidade . . . . .</i>      | 56 |

| 5.25 | <i>Dados sendo carregados de forma assíncrona . . . . .</i>                              | 58 |

| 5.26 | <i>Imagens sendo carregadas pouco a pouco por threads separadas . . . . .</i>            | 59 |

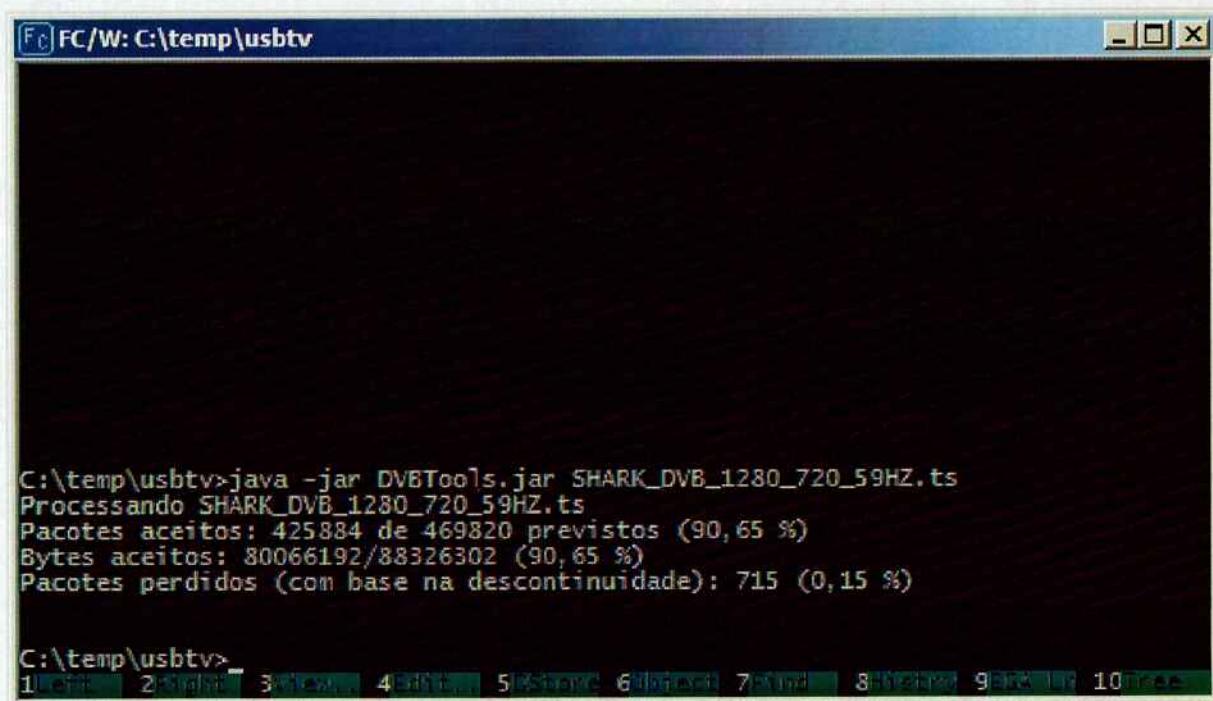

| 6.1  | <i>Arquivos de Transport Streams utilizados nos testes . . . . .</i>                     | 60 |

| 6.2  | <i>Resultado dos testes efetuados . . . . .</i>                                          | 61 |

| 6.3  | <i>Aplicação desenvolvida para efetuar testes nos vídeos amostrados . . . . .</i>        | 62 |

| A.1  | <i>Inicialização e configuração dinâmica do dispositivo via software . . . . .</i>       | 77 |

| A.2  | <i>Seqüência de chamadas à API para leitura de dados do dispositivo . . . . .</i>        | 78 |

| B.1  | <i>Configuração dos 25 pinos do conector D-subminiatura na interface SPI . . . . .</i>   | 84 |

| B.2  | <i>Relação entre os pinos da FPGA e do kit de desenvolvimento . . . . .</i>              | 85 |

| B.3  | <i>Relação entre os fios do conector SPI e pinos do kit de desenvolvimento . . . . .</i> | 85 |

# Sumário

|                                                                       |           |

|-----------------------------------------------------------------------|-----------|

| <b>1 INTRODUÇÃO</b>                                                   | <b>1</b>  |

| 1.1 Objetivo . . . . .                                                | 1         |

| 1.2 Motivação . . . . .                                               | 1         |

| 1.3 Escopo . . . . .                                                  | 2         |

| 1.4 Organização . . . . .                                             | 3         |

| <b>2 ASPECTOS CONCEITUAIS</b>                                         | <b>5</b>  |

| 2.1 O Ambiente . . . . .                                              | 5         |

| 2.1.1 Cenário . . . . .                                               | 5         |

| 2.1.2 Plano de Transição . . . . .                                    | 6         |

| 2.1.3 Terminal de Acesso ( <i>set-top box</i> ) . . . . .             | 6         |

| 2.1.4 Modelo de Serviços . . . . .                                    | 8         |

| 2.1.5 Serviços Interativos . . . . .                                  | 9         |

| 2.1.6 Plataforma brasileira para interatividade (Ginga) . . . . .     | 10        |

| 2.2 Equipamento Utilizado . . . . .                                   | 10        |

| <b>3 ESPECIFICAÇÃO DO PROJETO</b>                                     | <b>13</b> |

| 3.1 Funcionalidades principais . . . . .                              | 13        |

| 3.2 Conexão USB . . . . .                                             | 13        |

| 3.2.1 Software . . . . .                                              | 13        |

| 3.2.2 Hardware . . . . .                                              | 14        |

| 3.3 Formato dos dados . . . . .                                       | 15        |

| 3.3.1 O padrão MPEG-2 . . . . .                                       | 16        |

| 3.3.2 Conteúdo como fluxo de dados: MPEG-2 Transport Stream . . . . . | 17        |

| 3.4 Middleware . . . . .                                              | 18        |

| 3.5 Canal de retorno . . . . .                                        | 20        |

| 3.5.1 Conceito . . . . .                                              | 20        |

| 3.5.2 Aplicações . . . . .                                            | 21        |

| 3.5.3 Implementação . . . . .                                         | 23        |

| 3.6 Planejamento e Métodos . . . . .                                  | 24        |

| 3.6.1 TV Digital e Middleware . . . . .                               | 24        |

| 3.6.2 Captura do Sinal via USB . . . . .                              | 25        |

| 3.6.3 Canal de Retorno pela Internet . . . . .                        | 26        |

|                                                  |           |

|--------------------------------------------------|-----------|

| <b>4 METODOLOGIA</b>                             | <b>28</b> |

| 4.1 Metodologia Ágil . . . . .                   | 28        |

| 4.2 Desenvolvimento do Hardware . . . . .        | 29        |

| <b>5 PROJETO E IMPLEMENTAÇÃO</b>                 | <b>31</b> |

| 5.1 Dispositivo USB . . . . .                    | 31        |

| 5.1.1 Arquitetura USB . . . . .                  | 32        |

| 5.1.2 Gerador de Transport Stream . . . . .      | 33        |

| 5.1.3 Interfaces e Padrões . . . . .             | 34        |

| 5.1.4 Kit de Desenvolvimento . . . . .           | 38        |

| 5.1.5 Implementação VHDL . . . . .               | 40        |

| 5.2 Lendo os dados do dispositivo USB . . . . .  | 47        |

| 5.3 Demultiplexação e decodificação . . . . .    | 49        |

| 5.4 Adequando ao Ginga . . . . .                 | 51        |

| 5.5 Aplicação com Interatividade Local . . . . . | 53        |

| 5.6 Uso do canal de retorno . . . . .            | 55        |

| <b>6 TESTES E AVALIAÇÃO</b>                      | <b>60</b> |

| 6.1 Hardware . . . . .                           | 60        |

| 6.2 Aplicação com Interatividade Local . . . . . | 62        |

| 6.3 Aplicação com Canal de Retorno . . . . .     | 63        |

| <b>7 CONSIDERAÇÕES FINAIS</b>                    | <b>64</b> |

| 7.1 Análise dos Resultados . . . . .             | 64        |

| 7.2 Trabalhos Futuros . . . . .                  | 65        |

| <b>Referências Bibliográficas</b>                | <b>67</b> |

| <b>Glossário</b>                                 | <b>71</b> |

| <b>Apêndice</b>                                  | <b>76</b> |

| <b>A API FrontPanel</b>                          | <b>76</b> |

| A.1 Utilização da API . . . . .                  | 76        |

| A.2 Overview . . . . .                           | 78        |

| <b>B Pinagem</b>                                 | <b>83</b> |

| B.1 Conector SPI . . . . .                       | 83        |

|     |                                         |    |

|-----|-----------------------------------------|----|

| B.2 | FPGA e Kit de Desenvolvimento . . . . . | 84 |

|-----|-----------------------------------------|----|

## Capítulo 1

# INTRODUÇÃO

### 1.1 Objetivo

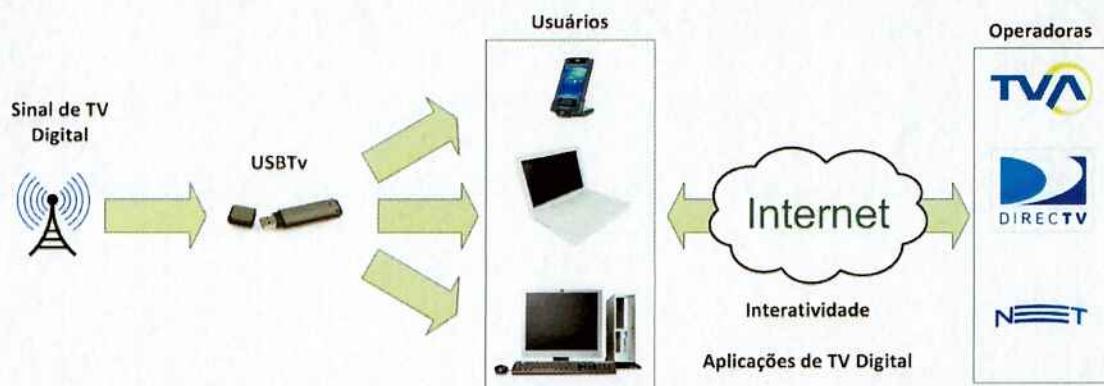

O objetivo principal deste projeto é criar um dispositivo que possibilite a captura de sinais de vídeo digital pelo computador através da interface USB e permita assistir à programação de forma interativa através do envio de dados por um canal de retorno implementado por uma conexão comum à Internet, dando suporte aos padrões brasileiros de TV digital e incentivando o desenvolvimento de novas tecnologias puramente nacionais.

### 1.2 Motivação

A TV Digital desempenhará em breve um dos principais papéis na difusão de informação, conteúdo e conhecimento, além de entretenimento. A convergência tecnológica percebida nos dias atuais cria demanda para a integração entre esse mundo de conteúdo digital e o principal instrumento de manipulação de informação: o computador. Neste contexto, tornam-se necessárias alternativas para a captura do sinal de TV Digital pelo computador, tanto como forma de facilitar a inclusão dos telespectadores neste novo sistema de TV, quanto melhorar a experiência de usuário. O perfil brasileiro dá preferência a alternativas simples e baratas, que acabam tendo um maior alcance.

Uma vez que o computador oferece uma ótima plataforma para desenvolvimento, o projeto também possibilita que aplicações possam ser construídas oferecendo a infraestrutura e a interatividade para que se beneficiem do sinal de TV Digital na sua totalidade.

Embora a interatividade seja uma das metas da implantação da TV Digital no Brasil, o funcionamento do canal de retorno de dados, essencial para a sua existência - pois é por esse canal que trafegam os dados do usuário - ainda não está adequadamente adaptado para o público brasileiro. Na Europa utiliza-se a transmissão por GSM, que em princípio não tem apelo comercial por tornar mais caro quanto maior a sua utilização. De fato, poucas pessoas utilizam a rede celular como forma de transmissão de dados. A transmissão dos dados pela Internet já está prevista em todos os padrões de TV Digital, porém muito pouco explorada. Deste modo, a criação de uma estrutura alternativa para a implementação deste canal de retorno é altamente justificável, e para tal, a proposta deste

projeto é o desenvolvimento desta através de uma conexão comum à Internet, seja ela por linha discada, banda larga, ou comunicação wireless (Wi-Fi ou WiMax).

Disponibilizar o sinal de TV Digital para o computador abre inúmeras portas para aplicações, manipulação e tratamento deste. Como alguns exemplos podem ser citados a gravação agendada de programas, a conversão para diversos formatos de vídeo (WMV, DivX, XViD, Mov, entre outros), a transmissão do vídeo on-line - via Internet, armazenamento dada a crescente capacidade dos discos rígidos em computadores pessoais, facilidade para criação de multimídia (CDs, DVDs). É importante novamente ressaltar que dispor o sinal de TV Digital aos computadores facilita a criação de plataformas de desenvolvimento para conteúdo interativo destinado a TV Digital.

### 1.3 Escopo

O projeto teve início em Janeiro de 2007 e a idéia inicial envolvia a captura de sinais analógicos de TV aberta através de uma interface USB, para a visualização da programação comum de TV no computador. O projeto evoluiu após a identificação da crescente demanda por tecnologia envolvendo TV Digital. Assim, o foco do projeto foi redirecionado para a implementação do canal de interatividade pela Internet. Este projeto desencadeou uma pesquisa profunda sobre as tecnologias atualmente existentes e toda a polêmica sobre o assunto no Brasil.

O grupo percebeu que o assunto tomava volume ao longo do ano, e que diversas equipes espalhadas pelo país estavam apostando em pesquisa e desenvolvimento técnico na área. A oportunidade de contribuir para a especificação do padrão brasileiro também incentivou o grupo a continuar o seu trabalho e a envolver-se cada vez mais nas pesquisas de TV Digital.

Com o projeto já direcionado à TV Digital, foi prevista a implementação de um receptor, sintonizador e decodificador de sinal de TV Digital para a sua captura através do dispositivo USB. Devido ao tempo e recursos limitados para a realização do projeto, houve uma redução nas características funcionais.

O projeto é caracterizado por dois grandes blocos. O primeiro deles trata mais do hardware e provê um dispositivo USB responsável pela captura do fluxo de vídeo, som e dados multiplexados no padrão MPEG-2 Transport Stream. O MPEG-2 é a tecnologia de codificação do vídeo adotada pelos três principais padrões de TV Digital: o DVB (europeu), o ATSC (americano) e o ISDB (japonês). O padrão brasileiro, conhecido como Sistema Brasileiro de TV Digital (SBTVD), definiu a adoção de uma tecnologia mais atual para a

codificação do vídeo, o MPEG-4, que é totalmente compatível com o MPEG-2 e considerado a sua evolução já que permite maior compressão. Para o transporte dos dados, o padrão adotado no Brasil continua sendo o MPEG2 Transport Stream. Por basear-se no padrão MPEG-2 Transport Stream, o projeto torna-se independente do padrão de transmissão utilizado.

O segundo bloco está relacionado ao software necessário, responsável pela leitura do fluxo MPEG-2 através da interface USB, pela apresentação do vídeo e som e pela execução de aplicativos para a TV Digital. O ambiente de execução de aplicativos é conhecido como *middleware* e deverá possibilitar a implementação de um canal de retorno através da conexão disponível com a Internet, seja ela uma conexão discada, banda larga, sem fio ou qualquer outra.

O foco do projeto é a pesquisa e desenvolvimento de uma infra-estrutura completa para a implementação do *middleware* que possibilite o canal de retorno através da Internet. Isto inclui as funcionalidades do lado cliente e do lado servidor, além da definição de padrões, estrutura e protocolos de comunicação utilizados. Este *middleware* também possibilita a criação de um poderoso ambiente de desenvolvimento, já que aplicações poderão ser desenvolvidas e testadas na mesma plataforma – o computador.

É importante enfatizar a possibilidade de expansão das funcionalidades, uma vez que o projeto visa ser independente de tecnologias de transmissão, recepção e decodificação do sinal de TV Digital. Desta forma, tantos os padrões europeus, americanos, japoneses e brasileiros poderão tirar proveito dos resultados obtidos neste trabalho.

## 1.4 Organização

O presente documento está dividido nas seguintes seções:

- Capítulo 2 - Aspectos Conceituais: são definidos os conceitos básicos a serem discutidos ao longo de todo o documento, o cenário atual da TV Digital no país, o estado da arte da tecnologia existente e os equipamentos utilizados durante a concepção do projeto;

- Capítulo 3 - Especificação do Projeto: nesta seção são definidos todos os requisitos necessários para o projeto, bem como o impacto destes na definição do escopo do projeto. São levantadas as características técnicas dos equipamentos e padrões que serão estudados e utilizados ao longo do projeto;

- Capítulo 4 - Metodologia: este capítulo descreve os principais métodos e técnicas utilizadas para a implementação do projeto baseado nos requisitos levantados previamente;

- Capítulo 5 - Projeto e Implementação: este capítulo descreve todas as atividades, especificações técnicas e componentes de hardware e software que foram desenvolvidos para a implementação do projeto;

- Capítulo 6 - Testes e Avaliação: este capítulo descreve os principais testes executados para a validação das funcionalidades do dispositivo USB e do software implementado, bem como a avaliação dos resultados obtidos;

- Capítulo 7 - Considerações finais: este capítulo avalia os resultados globais do projeto, analisando as dificuldades e aspectos positivos do projeto, além de ressaltar os projetos futuros que poderão se basear no presente projeto;

- Apêndice A - API FrontPanel: este apêndice relata o uso da API do kit de desenvolvimento, bem como apresenta um overview da API utilizada;

- Apêndice B - Pinagem: este apêndice relata a configuração de pinos e conexões utilizada ao longo da implementação do dispositivo USB;

## Capítulo 2

# ASPECTOS CONCEITUAIS

### 2.1 O Ambiente

#### 2.1.1 Cenário

Iniciado em 2003 e coordenado pelo Centro de Pesquisa e Desenvolvimento em Telecomunicações (CPqD), o comitê do Sistema Brasileiro de Televisão Digital (SBTVD) foi responsável pelos estudos que definiriam o padrão a ser adotado no país. Após estudos conduzidos juntamente com universidades e companhias de comunicação, em 13 de novembro de 2005 o sistema foi apresentado pelo presente Ministro das Comunicações Hélio Costa. O sistema resultante dos estudos foi baseado no sistema ISDB-T utilizado no Japão, porém com a adição de padrões desenvolvidos no país que deveriam proporcionar alta definição e interatividade segundo as diretrivas do governo.

A definição do padrão brasileiro de TV Digital e o forte compromisso do governo e de instituições privadas levam a crer que a TV Digital, incluindo o serviço de interatividade, terá ampla penetração no Brasil. Uma vez instaurados, os serviços de interatividade estarão vinculados a programas de televisão e a publicidade, exigindo assim demanda constante por produção. A eficiência deste processo será fator crítico para a redução de custos de produção e impactará na margem de lucro das produtoras e emissoras.

Todas as expectativas são de forte adoção da TV Digital pelos espectadores (conforme estudo realizado pelo CPqD [1]). A penetração da tecnologia para 2016 está estimada em 40% dos domicílios brasileiros atendidos para o pior caso e 70% de domicílios atendidos no melhor caso. Esta estimativa nem leva em consideração eventos importantes, como as Olimpíadas de 2008 em Pequim, as Eleições de 2010 e principalmente a Copa do Mundo de 2010 na África. Tais eventos têm grande chance de alavancar ainda mais a adoção, já que historicamente sempre foram um incentivo às vendas de televisores (que podem já integrar o set-top box) e ao aumento da demanda por publicidade e propaganda, que certamente serão um atrativo à interatividade. Há ainda a questão do uso da propaganda, que já está sendo utilizada como estratégia de implantação pelo governo e que promete alavancar a difusão da TV Digital trazendo a estimativa (no melhor caso) para 80% dos domicílios atendidos já em 2010.

Além de o cenário ser bastante promissor, estudos mostram que a influência dos novos serviços oferecidos TV Digital para as emissoras e produtoras de conteúdo (principais clientes do produto proposto) é sempre positiva. Especificamente, a interatividade influi positivamente sobre as receitas das emissoras e produtoras de conteúdo.

A TV Digital ainda não é uma realidade no Brasil, uma vez que só existe para assinantes de TV por assinatura. Além disso, a tecnologia utilizada pelas operadoras de TV a cabo é estrangeira, baseada nos padrões europeus de TV Digital (DVB e MHP). O projeto de TV Digital brasileiro incentiva a pesquisa de diferentes setores, tanto no meio acadêmico como no meio privado. Estas pesquisas e incentivos do governo brasileiro permitem a definição de um padrão brasileiro para transmissão e *middleware* para a execução de aplicações sobre conteúdo multimídia.

### **2.1.2 Plano de Transição**

O governo elaborou também um plano de transição que deverá ser cumprido tanto por emissoras comerciais como públicas a fim de organizar e estabelecer um prazo para que a tecnologia de TV Digital seja implantada e esteja disponível para todos os brasileiros.

A Figura 2.1 contém um quadro onde são apresentadas as etapas do cronograma de digitalização para esse plano de transição.

O estado de São Paulo já possui a infra-estrutura e tem início das transmissões do novo padrão marcado para dezembro de 2007. Ao final do processo de transição, em 2013, todo o país terá acesso a TV Digital. Regulamentado pelo governo e também em consequência das perspectivas futuras de mercado, fabricantes de televisão deverão entrar em conformidade com o novo padrão sendo obrigados, também a partir de 2013, a produzir aparelhos seguindo os padrões da TV Digital brasileira.

Até atingir a conformidade com o padrão, o país pretende continuar transmitindo ambos os sinais analógicos e digitais, o chamado *simulcasting*, pelo menos até 2016. Se houver necessidade, o governo prorrogará o prazo de transição.

### **2.1.3 Terminal de Acesso (*set-top box*)**

O usuário deverá possuir um terminal de acesso que será responsável pela recepção e decodificação do sinal para o aparelho televisor. Este equipamento, chamado *set-top box*, inicialmente será vendido como um aparelho externo; os consumidores poderão comprar e utilizar em seus televisores analógicos ou digitais. Porém, a tendência é que, com o tempo, o *set-top box* virá integrado aos novos aparelhos de televisão já adaptados a tecnologia digital.

| Fases | Regiões                                                 | Emissoras                                                                             | Calendário       |

|-------|---------------------------------------------------------|---------------------------------------------------------------------------------------|------------------|

| 1     | As duas maiores Regiões Metropolitanas (RJ e SP)        | 5 maiores emissoras comerciais e a maior emissora pública (e/ou operador(es) de rede) | $T_0 + 6$ meses  |

| 2     | RMs com mais de 2 milhões de habitantes e Brasília      | 5 maiores emissoras comerciais e a maior emissora pública (e/ou operador(es) de rede) | $T_0 + 12$ meses |

| 3     | Demais RMs, capitais e cidades com mais de 300 mil hab. | 5 maiores emissoras comerciais e a maior emissora pública (e/ou operador(es) de rede) | $T_0 + 24$ meses |

| 4     | Cidades com mais de 100 mil habitantes                  | 5 maiores emissoras comerciais e a maior emissora pública (e/ou operador(es) de rede) | $T_0 + 36$ meses |

| 5     | Cidades com mais de 100 mil habitantes                  | Todas as geradoras e retransmissoras (e/ou operador(es) de rede)                      | $T_0 + 48$ meses |

| 6     | Todo o país                                             | Todas as geradoras e retransmissoras (e/ou operador(es) de rede)                      | $T_0 + 72$ meses |

RM - Região Metropolitana

$T_0$  - instante em que as primeiras freqüências são consignadas

Figura 2.1: Quadro resumo para o plano de transição da TV Digital no Brasil

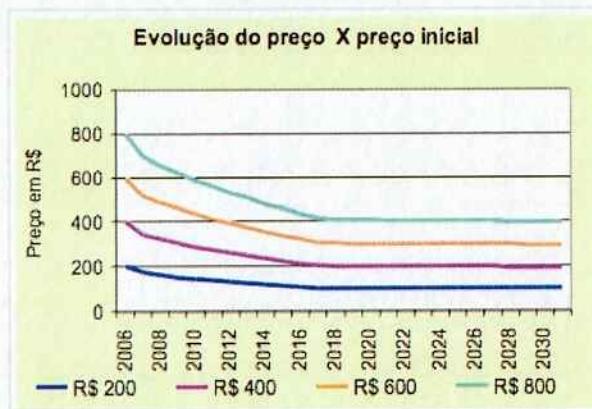

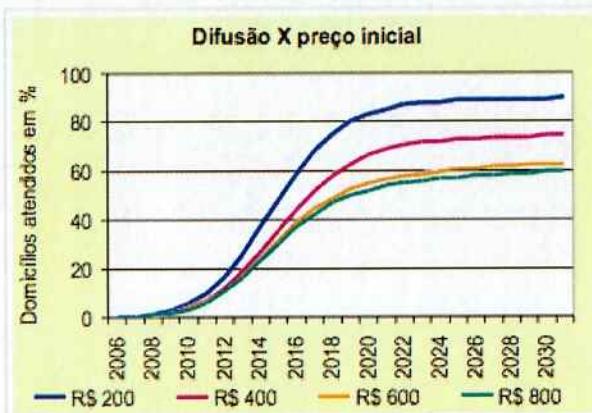

Muito se tem especulado sobre o preço do *set-top box*. Governo e indústria divergem nos valores, porém este deve variar entre R\$ 200 e R\$ 800. Nos gráficos da Figura 2.2 e da Figura 2.3 observa-se o estudo feito pelo CPqD sobre o comportamento de alguns indicadores à variação do preço inicial do terminal de acesso à TV Digital.

Com relação à evolução dos preços, tem-se que quanto maior o preço inicial, maior o preço médio ao longo do período, conforme ilustrado na Figura 2.2. Em todos os casos, o preço cai mais intensamente nos primeiros anos, estabilizando por volta de oito a dez anos após o início da comercialização do terminal de acesso.

Preços mais elevados implicam em um percentual menor de domicílios atendidos, como é mostrado no gráfico da Figura 2.3. O estudo mostra que após 15 anos e com as premissas consideradas, o percentual de domicílios atendidos no caso mais favorável (a R\$ 200) chega a 81%, enquanto que no caso mais desfavorável (a R\$ 800) esse percentual fica em torno de 52%. É importante lembrar que, para efeito de simulação, esses valores foram divididos em 10 parcelas, segundo o procedimento de venda a prazo.

Figura 2.2: Sensibilidade da evolução do preço ao preço inicial

Figura 2.3: Sensibilidade da difusão segundo o preço inicial do terminal de acesso

Pode-se concluir que a longo prazo, mesmo com o preço elevado do terminal de acesso, a difusão da TV Digital será ampla sobre o território brasileiro e substituirá a TV analógica convencional.

#### 2.1.4 Modelo de Serviços

Entende-se por modelo de serviços como o leque de serviços e aplicações de que um sistema de TV digital terrestre pode dispor. Para que tais serviços cheguem ao usuário é necessário que não apenas das tecnologias habilitadoras e de toda infra-estrutura de serviços subjacentes mas também do perfil de demanda dos usuários e da estratégia e capacidade de atendimento dos provedores de serviço (emissoras/programadores e outros agentes associados).

O modelo de serviços é, portanto, um reflexo do quanto será explorado das potencialidades funcionais da TV Digital, ressaltando-se a importância do conteúdo, e de sua

formatação, para que o usuário perceba valor no usufruto da nova tecnologia. Entre os principais serviços possíveis para a TV Digital, estão a interatividade, a alta definição e a portabilidade em diversos dispositivos móveis.

Neste âmbito a interatividade aparece como principal fator potencializador de inovação de conteúdo agindo também como ponto chave na percepção do usuário sobre o conteúdo.

### 2.1.5 Serviços Interativos

Os serviços interativos permitem uma maior participação do usuário na escolha e formatação de conteúdo, o que, no limite dessa funcionalidade, pode trazer para o mundo da televisão um novo universo de aplicações e possibilidades similares às da Internet. Entre as novas aplicações providas com interatividade local, encontram-se multicâmeras, serviços extras vinculados ao programa, portal de informação, novos formatos de publicidade e Guia Eletrônico de Programação (GEP). Dependendo do cenário, a existência do canal de retorno permite, entre outros, serviços e aplicações como cursos e jogos on-line, envio de mensagens curtas, correio eletrônico, participação em programas com respostas individualizadas, TV-Gov (declarações, prontuários, agendamentos de serviços etc.), portal de informações, notícias personalizadas, comércio eletrônico e publicidade dirigida com resposta.

Este tipo de conteúdo é novo no mercado de televisão. Apenas algumas empresas de TV por assinatura fornecem serviços de interatividade, porém de maneira muito mais restrita: uma vez instalado o terminal de acesso, os serviços de interatividade já estão definidos e não mudam de acordo com a programação.

Quando vinculados aos programas de televisão e às publicidades, os serviços de interatividade passam a exigir uma demanda constante por produção. Desta maneira, a eficiência do processo de produção reduzirá os custos de produção impactando consequentemente na margem de lucro das produtoras. O projeto apresentado por este documento, possibilita a criação de ferramentas de autoria de conteúdo, portanto contribui de forma indireta na melhoria deste processo de produção.

Basicamente, aplicações interativas podem ser classificadas em três diferentes níveis de interatividade, sendo que o produtor poderá misturá-los para obter o apelo comercial ou aplicativo desejado. São os níveis:

- Nível reativo: as opções de conteúdo e feedback são fornecidas pelo próprio programa, e o usuário basicamente seleciona as informações e conteúdo ao qual deseja ter acesso. Temos aqui aplicações como seleção de legendas, canais, apresentação

de informações ao vivo, informações sobre preço e característica de produtos em cena, entre outras aplicações;

- nível coativo: o usuário pode escolher a seqüência de ações, telas, controlar o ritmo e interagir com as aplicações. Temos aqui aplicações com interatividade local, ou seja, podemos ter aplicações do tipo “Quiz”, jogos interativos, propagandas interativas com seleção de cenas e modificação da estrutura do vídeo e conteúdo multimídia;

- nível proativo: o usuário poderá controlar tanto a estrutura quanto o conteúdo. Temos o nível máximo de interatividade, no qual o usuário poderá demandar outros tipos de conteúdo, interagir e enviar dados de volta ao transmissor de conteúdo, acessar conteúdos multimídia em sites da Web, postar dados, acessar e-mail, aplicações de e-banking, entre outras.

Com estes três níveis de interatividade, o produtor de conteúdo poderá criar e produzir conteúdos muito mais ricos e que atinjam diretamente o seu telespectador, podendo interagir com ele e efetuar vendas e consultas de mercado durante a própria transmissão do conteúdo.

### 2.1.6 Plataforma brasileira para interatividade (Ginga)

Resultado de anos de pesquisas lideradas pela Pontifícia Universidade Católica do Rio de Janeiro (PUC - Rio) e pela Universidade Federal da Paraíba (UFPB), o Ginga é a camada de software intermediário (*middleware*) que permite o desenvolvimento de aplicações interativas para a TV Digital de forma independente da plataforma de hardware dos fabricantes de terminais de acesso (set-top boxes). Este padrão brasileiro reúne um conjunto de tecnologias e inovações brasileiras que o tornam a especificação de *middleware* mais avançada e, ao mesmo tempo, mais adequada à realidade do país.

Durante a elaboração deste documento, a especificação completa do GINGA esteve em processo de aprovação pública, sendo analisada por todas as entidades de pesquisas envolvidas com a produção de tecnologia para a TV Digital brasileira. A aprovação do padrão é praticamente certa.

## 2.2 Equipamento Utilizado

Nesta seção, são detalhados todos os equipamentos, ferramentas, software e componentes utilizados no desenvolvimento do projeto.

*Equipamentos:*

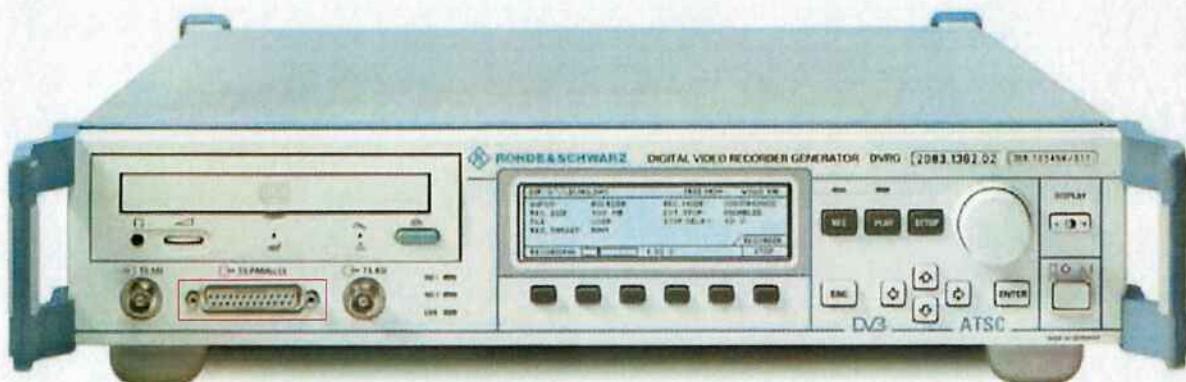

- Recorder Generator DVRC da Rohde & Schwarz : gerador de TS utilizado como fonte de transmissão para o dispositivo USB;

- SFU Broadcast Test System da Rohde & Schwarz: modulador para transmissão de DVB-T para recepção pelo set-top box;

- Set-top box DVB Philips: utilizado para visualização dos vídeos transmitidos em uma TV comum;

- Osciloscópio Tektronix TDS220 de 100MHz: utilizado para visualização dos sinais analógicos e digitais durante o desenvolvimento do projeto;

- MacBook, HP Pavilion, Notebook DELL: utilizados pelos integrantes do grupo para desenvolvimento do projeto;

*Software:*

- IntelliJ IDEA: IDE para desenvolvimento de aplicações em JAVA;

- Eclipse: IDE para desenvolvimento de aplicações em JAVA;

- Xilinx ISE 9.2i WebPack: IDE para desenvolvimento do modelo em VHDL do dispositivo e geração dos arquivos de configuração da FPGA;

- ModelSim XE III 6.2: simulador de circuitos lógicos integrado ao ambiente da Xilinx para simulação do dispositivo;

*Componentes e materiais:*

- Kit Opal Kelly XEM 3001v2: kit de desenvolvimento USB com FPGA Spartan-3 da Xilinx utilizado como base para o dispositivo USB;

- Conector D-subminiatura 25 pinos: utilizado para encaixe com a interface SPI do gerador de TS e interconexão com os pinos de entrada do kit de desenvolvimento;

- Cabo USB: utilizado para interconectar o kit de desenvolvimento ao computador *host*;

- Solda de estanho/chumbo: utilizada para a elaboração do conector e interconexão dos pinos no kit de desenvolvimento;

*Ferramentas:*

- Ferro de solda 25W: utilizado para realizar a solda de componentes;

- Alicate pela fio;

- Alicate cortador de fio;

## Capítulo 3

# ESPECIFICAÇÃO DO PROJETO

### 3.1 Funcionalidades principais

As funcionalidades principais do dispositivo são:

- Captura de vídeo digital a partir de stream MPEG2 de entrada.

- Visualização do vídeo capturado na tela do computador.

- Interface com outros programas para edição, compressão e armazenamento dos vídeos capturados em diferentes formatos (MPEG, DivX, XVID, entre outros).

- Suporte a novos módulos de aplicações para TV Digital (flexibilidade).

- Interatividade através de canal de retorno via conexão de Internet.

Figura 3.1: Diagrama de blocos da aplicação principal

### 3.2 Conexão USB

#### 3.2.1 Software

Para o funcionamento do dispositivo através da conexão USB do computador faz-se necessário a criação de um driver para transferência dos dados. O desenvolvimento de drivers para plataforma Windows foi simplificado no final do ano de 2005 com a adição do

framework Windows Driver Foundation (WDF), uma camada acima e em nível mais alto que o Windows Driver Model (WDM). Tal tecnologia tem possibilitado agilidade na criação dos drivers e maior segurança através do encapsulamento de itens como a estrutura de dispositivos Plug and Play (PnP), gerenciamento de energia, requisições de I/O, eventos e interrupções.

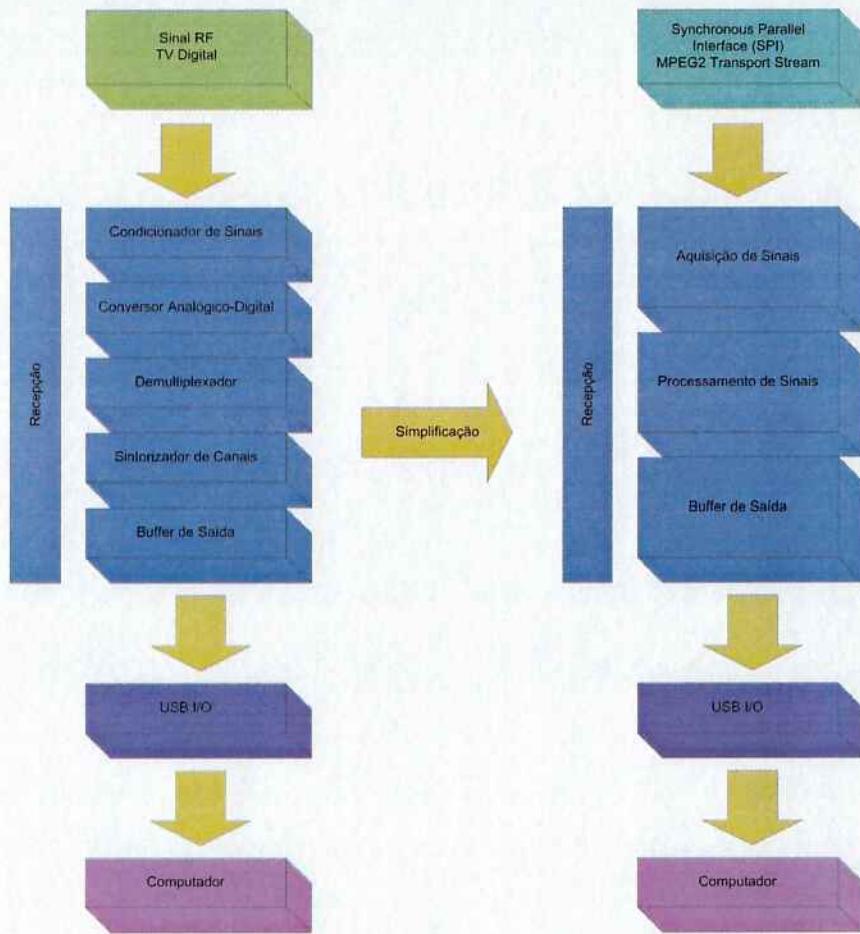

### 3.2.2 Hardware

Inicialmente o hardware a ser utilizado no projeto consistia em um receptor de TV Digital por Radio Freqüência (RF), abrangendo assim todas as etapas de tratamento do sinal. Visando a simplificação, uma vez que a recepção do sinal não é o objetivo principal, o projeto foi reduzido para capturar uma saída MPEG2 Transport Stream (já digital) de um aparelho de geração de sinais, ao invés de obtê-lo a partir da demodulação e decodificação de um sinal RF. A Figura 3.2 mostra o diagrama em blocos que representa o esquema do hardware necessário.

Figura 3.2: Diagrama de blocos do hardware completo para a aquisição do sinal

O gerador de sinais DVRG, da *Rohde & Schwarz*, dispõe de uma saída serial assíncrona com conector BNC a 270 Mbits/s e uma saída paralela síncrona de 25 pinos que transmitem dados em MPEG2-TS, facilitando o projeto e o desenvolvimento do sistema de

Figura 3.3: *Processo de simplificação para este projeto*

aquisição de sinais. Como o padrão USB 2.0 estabelece uma taxa de transferência de 480 Mbits/s, a viabilidade da transmissão do sinal para o computador não é comprometida.

A Figura 3.3 apresenta o diagrama de blocos do projeto original e a sua simplificação para o projeto no estágio atual.

### 3.3 Formato dos dados

Tecnologias de transmissão e modulação dos dados estão fora do escopo deste projeto. Não há nenhuma suposição sobre como são feitas a transmissão e a modulação dos dados. Apesar de o foco estar no modelo brasileiro de TV Digital, SBTVD, o projeto se encaixa com qualquer um dos padrões existentes para modulação e transmissão de conteúdo: o europeu DVB [13], o norte americano ATSC [10] e o japonês ISDB [14].

Para alcançar tal independência, o conteúdo será capturado no formato definido pelo padrão MPEG-2 [9], suportado por todos os padrões e tecnologias de transmissão do sinal de TV Digital.

### 3.3.1 O padrão MPEG-2

De uma forma geral, o padrão MPEG-2 define como informações de som, imagem e dados são codificadas, decodificadas, comprimidas, armazenadas e transmitidas. Ele também é um padrão internacional, o ISO/IEC 13818 e é dividido em dez partes. São listadas abaixo as sete mais importantes:

- **Parte 1 - Sistemas:** sincronização e multiplexação de som, vídeo e dados. Também conhecida como ITU-T Rec. H.222.0.

- **Parte 2 - Vídeo:** codificação e compressão de vídeo. Também conhecida como ITU-T Rec. H.262.

- **Parte 3 - Áudio:** codificação e compressão de áudio.

- **Parte 4 - testes de compatibilidade com a especificação.**

- **Parte 5 - descreve sistemas de simulação por software.**

- **Parte 6 - mecanismos de proteção contra fraude (cópias e armazenamento) - DSM-CC (Digital Storage Media Command and Control).**

- **Parte 7 - formato avançado para codificação e compressão de áudio, AAC (Advanced Audio Coding).**

Para o projeto, a primeira parte (**Sistemas**) é a mais importante, pois define como são misturadas (ou multiplexadas) as informações de som, vídeo e dados a serem transmitidas. Esta parte ainda se divide em duas, sendo uma divisão adequada a aplicações de transmissão (*broadcast*), conhecida como *MPEG-2 Transport Stream* e uma divisão adequada a sistemas de armazenamento, conhecida como *MPEG-2 Program Stream*.

O projeto assume que os dados entram no formato MPEG-2 Transport Stream. A recepção e demodulação deste sinal estão fora do escopo.

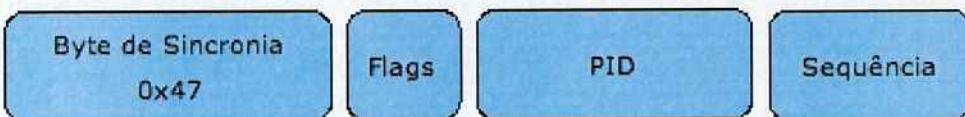

Figura 3.4: Parte do cabeçalho dos pacotes

### 3.3.2 Conteúdo como fluxo de dados: MPEG-2 Transport Stream

O padrão MPEG-2 Transport Stream é formalmente um protocolo de comunicação de áudio, vídeo e dados que tem como objetivo principal permitir a transmissão dos três componentes em um mesmo fluxo de dados, através da multiplexação no tempo. O protocolo ainda prevê recursos para sincronização entre os componentes e correção de erros no transporte sobre meios não confiáveis.

Os pacotes são a unidade básica do protocolo e geralmente têm tamanho de **188 bytes**. Um fluxo MPEG-2 é composto de pacotes pertencentes a diversos fluxos elementares, misturados pela multiplexação no tempo. A Figura 3.4 mostra a composição de uma parte do cabeçalho dos pacotes, que iniciam por um byte de sincronização de valor *0x47*.

Um dos componentes mais importantes dos cabeçalhos dos pacotes é o *Program ID - PID*, de 13 bits. Pacotes de mesmo PID formam um fluxo elementar, que pode transportar vídeo, áudio ou dados.

Um Programa é formado por um conjunto de fluxos elementares. Geralmente há um fluxo elementar para vídeo, dois para áudio (som estéreo) e um para dados, mas um programa pode ter quais fluxos elementares forem necessários. Os Programas são popularmente conhecidos como **canais de televisão** e comumente cada fluxo MPEG-2 pode carregar três deles.

Para a definição dos programas existentes em um fluxo MPEG-2, existem alguns pacotes especiais de PID *0x00*. São pacotes pertencentes à PAT (*Program Association Table*), que listam os PIDs de quais pacotes contém informações sobre os programas.

Os pacotes que contêm informações sobre os programas são conhecidos como PMTs (*Program Map Tables*) e definem quais são os conjuntos de PIDs que formam os Programas. Em outras palavras, os PMTs agrupam conjuntos de fluxos elementares em Programas e ainda contém metadados sobre cada um dos fluxos elementares; mostrando, por exemplo, se um fluxo elementar carrega vídeo, áudio ou dados.

### 3.4 Middleware

O nome vem de sua principal função: prover a interação entre as aplicações da TV Digital e o hardware do *set-top box*. Dito de outra maneira, o *middleware* é o software responsável pelo tratamento, decodificação e reprodução do áudio e do vídeo e pela execução das aplicações de TV Digital. O *middleware* é uma plataforma para a execução de aplicações de TV Digital.

Existem diversas especificações para *middlewares*. O mais famoso de todos é o *Multimedia Home Platform* (MHP) [16], definido no padrão europeu DVB [13] e baseado na tecnologia JavaTV. O MHP foi tão bem visto que acabou baseando diversas outras especificações de *middlewares* e fez com que fosse criado o *Globally Executable MHP* (GEM [17]), pedaço do MHP sem os detalhes específicos do DVB, para ser usado como base em outras tecnologias de transmissão e decodificação.

O GEM é a base que impulsiona uma das duas abordagens para *middlewares* de TV Digital; a abordagem procedural. Nesta abordagem, as aplicações de TV Digital são escritas como programas convencionais em alguma linguagem de alto nível (quase sempre em Java). Exemplos de *middlewares* que seguem esta abordagem são o europeu DVB-J (o próprio MHP, o "J" vem de Java), o norte americano OCAP (*OpenCable Application Platform* [12]), o outro norte americano ACAP (*Advanced Application Platform* [11]), o japonês ARIB B.23 [7] e o brasileiro Ginga-J (o "J" vem de Java [18]), coordenado pelo Laboratório de Aplicações de Vídeo Digital (LAViD) do Departamento de Informática (DI) da Universidade Federal da Paraíba (UFPB).

A outra abordagem para *middlewares* de TV Digital é a declarativa, onde as aplicações de TV Digital são programas declarados em linguagens derivadas do XML, como o XHTML. É um modelo de desenvolvimento parecido com o atualmente empregado na Internet, onde as páginas são geralmente declaradas em linguagem XHTML.

A abordagem declarativa ainda permite o uso de algum tipo de linguagem ou script para conseguir oferecer as mesmas funcionalidades que a abordagem procedural. Geralmente é possível descrever algumas funcionalidades específicas da aplicação de TV Digital de forma procedural através destas linguagens embutidas. Um exemplo de linguagem largamente utilizada para este fim é o ECMAScript, popularmente conhecida como JavaScript.

O pioneiro da abordagem declarativa é o padrão de *middleware* japonês definido pela organização ARIB que usa a linguagem BML (*Broadcast Markup Language*) baseada no XHTML. Outros exemplos de *middlewares* existentes que seguem a abordagem declarativa são o europeu DVB-HTML, o norte americano ACAP-X e o brasileiro Ginga-NCL, que usa

a Nested Context Language (NCL) e é desenvolvido pelo Departamento de Informática da Pontifícia Universidade Católica do Rio de Janeiro (PUC - Rio).

A especificação que define o middleware incluído no padrão brasileiro de TV Digital – SBTVD – é o Ginga, incluindo tanto o Ginga-J quanto o Ginga-NCL.

Para o projeto, foram consideradas duas alternativas para adoção: o europeu DVB-J/MHP como abordagem procedural, ou o brasileiro Ginga-NCL como abordagem declarativa. A escolha teve de ser feita com base nas ferramentas e implementações existentes para ambas as alternativas, tendo em vista que o projeto visa estender uma alternativa de middleware livre existente para prover as funcionalidades desejadas.

A primeira escolha foi trabalhar com o padrão europeu MHP, já que o padrão brasileiro Ginga ainda vinha sendo desenvolvido e não estava facilmente disponível para consulta. Porém durante o desenvolvimento do projeto, foi anunciado o lançamento público das especificações do Ginga e a implementação de referência do Ginga-NCL foi disponibilizada ao público através do portal Software Público, do governo federal (<http://www.softwarepublico.gov.br>).

Tais fatos fizeram com que o direcionamento da tecnologia de middleware para a interatividade fosse firmada na utilização do Ginga [18] (em oposição ao MHP), por ser parte integrante da especificação do padrão do Sistema Brasileiro de TV Digital e pela possibilidade de participar e contribuir com a implementação da especificação, por tratar-se de software livre.

Esta foi uma decisão importante, que afetou de maneira crítica o direcionamento do projeto, que originalmente estava dimensionado e baseado no padrão europeu MHP. Felizmente, todos os padrões mundiais de middleware para TV Digital têm pontos em comum, padronizados pelo GEM. Oportunamente, o padrão de middleware brasileiro adotado, também é baseado neste padrão internacional, o que permitiu o aproveitamento da maior parte do trabalho já realizado no projeto.

Dadas as desvantagens de se mudar a direção do projeto já em estágio avançado, a importante decisão foi tomada principalmente levando em consideração a potencial contribuição social e tecnológica deste Projeto de Formatura ao país. O Brasil está criando o seu próprio padrão de middleware para TV Digital, o que incentiva diretamente o desenvolvimento de tecnologia nacional. Além disso, cria-se uma reserva de mercado, já que as empresas multinacionais do setor ainda não têm a tecnologia para produção em escala, baseada no middleware brasileiro. Esta reserva abre oportunidade para novos empreendedores dentro do país.

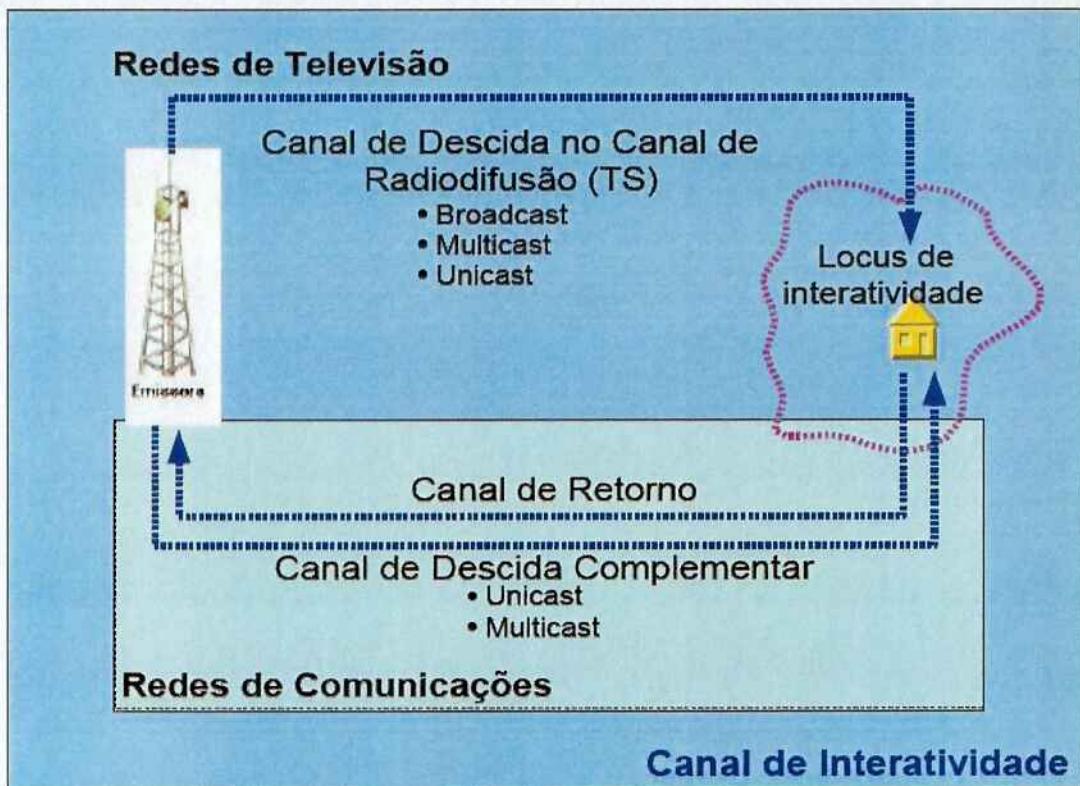

Figura 3.5: *Diagrama do Canal de Interatividade*

### 3.5 Canal de retorno

#### 3.5.1 Conceito

O Canal de Retorno, ou Canal de Interatividade, é a camada responsável por viabilizar a comunicação das aplicações interativas, no terminal de acesso, com os servidores de aplicação do provedor de conteúdo. Desta forma, pode-se conceituar o Canal de Interatividade como o subsistema que permite que cada usuário, individualmente, possa interagir de forma própria com o conteúdo multimídia disponibilizado pelas emissoras, enviando e/ou recebendo informações e complementando atividades e aplicações disponíveis.

A arquitetura prevista para o Canal de Retorno tende a utilizar múltiplas tecnologias de comunicação, o que permite um aumento na capacidade de acesso, cobertura e número de usuários com acesso a conteúdos adicionais ao conteúdo normal disponibilizado.

No caso do SBTVD, o uso de diferentes meios de comunicação para a implementação do Canal de Retorno é essencial, já que a maior meta do SBTVD é a inclusão digital de regiões longínquas, onde o acesso à informação e cultura é escasso e limitado. Portanto, o canal de retorno deve possibilitar interatividade a partir dos meios disponíveis em tais

regiões, havendo assim a necessidade de se adaptar a diferentes subsistemas de comunicação, desde as redes GSM, como as redes de telefonia discada, comunicação via RF e outras.

### 3.5.2 Aplicações

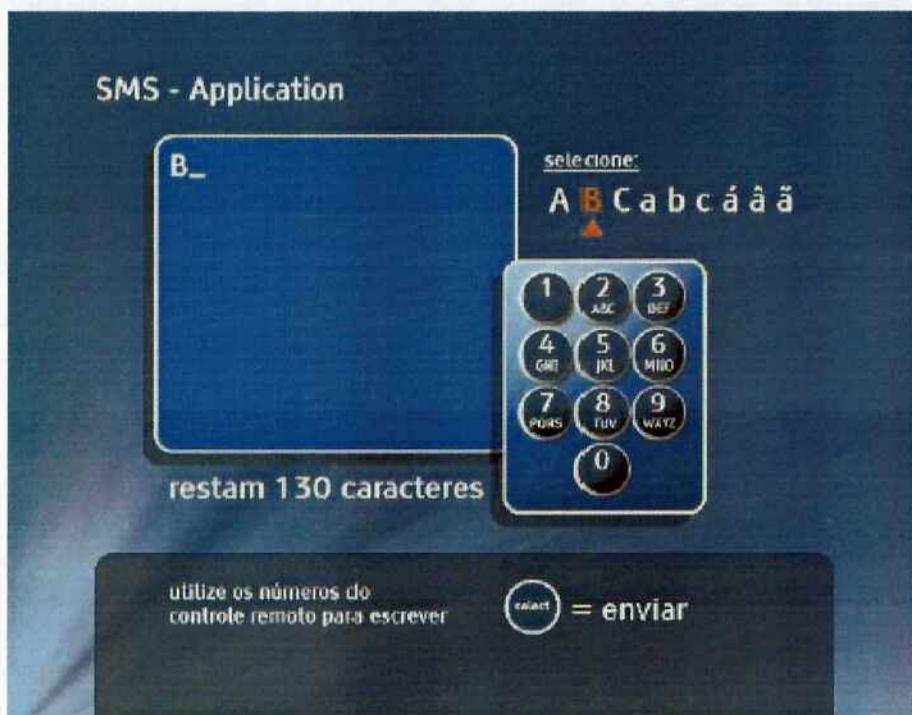

A interatividade pode ser dividida em três níveis, como já descrito na Seção 2.1.5. Além disso, sob o ponto de vista das aplicações interativas que se utilizam do Canal de Retorno, podemos dividi-las em dois tipos de interatividade, sendo estas as aplicações de Interatividade Intermittente e Interatividade Permanente.

#### Aplicações de Interatividade Intermittente

Para este tipo de aplicações, a comunicação entre o telespectador e o emissor de conteúdo se dá de forma unidirecional, ou seja, o telespectador apenas envia informações para o emissor, sem esperar nenhuma resposta a cerca das informações enviadas.

Neste tipo de aplicação se enquadram o envio de votos de enquetes, pesquisas de opinião, jogos do tipo quiz, envio de mensagens SMS, entre outras aplicações. Neste caso, o usuário apenas utiliza o canal de retorno como forma de enviar informações, utilizando alguma aplicação do emissor de conteúdo para tratar os dados enviados. Assim, não é necessária a comunicação do emissor de conteúdo para o telespectador através do canal de retorno, pois todos os dados necessários já foram enviados através das aplicações de dados recebidas no terminal de acesso.

Apesar de possuírem um grau de interatividade limitado, tais aplicações já permitem que o emissor de conteúdo interaja com seus telespectadores, porém não há emissão de conteúdo individual e exclusivo para cada telespectador, há apenas a coleta de informações e tratamento das mesmas pelo emissor.

#### Aplicações de Interatividade Permanente

Para este tipo de aplicações, a comunicação entre o telespectador e o emissor de conteúdo passa a ser bidirecional, ampliando o nível de interatividade e permitindo a emissão de conteúdo exclusivo do emissor para o telespectador.

Tais aplicações passam a incorporar funções que poderiam existir em um computador conectado à Internet, tais como envio e recebimento de e-mails, jogos multiusuários, home banking, chat, educação à distância, compras on-line, pesquisa, etc. Este nível de inter-

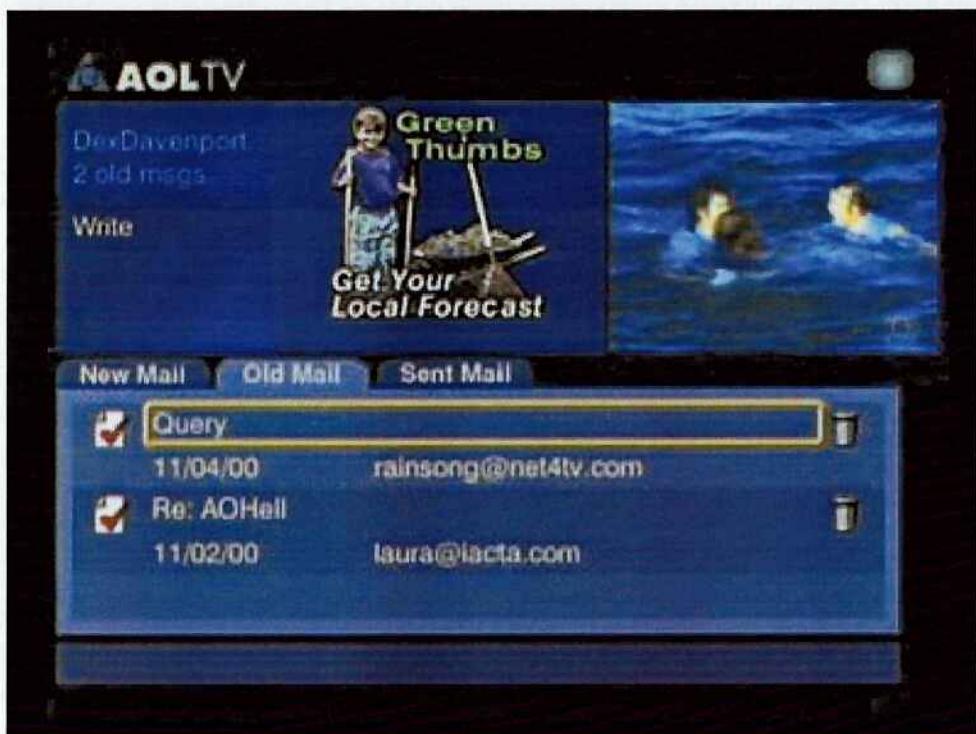

Figura 3.6: Aplicação SMS utilizando interatividade intermitente.

atividade permite inclusive que conteúdo multimídia extra seja enviado ao telespectador, conforme suas necessidades e serviços disponíveis.

Outra aplicação acrescentada é a possibilidade de comunicação entre os telespectadores, permitindo a discussão de conteúdos e uma interação completa entre todos os receptores de conteúdo do mesmo emissor.

Como um exemplo do uso extensivo deste grau de comunicação, podemos ilustrar a seguinte situação. Um telespectador está assistindo a um evento esportivo de seu gosto, como por exemplo, uma partida de futebol. Ele se interessa em comprar a mesma chuteira que o seu jogador predileto usa. Utilizando os dados já enviados pelo emissor de conteúdo, ele sabe a marca e modelo da chuteira que o jogador está usando (interatividade local). Ele pode utilizar uma aplicação que compare o preço do produto em diferentes lojas online. Após isto, ele pode entrar em um fórum de discussão onde outros telespectadores comentam sobre o produto e sobre o atendimento das lojas nas quais eles compraram o produto. Utilizando uma aplicação de home banking, ele consulta o seu saldo no banco. Baseado em todas as informações, o telespectador decide comprar o produto e acessa via alguma aplicação a loja na qual o produto está mais barato. Efetua a compra e continua assistindo ao jogo, feliz em saber que em alguns dias terá a mesma chuteira que a de seu jogador favorito.

Figura 3.7: Aplicação de e-mail com interatividade permanente.

### 3.5.3 Implementação

Como foco principal do projeto, é realizada a implementação do Canal de Retorno do dispositivo USBTv através de uma conexão qualquer com a Internet, seja através de conexão discada, ADSL, cabo, sem fio, ou qualquer outra forma disponível para o usuário.

Como já previsto no SBTVD, o canal de retorno deve ser de fácil implementação e permitir o uso de diferentes tecnologias. Supondo que, para a maior parte dos usuários de computador, já existe uma conexão com a Internet, nada melhor do que utilizá-la como o canal de retorno, permitindo assim uma integração total das aplicações de TV Digital com as aplicações disponíveis para um computador comum através da Internet.

Assim sendo, o projeto deve analisar e implementar a camada de interface entre as aplicações de TV Digital e os serviços disponíveis na Internet, inicialmente para o *middleware* escolhido, porém expansível para os demais tipos de *middleware* existentes.

O uso da Internet como canal de retorno viabiliza tanto a interatividade intermitente como a permanente, ampliando-as ainda mais, pois permite a interação com os sistemas já existentes de conteúdo multimídia na Internet. Poderíamos citar, por exemplo, uma aplicação de TV digital que permitisse a busca por vídeos no YouTube similares ao conteúdo que está sendo atualmente transmitido pelo emissor de conteúdo e, através do canal de retorno, carregar e apresentar o vídeo simultaneamente à transmissão de TV. Ou ainda,

poderíamos prever uma integração com os serviços já disponibilizados via Web Services de lojas como Amazon, permitindo o reuso das tecnologias já existentes na Internet para o uso com aplicações de TV Digital.

Assim, o projeto deve viabilizar e formalizar o canal de retorno através da Internet, analisando quais os protocolos de comunicação mais adequados a serem utilizados e realizando sua implementação como modelo de referência e prova de conceito.

### 3.6 Planejamento e Métodos

Todas as tarefas desenvolvidas pelos integrantes do grupo podem ser divididas em três grandes conjuntos de tarefas, as quais são desenvolvidas por cada um dos integrantes do grupo de acordo com seu grau de interesse pelo assunto.

Foram previstas etapas de integração das tarefas desenvolvidas individualmente, para que o grupo como um todo possa entender e acompanhar o funcionamento de cada uma das partes do projeto.

Cada grupo de tarefas representa problemas distintos, necessitando para tanto o uso de diferentes abordagens para sua resolução. A seguir estão detalhados cada um dos conjuntos de tarefas, assim como os métodos e técnicas que serão utilizados para o seu desenvolvimento.

#### 3.6.1 TV Digital e Middleware

Este conjunto de tarefas engloba todas as etapas de pesquisa e desenvolvimento necessários para o entendimento e uso das atuais tecnologias e plataformas de desenvolvimento para a TV Digital.

São necessários o entendimento dos formatos de dados, fluxos, codificação, modulação, empacotamento e transmissão do sinal multimídia em fluxo de dados, bem como o entendimento profundo do middleware a ser utilizado como plataforma para as aplicações de TV Digital.

Fica de responsabilidade deste conjunto de tarefas o entendimento e uso adequado das ferramentas de desenvolvimento, simulação e execução de aplicações, além da geração e/ou simulação da transmissão de TV Digital a ser captada e apresentada pelo dispositivo USBTv.

### Sinal de TV Digital

Esta tarefa consiste em obter e utilizar dispositivos de geração, transmissão e recepção de sinal de TV Digital para o uso como entrada para o dispositivo de captura. Isto tem como função principal simular o sinal recebido por um telespectador transmitido por um provedor de TV Digital, baseado nos padrões disponíveis atualmente no mercado. É dada prioridade ao formato escolhido pelas especificações do padrão brasileiro de TV Digital (SBTVD), porém outros padrões poderão ser utilizados, desde que se obtenha como produto final o MPEG-2 Transport Stream para o uso com o dispositivo de captura USBTv.

### Complementação do Middleware

Esta tarefa consiste em testar e analisar os diferentes padrões de *middleware* previstos para o SBTVD (Ginga-J e Ginga-NCL) e verificar qual padrão oferece melhor suporte e viabilidade técnica para o desenvolvimento das aplicações de TV Digital com suporte ao canal de retorno pela Internet.

Inicialmente foram abordados os padrões GINGA-NCL e o MHP, sendo analisadas as suas especificações e ferramentas disponíveis no mercado para o desenvolvimento e simulação de aplicações em cada um dos *middlewares*.

#### 3.6.2 Captura do Sinal via USB

Este conjunto de tarefas engloba todas as etapas de pesquisa e desenvolvimento necessárias para a implementação das camadas de hardware e software, que permitam o envio do sinal de TV Digital no formato MPEG-2 Transport Stream como fluxo serial de dados para o uso nas plataformas de aplicações de TV Digital no computador, através de uma porta USB.

Este conjunto é a parte do projeto que permite que o mundo da TV Digital possa ser aproveitado, assistido e utilizado em qualquer computador que possua interface USB. Para tanto, deverá implementar não só o hardware mas também os *drivers* e componentes de software necessários para o uso do sinal de TV Digital no computador.

Este conjunto de funcionalidades pode ser simulado ao longo do projeto para o desenvolvimento das outras etapas, permitindo o paralelismo do trabalho. Existem no mercado softwares que geram arquivos no formato MPEG-2 Transport Stream, que podem ser utilizados como sinal de entrada para as plataformas de *middleware* e para o desenvolvimento e testes do canal de retorno. Porém, o projeto deve implementar tal interface de hardware

para que os objetivos de portabilidade e usabilidade especificados no projeto sejam completamente alcançados.

### **Hardware USB**

Esta tarefa consiste em especificar, detalhar e implementar o hardware necessário para a captura do MPEG-2 Transport Stream e seu envio em formato serial para o computador através do padrão USB.

Como método, pode ser citado o uso de diagramas de blocos funcionais, que a cada nível detalham os requisitos específicos de cada módulo, detalhando suas entradas e saídas. A arquitetura é detalhada até a obtenção de módulos compatíveis com componentes existentes no mercado, de forma a facilitar a implementação do hardware necessário.

Está aberta a possibilidade do uso de kits de desenvolvimento, que forneçam suporte ao tratamento dos dados e comunicação USB, além de ser necessária a completa especificação e elaboração do circuito lógico e físico dedicados para a aplicação USBTv, permitindo assim uma possível implementação comercial do projeto.

### **Software USB**

Esta tarefa consiste em especificar, detalhar e implementar os drivers e aplicativos necessários para o tratamento da entrada de dados USB e sua correta formatação para o uso do sinal como entrada para aplicações de TV Digital.

Inicialmente está previsto o desenvolvimento de drivers para o Sistema Operacional Windows, uma vez que já existem bibliotecas padrão que facilitam a implementação da comunicação USB. Para o desenvolvimento é utilizado o WDK (*Windows Driver Kit*), que já possui extensões para a implementação de drivers USB.

São utilizadas as ferramentas e padrões de desenvolvimento estabelecidos por órgãos internacionais, como os padrões definidos [19].

Caso possível, podem ser desenvolvidos também drivers e aplicações para outros sistemas operacionais, como o Linux e o Mac OS X.

#### **3.6.3 Canal de Retorno pela Internet**

Este conjunto de tarefas engloba todas as etapas de pesquisa e desenvolvimento necessárias para a implementação da interface e protocolos de comunicação que possibilitem o canal de interatividade via conexão com a Internet.

Tais tarefas devem apresentar como resultado final um arcabouço que permita que qualquer aplicação de TV Digital consiga acessar serviços disponibilizados na Internet por emissores de conteúdo, de preferência independentemente do padrão de *middleware* utilizado.

Dentro destas tarefas, está também a migração de algum serviço disponível na Internet como serviço para aplicações de TV Digital, utilizando os protocolos e bibliotecas desenvolvidas para fazer a comunicação e interfaces necessárias como canal de retorno. Ou seja, deve ser criada uma aplicação de exemplo que utilize o canal de retorno implementado para executar alguma tarefa atualmente só disponível para aplicações de computadores.

Como métodos de desenvolvimento, podem ser citados o uso das camadas do modelo OSI, sendo definidas as interfaces, entradas e saídas (protocolos) para cada uma das camadas necessárias para a implementação do canal de retorno via Internet.

São utilizados os padrões da UML para documentação do software a ser desenvolvido, sendo utilizadas ferramentas abertas de modelagem de software (como, por exemplo, a ferramenta ArgoUML para modelagem UML) e dadas as características da equipe e do projeto, optou-se por uma metodologia ágil e iterativa de desenvolvimento, baseada em resultados e metas parciais.

## Capítulo 4

# METODOLOGIA

### 4.1 Metodologia Ágil

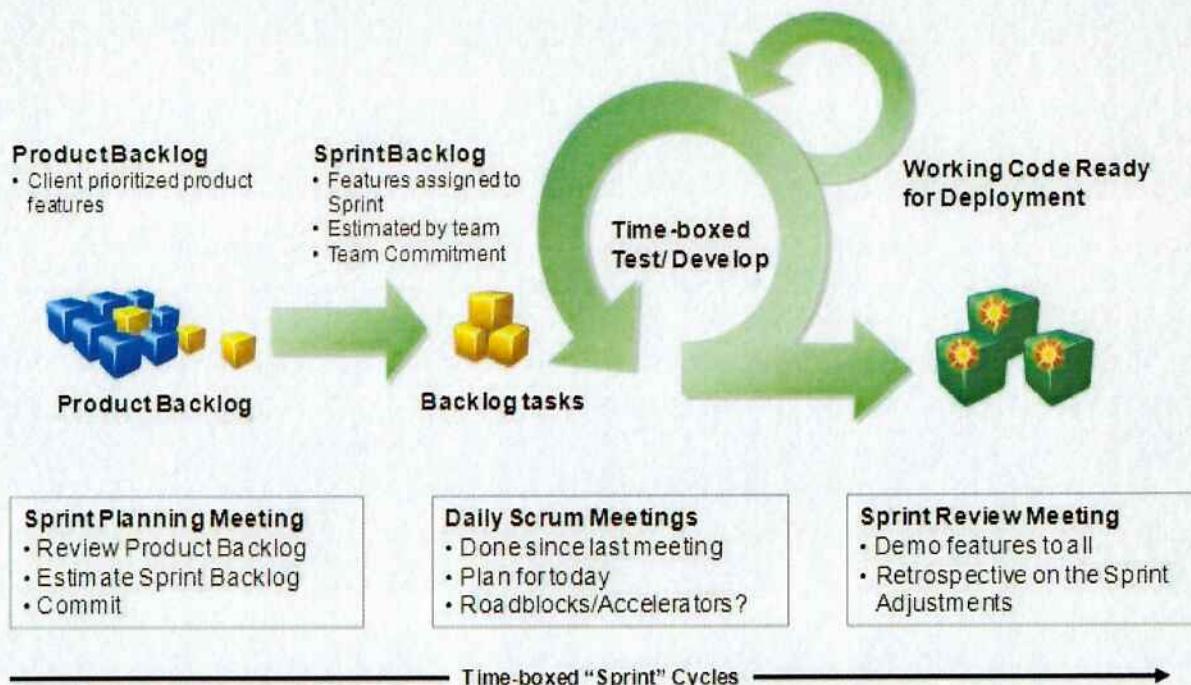

Como metodologia de processo de desenvolvimento de software o grupo adotou métodos ágeis, utilizando como base para gerenciamento de projetos a metodologia *SCRUM*.

Esta metodologia consiste em um processo incremental e iterativo, no qual desenvolvedores e interessados têm uma relação muito próxima e versões intermediárias são entregues assim que determinadas funcionalidades são completadas.

São realizadas pequenas reuniões diárias para avaliação do andamento das equipes no desenvolvimento de cada funcionalidade, havendo assim uma troca de experiências, problemas e soluções entre os integrantes da equipe. Ao final de prazos pré-estabelecidos (para este projeto o prazo foi de uma semana), são entregues versões das funcionalidades para que os interessados possam testá-las, sugerir modificações e propor melhorias. Desta forma, é garantida a qualidade e prazos para funcionalidade e, ao final de todo o processo iterativo, o produto é finalizado com todas as suas funcionalidades testadas e aprovadas pelos interessados.

A Figura 4.1 exibe o fluxo do processo de desenvolvimento iterativo adotado.

Figura 4.1: Descrição da metodologia de desenvolvimento ágil Scrum

## 4.2 Desenvolvimento do Hardware

Como metodologia para o desenvolvimento do hardware, também foi adotado o modelo incremental e iterativo, no qual a cada iteração novas funcionalidades foram sendo agregadas ao dispositivo em desenvolvimento. Assim, foi possível gerar versões intermediárias do dispositivo, a medida das quais ele se tornava mais complexo e apto a realizar completamente determinadas funcionalidades.

Como modelo de arquitetura de desenvolvimento de sistemas digitais, foi utilizado o modelo de máquina de estados com “datapath”, no qual existe uma máquina de estados que controla as entradas, saídas e transições da unidade de controle, porém com interligação direta entre os diferentes componentes da arquitetura para a realização do fluxo de dados.

Assim, foi possível utilizar todas as técnicas comumente utilizadas no desenvolvimento de sistemas digitais [31] baseados em máquinas de estados, no qual é possível acompanhar o estado atual do dispositivo e o andamento do fluxo de dados ao longo das transições entre estados. Desta forma, foi possível validar o sistema com simulações de sua lógica interna, antes mesmo de tê-lo implementado no hardware físico.

Desta forma, foi possível garantir em ambiente de desenvolvimento e simulação o funcionamento lógico do dispositivo, validando-se inclusive o fluxo de dados entre os diferentes componentes desenvolvidos.

Para o design e avaliação individual de cada componente, foram utilizadas as metodologias de projeto lógico digital descritas em [32], no qual são definidas técnicas para desenvolvimento de memórias e componentes lógicos digitais.

## Capítulo 5

# PROJETO E IMPLEMENTAÇÃO

### 5.1 Dispositivo USB

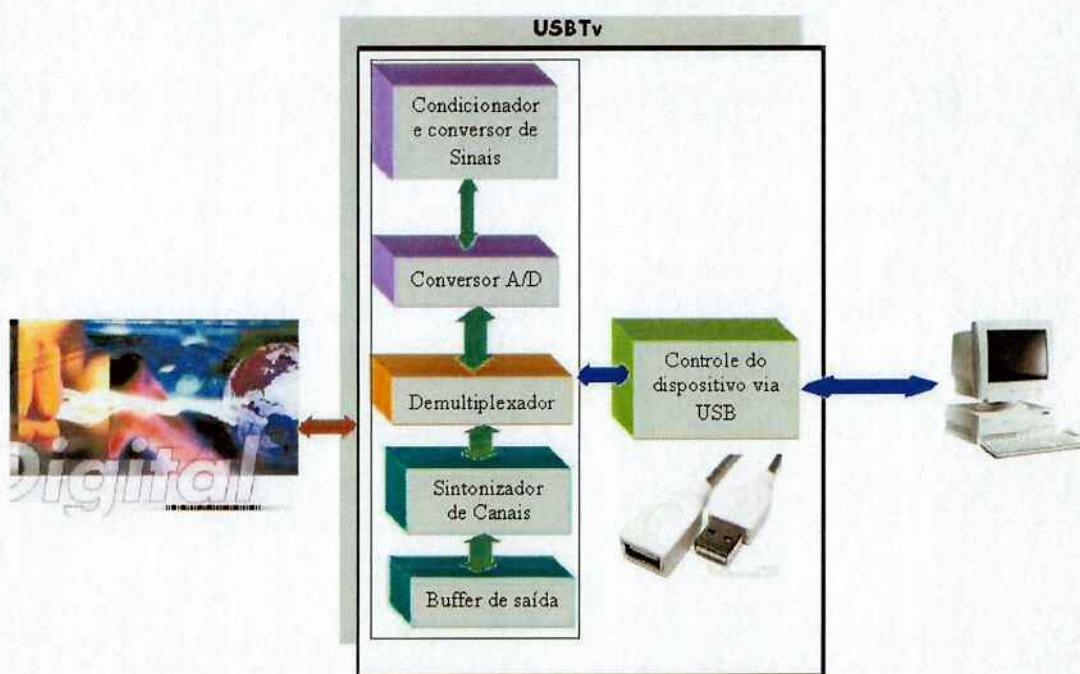

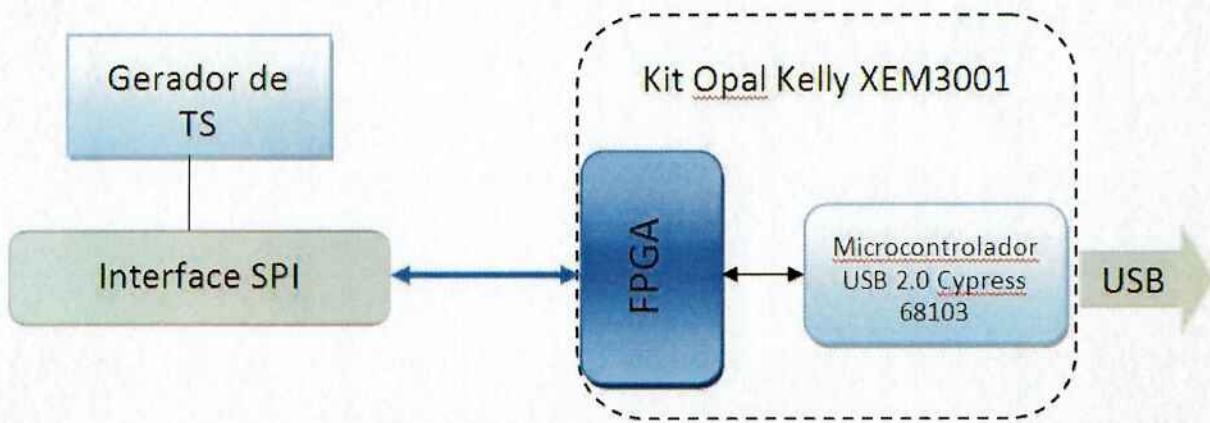

Baseando-se nas especificações dos requisitos funcionais e não funcionais para o dispositivo de captura de vídeo digital através da porta de comunicação USB, foi possível elaborar uma arquitetura que implementasse todo o tratamento do sinal de TV Digital até a comunicação serial com o computador de destino dos dados.

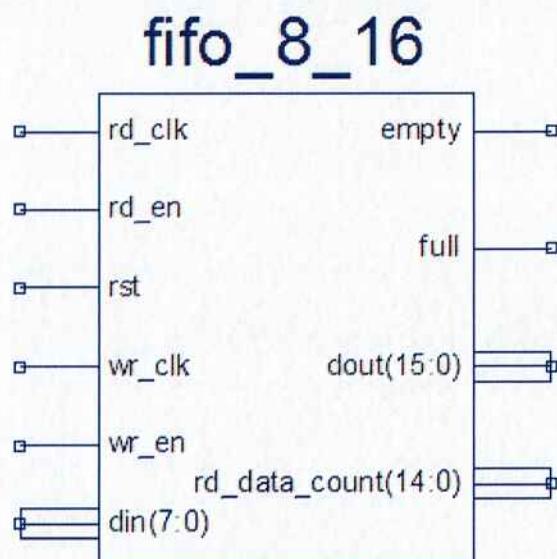

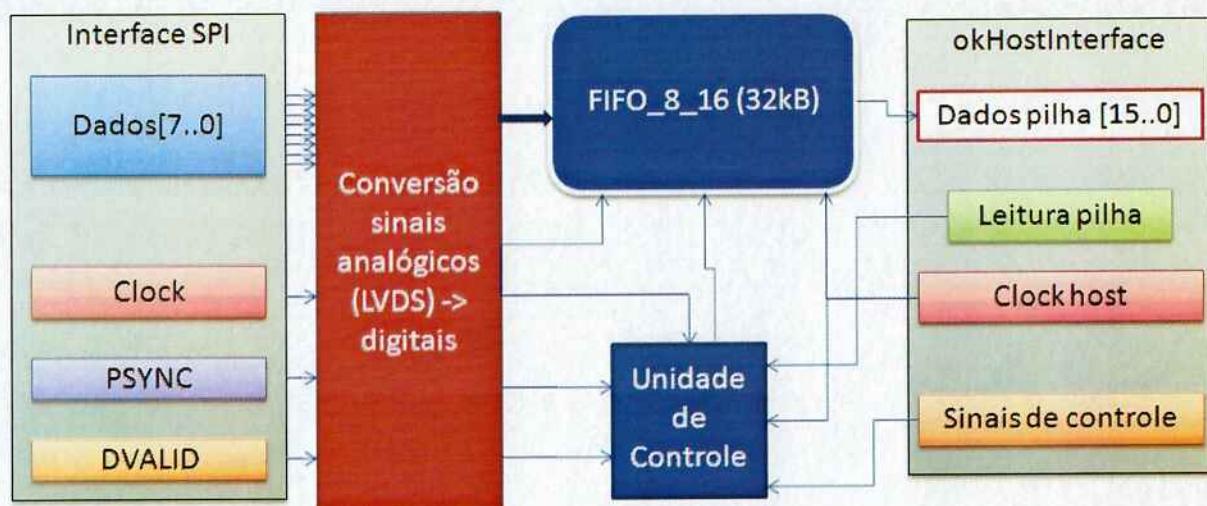

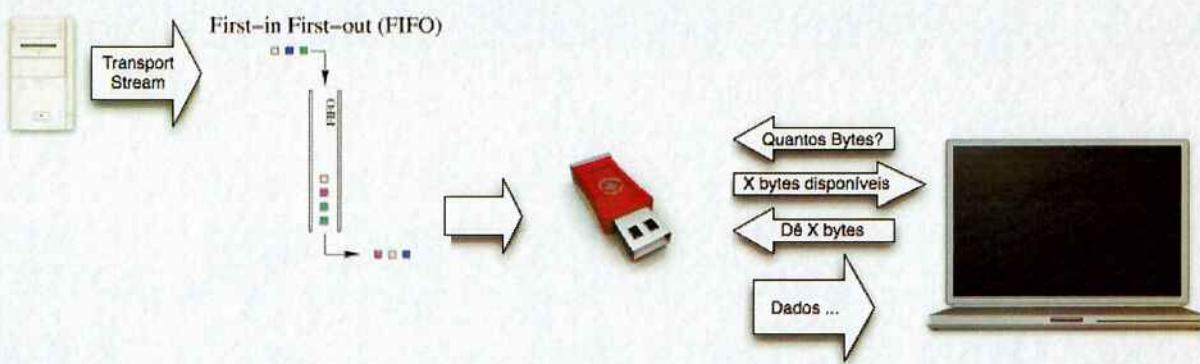

A arquitetura resume-se a componentes de hardware que efetuam o tratamento dos sinais transmitidos pela interface SPI do Gerador de Transport Stream, tornando-os compatíveis para o tratamento lógico digital. Em seguida, os dados são amostrados e armazenados em unidades de memória organizadas como um FIFO, e por fim lidas pela interface USB pelo computador host.

A Figura 5.1 ilustra a arquitetura adotada, representando os principais blocos utilizados para a implementação do dispositivo de captura USB. As demais seções irão detalhar o funcionamento de cada bloco individualmente, bem como os componentes lógicos e de hardware, além padrões de interfaces utilizados na implementação de tal arquitetura.

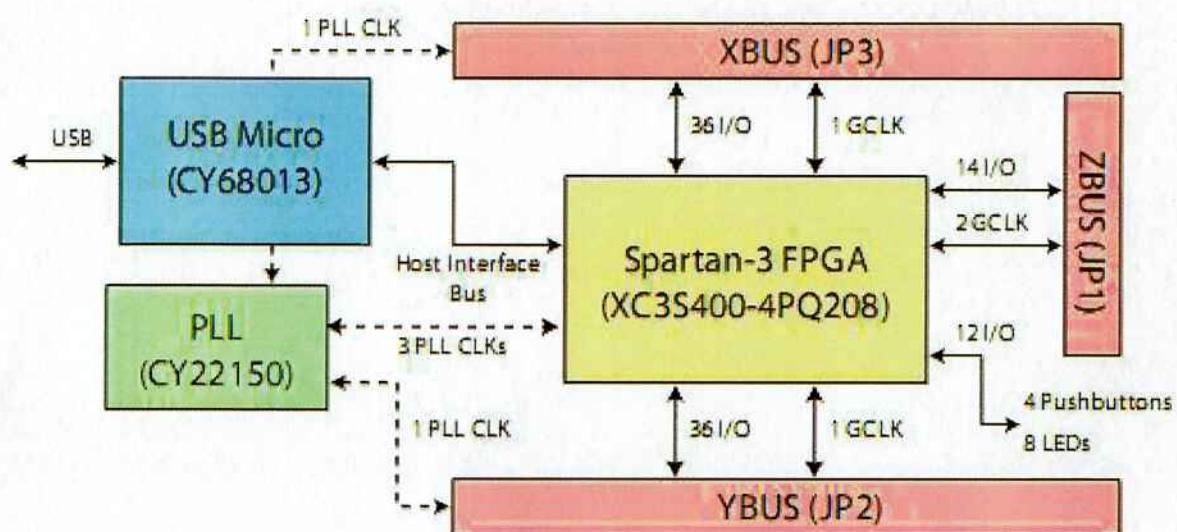

Figura 5.1: Visão geral da arquitetura do dispositivo USB

Figura 5.2: *Topologia da arquitetura USB*

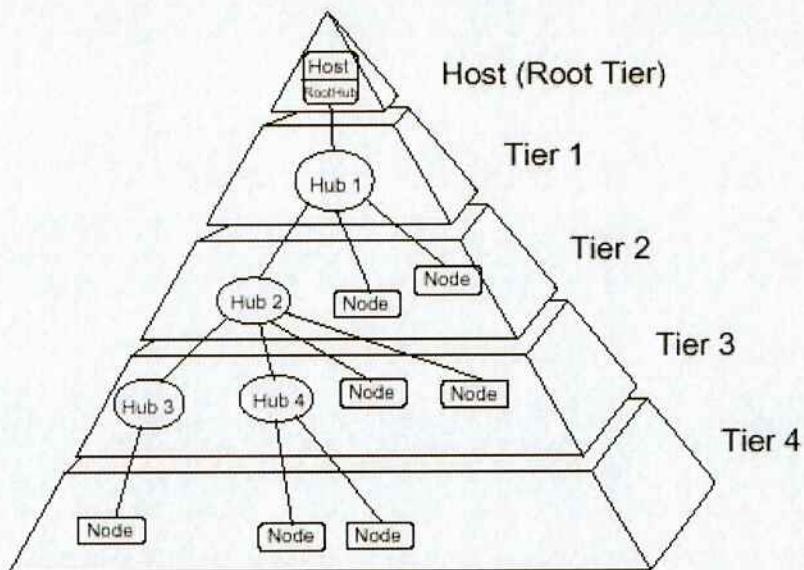

### 5.1.1 Arquitetura USB

Para desenvolver um dispositivo de captura USB, é necessário entender a arquitetura e o funcionamento do padrão USB, para que o dispositivo a ser interconectado possa implementar a interface de comunicação com o dispositivo host.

De acordo com [19], um sistema USB é descrito por três áreas fundamentais: a interconexão, os dispositivos e o host. A interconexão descreve como os dispositivos USB são conectados e se comunicam com o host, isto inclui a definição da topologia do barramento, as relações inter-camadas, os modelos de fluxo de dados e a listagem USB. O host é o dispositivo controlador, do qual se iniciam todas as transações. Os dispositivos são itens periféricos que recebem ou enviam dados ao host. Em geral, o host é um computador, e os dispositivos são periféricos tais como mouses, teclados, webcams, entre outros.

A topologia do barramento USB é a topologia conhecida por tiered-star (estrela disposta em camadas/níveis). Esta topologia permite que cada nó possa representar uma função ou outro hub no qual se interliguem mais dispositivos.

Todas as transações do barramento envolvem a transmissão de até três pacotes. Cada transação se inicia pelo controlador USB do host, que envia um pacote USB descrevendo o tipo e a direção da transação, o endereço do dispositivo USB e o número do ponto final (endpoint). O ponto final de um dispositivo é a porção endereçável dele, que é a fonte de informação em um fluxo de comunicações entre o host e o próprio. O número de endpoint

é um valor de 4 bits entre 0H e FH, inclusive, associado a um ponto final de um periférico USB.

A arquitetura USB comprehende quatro tipos básicos de transferências de dados:

- **Transferência de Controle:** Usada para configurar um dispositivo no instante de sua conexão e pode ser usada para outros propósitos específicos, incluindo controle de outros pipes no dispositivo;

- **Transferência do tipo Bulk:** Gerada e consumida em grandes quantidades e simultaneamente. Possui uma ampla e dinâmica latitude em transmissões de reserva;

- **Transferência de Interrupção:** Usada para caracteres ou coordenadas com percepções humanas ou características de respostas regenerativas;

- **Transferência Isossíncrona de Dados:** Ocupa uma quantidade pré-negociável da banda de transmissão do barramento, com a distribuição de pulsos. Chamada também de transferência de correntes em tempo real (streaming real-time transfers);

Estes tipos de transferência são implementados por componentes simples no kit de desenvolvimento escolhido para o projeto. Maiores detalhes sobre os tipos de transferência e como elas são utilizadas estão descritos nas próximas seções deste documento.

### 5.1.2 Gerador de Transport Stream

Como o objetivo do projeto é a captura do sinal de TV Digital, foram utilizadas as instalações e equipamentos de TV Digital disponíveis no Laboratório de Sistemas Abertos da Escola Politécnica da USP. O equipamento é um gerador e gravador de Transport Stream, baseado no padrão europeu de TV Digital (DVB). Portanto, foram necessárias adaptações aos padrões de Transport Stream, de forma que vídeos gerados e obtidos pelo grupo pudessem ser transmitidos adequadamente pelo equipamento.

O DTV Recorder Generator DVRG da Rohde & Schwarz possui diversas interfaces de entrada e saída de Transport Stream, sendo responsável pela sincronização e geração dos sinais de clock e sincronização do sinal nas diferentes saídas. Os padrões mais utilizados para realizar a interface entre dispositivos de geração e transmissão de Transport Stream são a interface SPI (Synchronous Parallel Interface) e a interface ASI (Asynchronous Serial Interface), detalhadas posteriormente neste documento.

O gerador pode ser controlado via acesso remoto, pelo qual os arquivos de vídeo são carregados e codificados no padrão proprietário do equipamento. Devido a restrições em

Figura 5.3: Gerador de TS da Rohde & Schwarz com interface SPI

relação à capacidade do equipamento ao gerar os sinais de sincronia, é necessário gerar arquivos de Transport Stream sem variação de taxa de bits (bitrate constante), além de outras especificações que permitam ao equipamento transmitir os pacotes contidos no arquivo.

### 5.1.3 Interfaces e Padrões

Conforme mencionado anteriormente, os padrões mais utilizados para a transmissão são os padrões definidos na especificação técnica do padrão europeu DVB [23]. Nesta especificação são definidas duas interfaces para transmissão dos pacotes de TS, cada uma com diferentes taxas de transmissão e formato dos dados. A seguir serão detalhadas as duas interfaces, bem como a utilização da interface SPI na implementação do dispositivo de captura USB.

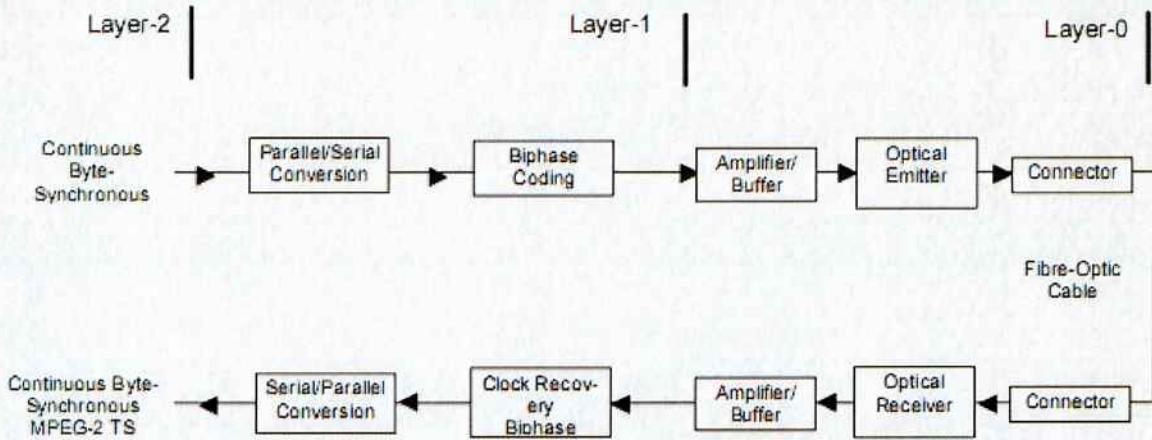

#### Interface ASI

A interface ASI é uma interface cujo objetivo é ter uma grande taxa de transmissão de dados, uma vez que pode ser implementada sob diferentes meios físicos de transmissão, seja via cabo coaxial, fibra ótica ou outros. Por se tratar de um canal serial, todos os bits são transmitidos em série, havendo necessidade de uma organização dos pacotes de forma que seja possível sincronizar o sinal e obter informações sobre o clock e bitrate do vídeo sendo transmitido.

Para tanto, a interface ASI está organizada em três camadas. Conforme pode ser observado pela Figura 5.4 A camada dois é a responsável pela definição dos pacotes de TS (188 ou 204 bytes), bem como a inserção do byte de sincronia (0x47) para sincronização dos pacotes. A camada um é a responsável pela codificação dos dados no formato 8B/10B,

Figura 5.4: Camadas da interface ASI

de forma a inserir bits de redundância para correção de erros. Finalmente, a camada zero é a física, responsável pela transmissão e recepção dos bits.

A interface prevê uma taxa constante de 270 Mbps, e caso a fonte não possua dados a serem transmitidos nesta taxa, devem ser inseridos pacotes extra de sincronia de forma a manter a taxa de bits constante. Devido a esta taxa relativamente alta de operação, o grupo optou pelo padrão SPI detalhado a seguir, de forma que a freqüência de leitura dos dados fosse menor, por se tratar de uma interface paralela ao invés de serial como a ASI.

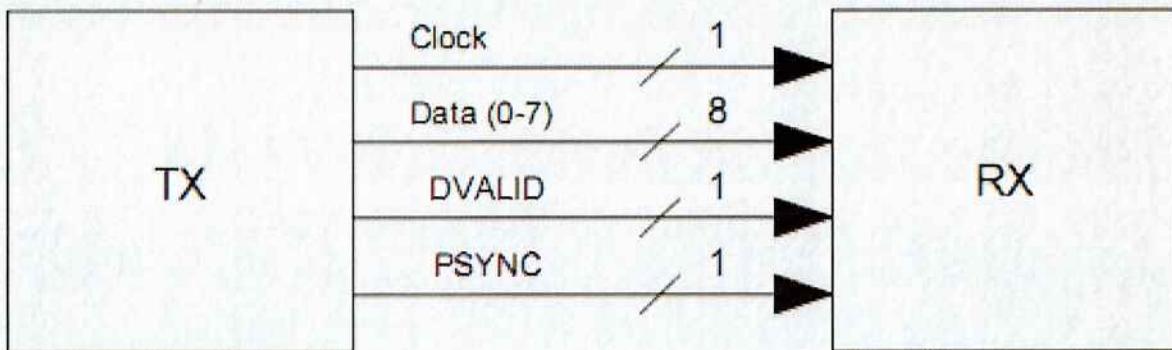

### Interface SPI

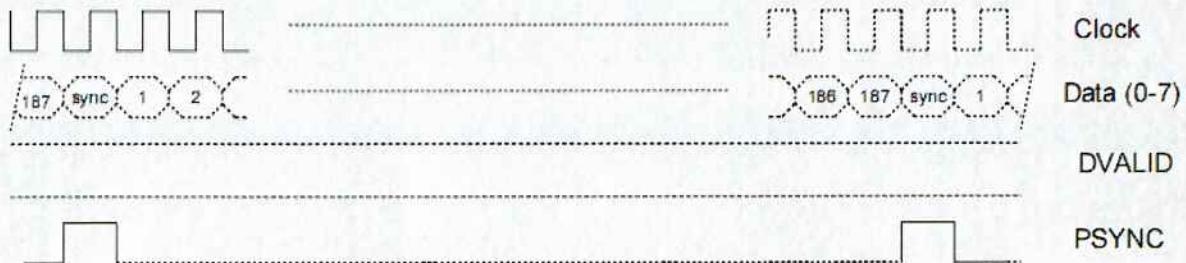

A interface SPI baseia-se na transmissão paralela dos bytes, além de acrescentar bits de sincronia e clock de forma a facilitar a transmissão e recepção dos bits de informação. Como a interface utiliza o padrão LVDS para a transmissão física dos dados, são necessários dois fios para a transmissão de um único sinal lógico. Assim, a interface utiliza um conector D-subminiatura de 25 pinos [26], destinando 16 pinos para a transmissão do byte de dados, dois para o sinal de clock, dois para o sinal de sincronia e outros dois para o bit de sinalização da validade do byte, conforme pode ser observado na Figura 5.5.

Conforme a Figura 5.6, a sincronização do sinal é feita pelo bit de sincronia (PSYNC), cuja função é sinalizar o início de cada pacote de 188 ou 204 bytes que está sendo transmitido. A sincronia também é garantida pelo sinal de clock, que é um sinal cuja freqüência varia conforme a taxa de dados do TS sendo transmitido. Assim, um TS de bitrate de 20Mbps irá gerar um sinal de clock de aproximadamente 2,5MHz.

O bit de validade (DVALID) serve para sinalizar a validade dos bytes transmitidos, especificamente quando a transmissão utilizar pacotes de tamanho variável ou de 204 bytes.

Figura 5.5: Interface de transmissão paralela (SPI)

Figura 5.6: Formato de transmissão de pacotes de 188 bytes

Este sinal irá então ser ativado toda vez que bytes vazios forem transmitidos para completar a quantidade total de 204 bytes.

Esta foi a interface escolhida para o projeto do dispositivo de captura USB, uma vez que podemos aproveitar a interface paralela para obtermos taxas de transmissão altas com uma baixa freqüência de clock, algo limitante no caso de uso de FPGAs e da interface USB, cuja maior freqüência de operação é 48MHz. Foi possível assim utilizar a grande quantidade de pinos de I/O disponíveis no Kit de Desenvolvimento para a implementação da interface paralela entre a FPGA e a porta paralela SPI. Além disso, o sinal de clock e bit de sincronia existente nessa interface permite um controle maior na recepção dos dados.

Desta forma, o dispositivo desenvolvido consegue capturar vídeos com taxa variável de bitrate, podendo capturar vídeos com taxas de bitrate de até 300Mbps. Durante os testes do dispositivo, foram utilizados arquivos de TS com taxas de 7, 19 e até 49 Mbps, demonstrando o funcionamento correto do dispositivo para diferentes taxas de transmissão de dados.

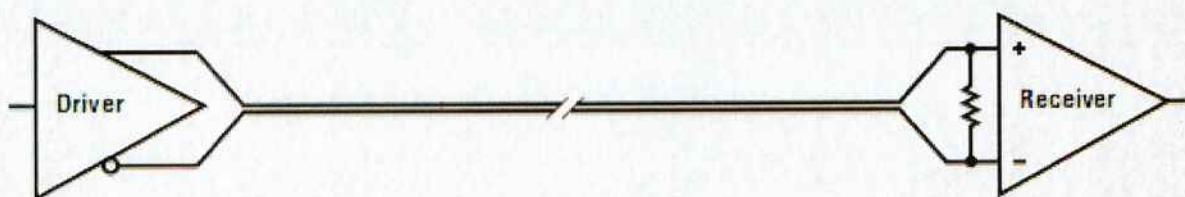

Figura 5.7: Interconexão entre transmissor e receptor dos sinais

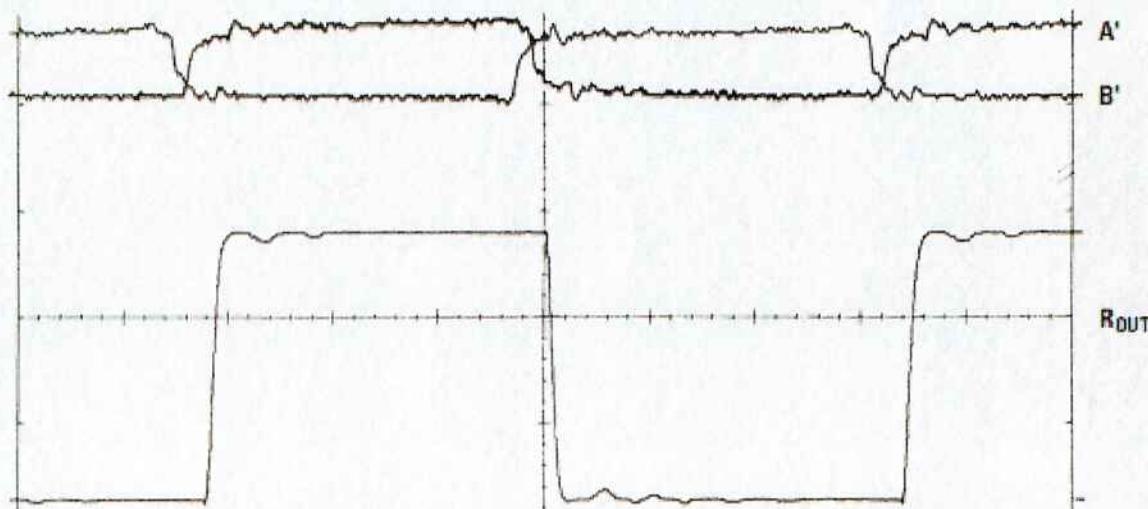

Figura 5.8: Geração de sinal lógico a partir dos sinais analógicos

### Padrão LVDS

Ambas as interfaces de transmissão definidas anteriormente utilizam o padrão elétrico *Low-Voltage Differential Signaling* (LVDS), padrão que utiliza técnicas de circuitos analógicos de alta velocidade para prover transferência de dados de vários gigabits sobre um condutor de cobre.

Baseando-se em uma dupla de condutores, o padrão utiliza sinais de baixíssima amplitude (cerca de 180 milivolts) que reduzem a quantidade de interferência causada pela irradiação eletromagnética dos sinais. Além disso, o padrão permite a redução da potência dissipada no circuito de transmissão, uma vez que trabalha com sinais de base constante, havendo somente a variação de milivolts para a modulação dos sinais lógicos.

O sinal lógico é obtido a partir da comparação entre os dois sinais analógicos, gerando um sinal digital “1” caso a diferença seja positiva, e “0” caso contrário. O padrão foi desenvolvido principalmente para aplicações de TV Digital, que necessitam de grandes taxas de transmissão e baixo consumo de energia e simplicidade nos meios de transmissão.

Além disso, o padrão também é suportado pela maioria das FPGAs existentes no mercado, uma vez que disponibiliza uma forma de barramento de alta velocidade e baixo consumo. O padrão é utilizado também para comunicação entre unidades de processamento e memórias, uma vez que permite taxas de até gigabits e pode ser utilizado sem maiores problemas em relação à interferência eletromagnética.

#### 5.1.4 Kit de Desenvolvimento