**UNIVERSIDADE DE SÃO PAULO

ESCOLA DE ENGENHARIA DE SÃO CARLOS**

**PROJETO DE AMPLIFICADORES DE

BAIXO RUÍDO USANDO ALGORITMOS

META-HEURÍSTICOS**

São Carlos

Novembro de 2014

**GILBERTO VOLPE NETO**

**PROJETO DE AMPLIFICADORES DE

BAIXO RUÍDO USANDO ALGORITMOS

META-HEURÍSTICOS**

Trabalho de Conclusão de Curso apresentado à Escola de Engenharia de São Carlos, da Universidade de São Paulo, como parte dos requisitos para obtenção do título de Engenheiro de Computação.

ORIENTADOR: Prof. Dr. João Navarro Soares Junior

São Carlos

Novembro de 2014

AUTORIZO A REPRODUÇÃO TOTAL OU PARCIAL DESTE TRABALHO,

POR QUALQUER MEIO CONVENCIONAL OU ELETRÔNICO, PARA FINS

DE ESTUDO E PESQUISA, DESDE QUE CITADA A FONTE.

V931p

Volpe Neto, Gilberto

Projeto de amplificadores de baixo ruido usando

algoritimos meta-heuristicos / Gilberto Volpe Neto;

orientador João Navarro Junior. São Carlos, 2014.

Monografia (Graduação em Engenharia de Computação)

-- Escola de Engenharia de São Carlos da Universidade

de São Paulo, 2014.

1. Amplificador de baixo ruido. 2. LNA. 3.

Algoritimos meta-heuristicos. 4. Indutor. I. Titulo.

## FOLHA DE APROVAÇÃO

**Nome:** Gilberto Volpe Neto

**Título:** "Projeto de amplificadores de baixo ruído usando algoritmos meta-heurísticos"

**Trabalho de Conclusão de Curso defendido em** 20/11/2014.

**Comissão Julgadora:**

Prof. Dr. João Navarro Soares Júnior

(Orientador) - SEL/EESC/USP

**Resultado:**

APROVADO

Prof. Titular Amílcar Careli Cesar

SEL/EESC/USP

APROVADO

Prof. Dr. João Paulo Pereira do Carmo

SEL/EESC/USP

APROVADO

**Coordenador do Curso Interunidades - Engenharia de Computação:**

Prof. Associado Evandro Luís Linhari Rodrigues

## **Agradecimentos**

Inicialmente agradeço a minha família por todo o esforço e carinho concedidos para que eu pudesse concluir o sonho de me formar pela Universidade de São Paulo.

Não posso esquecer de agradecer também a todos os companheiros que se aventuraram durante a graduação, acompanhando nas obrigações e lazeres. Um abraço especial para Adailto Aparecido Caramano, Carolina Catarina da Silva, Júlio César Simões Mathias, Guilherme Machado Gagliardi, Lídia Tomoko Sawakuchi, Leonardo Lourenço Crespilho, Lucas Aoki Heredia, Paola Lanzoni e Rafael Seiji Ishibe.

Agradeço as oportunidades de aplicar o conhecimento adquirido durante os anos de graduação que só foram possíveis graças a I-Healthsys e sua fantástica equipe, com o Caio Moraes Zanon, Éder Issao Ishibe, Marcelo Prado e Tales Santini, e ao Grupo Ultra.

Agradeço, por fim, ao professor doutor João Navarro Soares Junior por toda a orientação e paciência na condução do presente trabalho.

## RESUMO

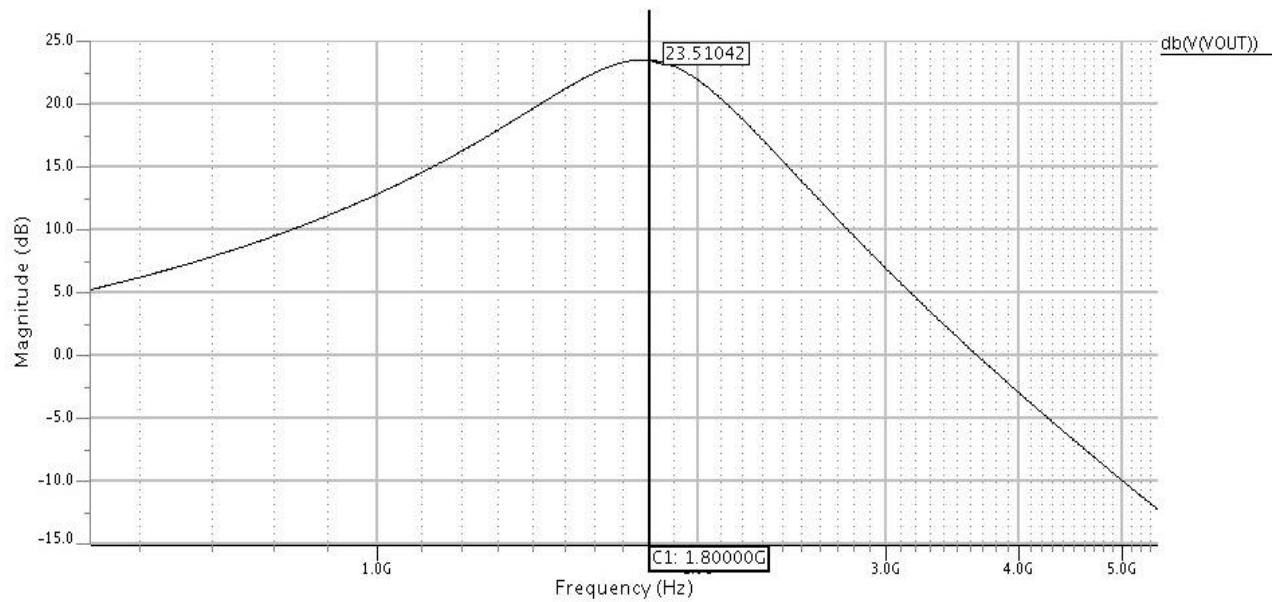

Amplificadores de baixo ruído, LNAs, são circuitos que amplificam sinais introduzindo pouco ruído e são utilizados em diversas aplicações modernas, como celulares e computadores móveis. O projeto de um LNA aparenta ser simples, pelos poucos componentes que o compõe, contudo a alta correlação entre os seus parâmetros introduz consideráveis dificuldades. Para contornar essas dificuldades, o presente trabalho faz uso dos algoritmos meta-heurísticos, *Particle Swarm Optimization* e *Simulated Annealing*, para projeto e otimização de LNAs. Esses algoritmos necessitam avaliar milhares de indivíduos, o que no presente trabalho é feito por simulações elétricas. Com isso, o tempo gasto para cada análise se torna um gargalo. Um dos elementos mais importante dos LNAs operando em RF é o indutor. A obtenção do seu modelo elétrico pode ser demorada quando se aplicam softwares extratores. Para acelerar a obtenção do modelo do indutor foi utilizado um conjunto de equações. Para analisar a viabilidade do uso de meta-heurísticas e equações para extração de modelos de indutores foram usadas quatro topologias para projeto de amplificadores de baixo ruído operando em 1,8 GHz, com tensão de alimentação de 2,0 e 3,0 V e uma tecnologia CMOS de 0,35  $\mu$ m. Para LNAs sem casamento de impedância na saída foram obtidos resultados, por simulação, tão bons quanto ganho de tensão de 23,5 dB, figura de ruído de 3,2 dB, ponto de intersecção de terceira ordem de 15,0 dBm e consumo de potência de 5,5 mW. Para LNAs com casamento de impedância na saída se atingiu resultados como ganho de potência de 23,5 dB, figura de ruído de 3,0 dB, ponto de intersecção de terceira ordem de -8,4 dBm e consumo de potência de 22,8 mW. Os resultados obtidos foram comparados com resultados da literatura mostrando que a utilização de algoritmos meta-heurísticos e equações para modelar indutores é eficaz no projeto de amplificadores de baixo ruído.

**Palavras Chaves:** Amplificador de baixo ruído, LNA, algoritmos meta-heurísticos, indutor.

## ABSTRACT

Low-noise amplifiers, LNAs, are circuits that amplify signals introducing small quantity of noise and are used in many modern applications, such as mobile phones and computers. The design of an LNA appears to be simple, because of the few components that compose it, however the high correlation among its parameters introduces considerable difficulties. To circumvent these difficulties, this paper makes use of metaheuristic algorithms, Particle Swarm Optimization and Simulated Annealing, for the design and optimization of LNAs. These algorithms need to evaluate thousands of individuals, which in this work is done by electrical simulations. With this, the time spent for each analysis becomes a bottleneck. One of the most important elements of LNAs, when they operate in RF, is the inductor. Obtaining your electric model can be time consuming when softwares of extraction were applied. To accelerate the attainment of the inductor model a set of equations was used. To analyze the feasibility of the use of metaheuristics and equations to modeling the inductors, four topologies were employed to design low-noise amplifiers operating at 1.8 GHz, with voltage of 2.0 and 3.0 V and a CMOS technology 0.35 um. For LNAs, without impedance matching, the output results reached, simulation, are gain of 23.5 dB, noise figure of 3.2 dB, the intersection point of the third order of 15.0 dBm and power consumption of 5.5 mW. For LNAs with impedance matching, the results reached are gain of 23.5 dB, noise figure of 3.0 dB, the intersection point of the third order of -8.4 dBm and power consumption of 22.8 mW. The results were compared with results from the literature showing that the use of metaheuristic algorithms and equations for inductor model is effective for the design of low-noise amplifiers.

**Keywords:** Low-noise amplifier, LNA, metaheuristic algorithms, inductor.

# Sumário

|                                                   |    |

|---------------------------------------------------|----|

| Agradecimentos.....                               | 5  |

| RESUMO .....                                      | 6  |

| ABSTRACT .....                                    | 7  |

| Lista de Figuras .....                            | 11 |

| Lista de Tabelas .....                            | 15 |

| Capítulo 1 - Introdução.....                      | 17 |

| Capítulo 2 – Revisão Teórica.....                 | 23 |

| Fator/Figura de ruído.....                        | 23 |

| Transistores MOS.....                             | 23 |

| Efeito de Corpo.....                              | 26 |

| Modulação de Canal .....                          | 26 |

| Transcondutância .....                            | 26 |

| Capacitâncias Intrínsecas .....                   | 27 |

| Modelo de pequenos sinais.....                    | 31 |

| Indutores Integrados.....                         | 32 |

| Degradação em indutores passivos integrados ..... | 34 |

| Efeito Pelicular .....                            | 34 |

| Efeito de Proximidade .....                       | 35 |

| Correntes Eddy .....                              | 36 |

| Círculo Equivalente .....                         | 36 |

| Indutância .....                                  | 38 |

| Resistência Série.....                            | 38 |

| Capacitância entre os Segmentos.....              | 38 |

| Capacitância do Isolante .....                    | 39 |

|                                                                             |    |

|-----------------------------------------------------------------------------|----|

| Capacitância do Substrato.....                                              | 39 |

| Resistência do Substrato .....                                              | 39 |

| Limitações do Circuito Equivalente.....                                     | 39 |

| Amplificadores de baixo ruído – LNA.....                                    | 40 |

| Parâmetros de projeto.....                                                  | 40 |

| Ruído.....                                                                  | 40 |

| Ganho.....                                                                  | 41 |

| Linearidade .....                                                           | 42 |

| Estabilidade.....                                                           | 44 |

| Topologias de LNAs .....                                                    | 44 |

| Características da arquitetura FCCDI.....                                   | 47 |

| Algoritmos Meta-heurísticos.....                                            | 54 |

| <i>Simulated Annealing - SA</i> .....                                       | 55 |

| <i>Particle Swarm Optimization - PSO</i> .....                              | 55 |

| Capítulo 3 – Metodologia.....                                               | 57 |

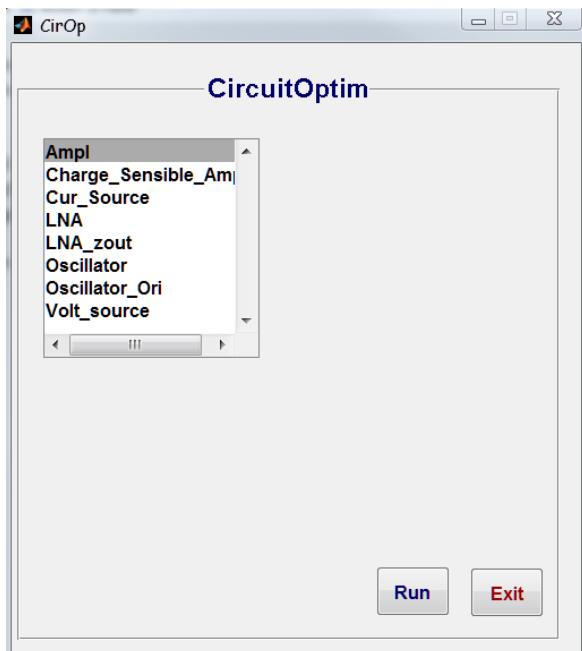

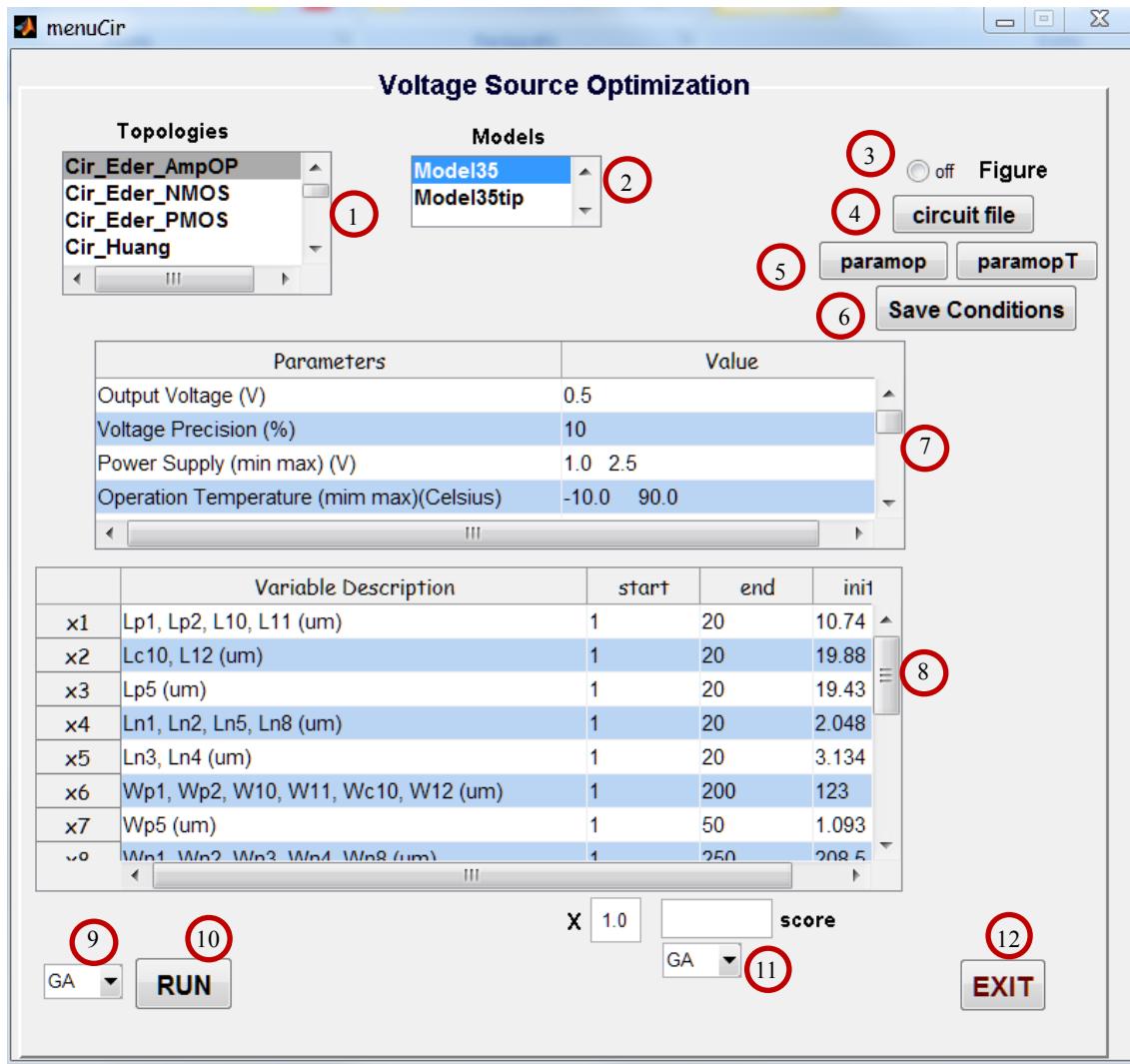

| CirOp.....                                                                  | 57 |

| Função objetivo .....                                                       | 59 |

| Modelo elétrico dos indutores integrados .....                              | 61 |

| Topologias de LNA utilizadas .....                                          | 62 |

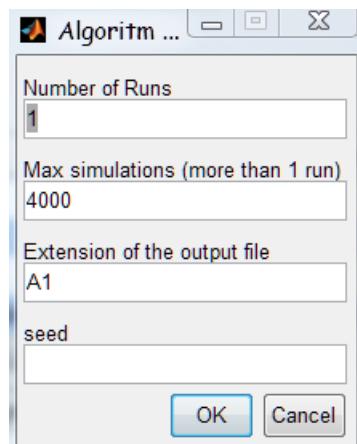

| Configuração dos algoritmos PSO e SA .....                                  | 65 |

| Capítulo 4 – Resultados.....                                                | 66 |

| Validação das equações de modelo elétrico dos indutores .....               | 66 |

| Resultados Otimizações .....                                                | 70 |

| Tempo de execução e comparação dos resultados entre ASITIC e equações ..... | 83 |

| Capítulo 5 – Conclusões.....                                                | 87 |

| Bibliografia.....                                                           | 89 |

|                                                                                |     |

|--------------------------------------------------------------------------------|-----|

| Apêndices e Anexos .....                                                       | 95  |

| Apêndice A – Utilização do CirOp .....                                         | 96  |

| Apêndice B – Código para simulações e medições dos parâmetros.....             | 100 |

| Apêndice C – Código para extração do modelo elétrico do indutor integrado..... | 108 |

| Apêndice D – Resultados das equações de Resistência de Substrato.....          | 111 |

| Anexo A – Parâmetros do modelo BSIM3v3 .....                                   | 114 |

| Anexo B – Tecnologia usada por ASITIC .....                                    | 116 |

## **Lista de Figuras**

|                                                                                                                         |    |

|-------------------------------------------------------------------------------------------------------------------------|----|

| Figura 1. Blocos básicos de um sistema RF .....                                                                         | 17 |

| Figura 2. Bloco transmissor e receptor, em destaque o LNA. ....                                                         | 18 |

| Figura 3. Representação de um circuito transceptor RF completo. ....                                                    | 19 |

| Figura 4. Esquemático de um LNA. ....                                                                                   | 20 |

| Figura 5. Parâmetros do projeto de LNA. ....                                                                            | 20 |

| Figura 6. Estrutura física de um transistor NMOS. ....                                                                  | 24 |

| Figura 7. Capacitâncias de overlap no transistor MOS. ....                                                              | 28 |

| Figura 8. Variação das componentes da capacitância de porta-canal em função de $VGS$ e $VDS$ (tensão dreno-fonte). .... | 28 |

| Figura 9. Detalhamento da região em torno da fonte. ....                                                                | 29 |

| Figura 10. Capacitâncias entre os terminais do transistor NMOS. ....                                                    | 30 |

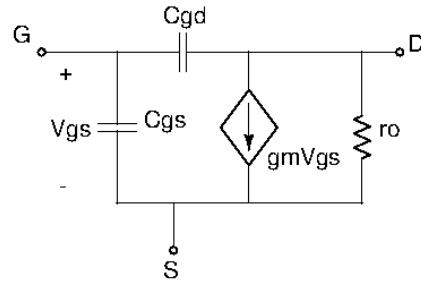

| Figura 11. Modelo de pequenos sinais simples do transistor NMOS. ....                                                   | 31 |

| Figura 12. Modelo de pequenos sinais do transistor NMOS, considerando a modulação de canal. ....                        | 31 |

| Figura 13. Modelo de pequenos sinais para baixas frequências. ....                                                      | 32 |

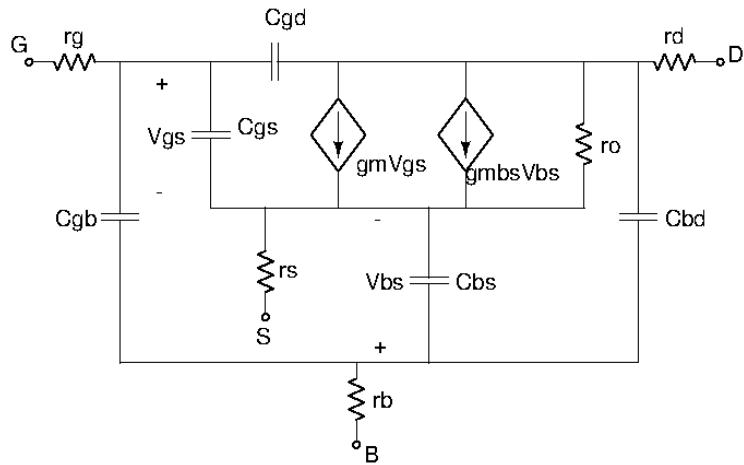

| Figura 14. Modelo de pequenos sinais do transistor NMOS completo. ....                                                  | 32 |

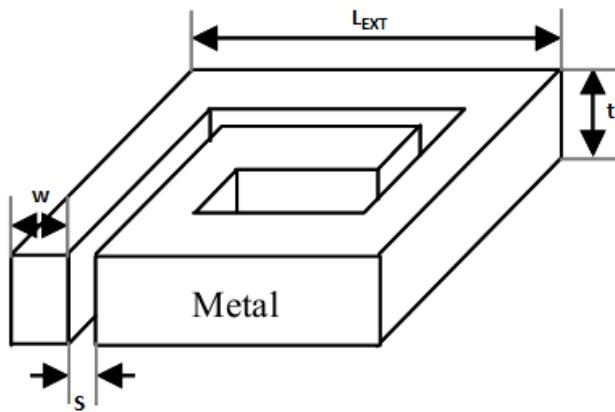

| Figura 15. Indutor retangular e seus parâmetros geométricos. ....                                                       | 33 |

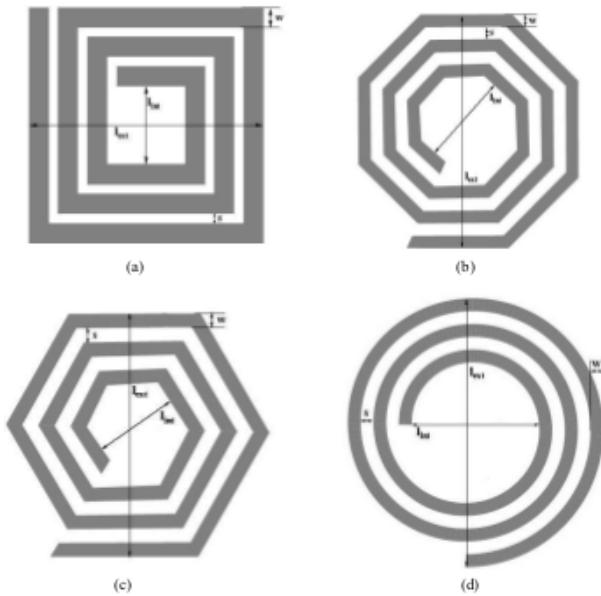

| Figura 16. Formatos de indutores integrados: (a) retangular, (b) octogonal, (c) hexagonal e (d) circular. ....          | 33 |

| Figura 17. Circuito MOS Indutor ativo. ....                                                                             | 34 |

| Figura 18. Distribuição das correntes nos segmentos de um indutor para baixas e altas frequências. ....                 | 35 |

| Figura 19. Correntes induzidas no substrato. ....                                                                       | 36 |

| Figura 20. Modelo equivalente para o indutor integrado. ....                                                            | 37 |

| Figura 21. Espessuras que caracterizam o indutor de uma espira. ....                                                    | 37 |

| Figura 22. Modelo do ruído térmico do resistor. ....                                                                    | 40 |

| Figura 23. Modelo do transistor NMOS considerando o ruído. ....                                                         | 41 |

|                                                                                                                                                                                                                                                                                           |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figura 24. Amplitude de saída versus amplitude de entrada; a) ponto de compressão 1,0 dB e b) ponto de intersecção de terceira ordem.....                                                                                                                                                 | 43 |

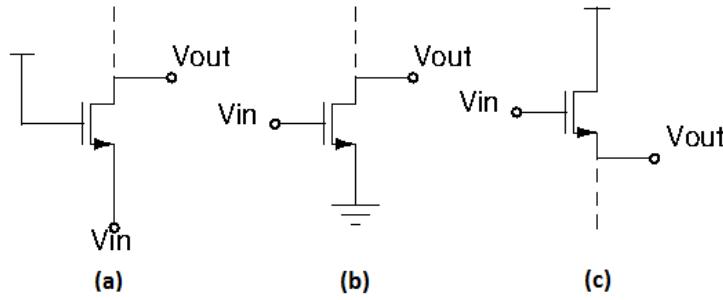

| Figura 25. Configurações de transistores: (a) Porta Comum (PC), (b) Fonte Comum (FC) e (c) Dreno Comum (DC).....                                                                                                                                                                          | 45 |

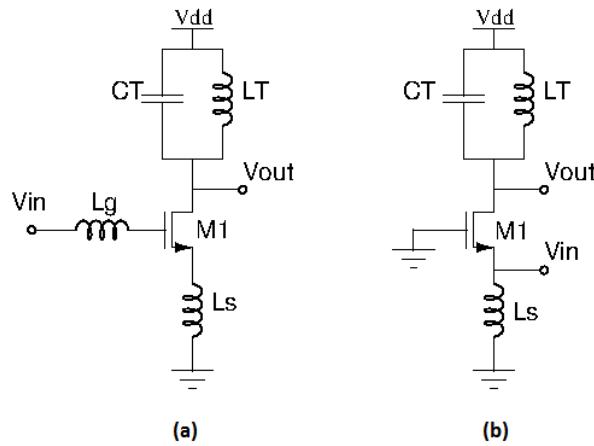

| Figura 26. (a) Configuração FC com DI, (b) Configuração PC com DI.....                                                                                                                                                                                                                    | 46 |

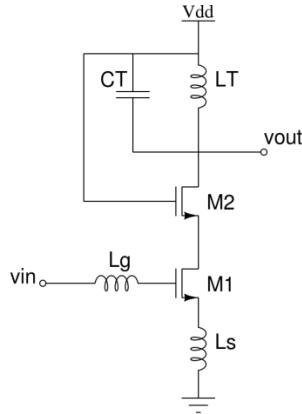

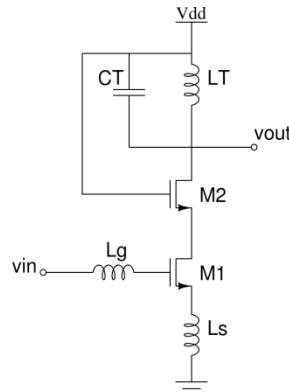

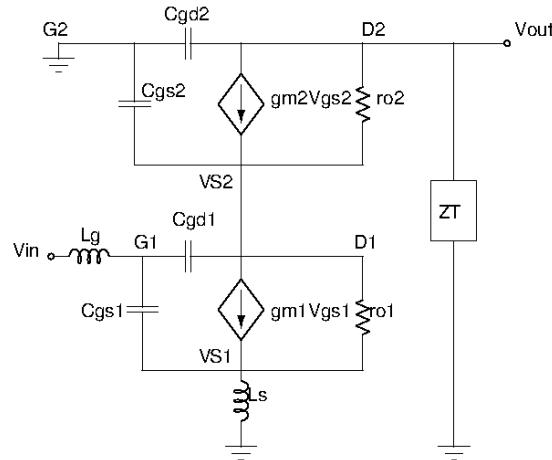

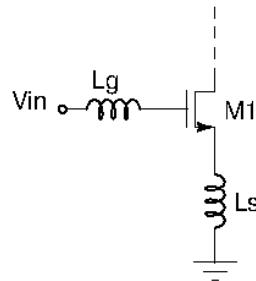

| Figura 27. Fonte comum cascode com degeneração indutiva (FCCDI).....                                                                                                                                                                                                                      | 46 |

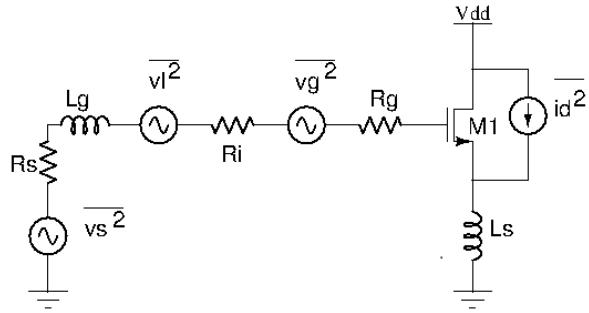

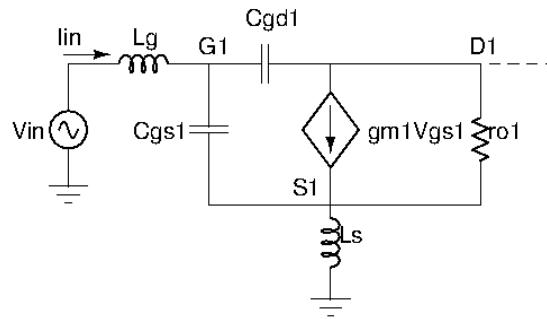

| Figura 28. Circuito para o cálculo do ruído do LNA.....                                                                                                                                                                                                                                   | 48 |

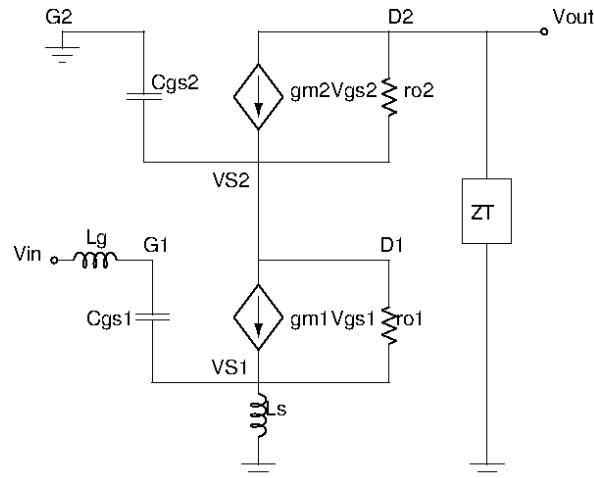

| Figura 29. Modelo pequenos sinais para o cálculo do ganho do LNA.....                                                                                                                                                                                                                     | 49 |

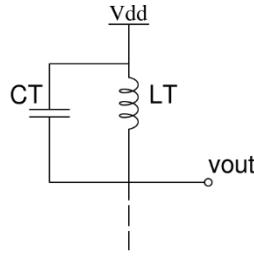

| Figura 30. Rede <i>LTCT</i> para ajuste de frequência de operação para o circuito da Figura 27.....                                                                                                                                                                                       | 50 |

| Figura 31. Modelo de pequenos sinais simplificado para o cálculo do ganho do LNA.....                                                                                                                                                                                                     | 50 |

| Figura 32. Circuito para o casamento de impedância na entrada.....                                                                                                                                                                                                                        | 51 |

| Figura 33. Modelo de pequenos sinais para o circuito da Figura 32.....                                                                                                                                                                                                                    | 51 |

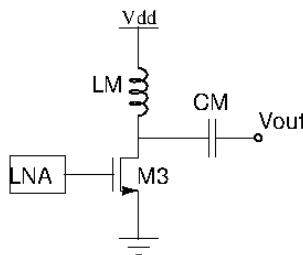

| Figura 34. Circuito para casamento de saída.....                                                                                                                                                                                                                                          | 52 |

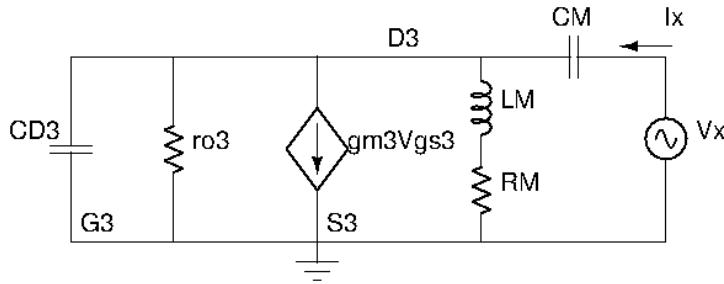

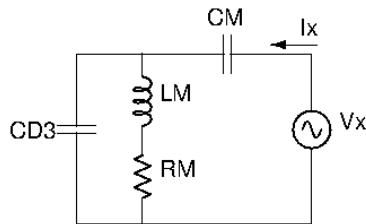

| Figura 35. Modelo de pequenos sinais do circuito da Figura 34.....                                                                                                                                                                                                                        | 53 |

| Figura 36. Simplificação do modelo pequenos sinais da Figura 34.....                                                                                                                                                                                                                      | 53 |

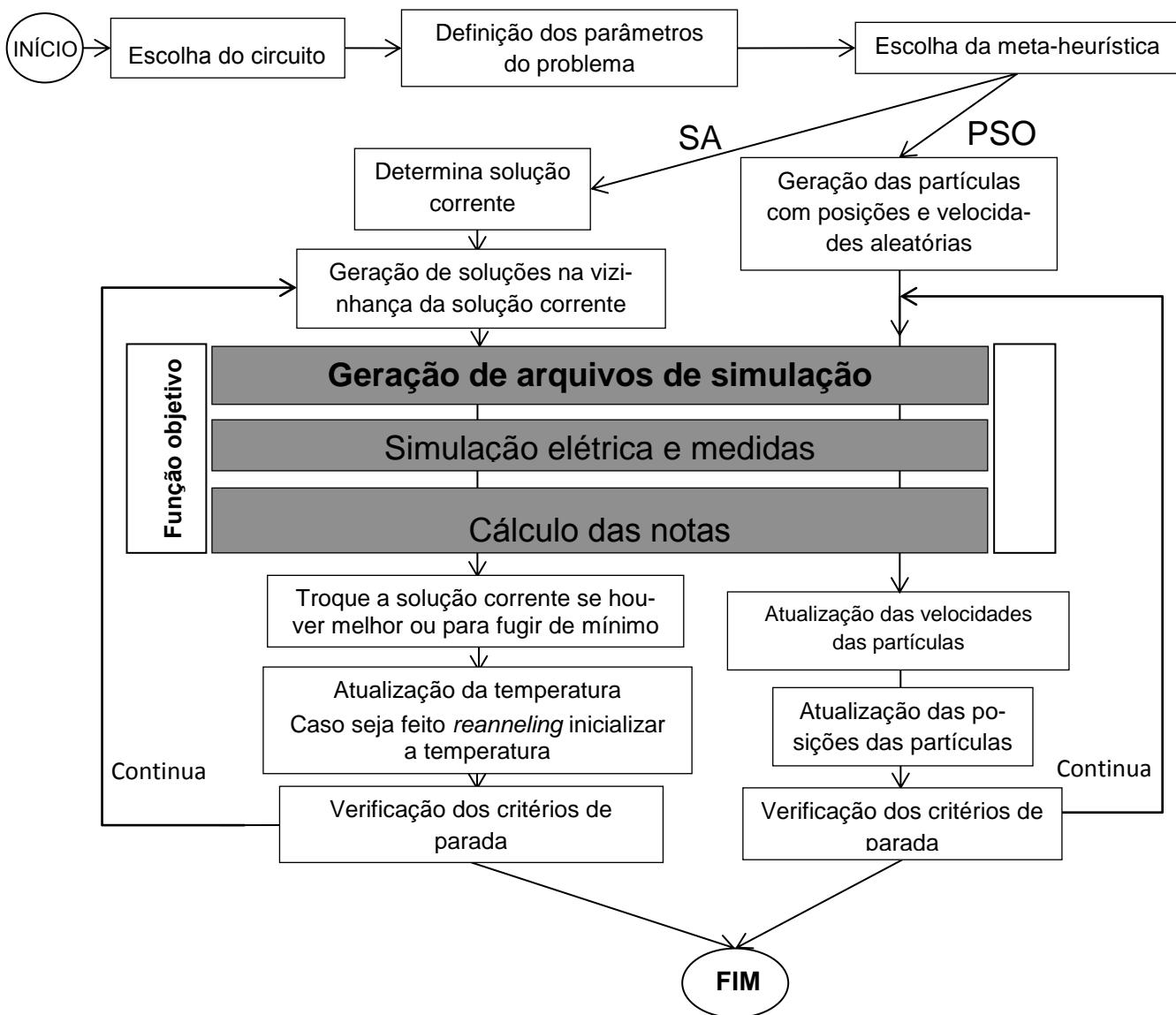

| Figura 37. Diagrama do funcionamento da ferramenta de projeto/otimização com as meta-heurísticas SA e PSO.....                                                                                                                                                                            | 58 |

| Figura 38. Modelo elétrico considerado para os indutores integrados.....                                                                                                                                                                                                                  | 61 |

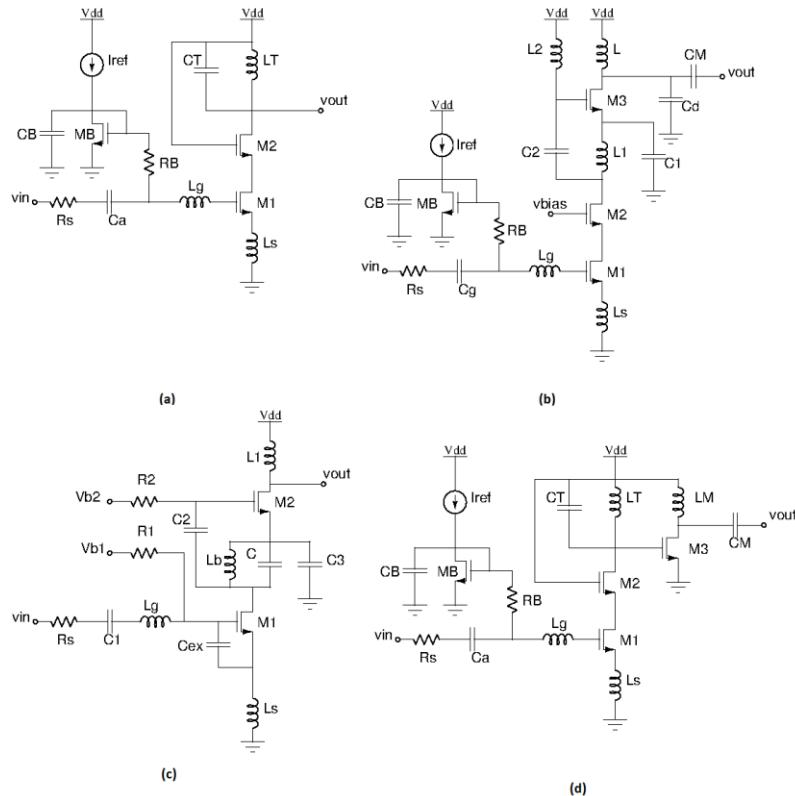

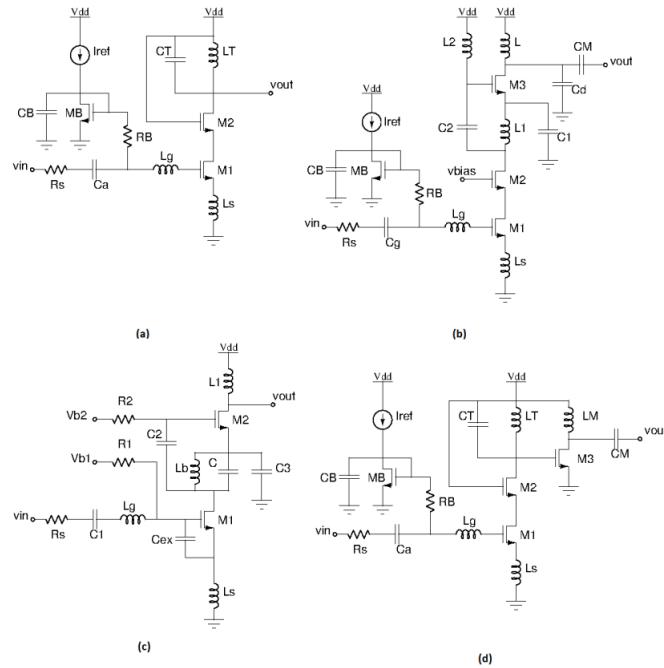

| Figura 39. Topologias utilizadas.....                                                                                                                                                                                                                                                     | 62 |

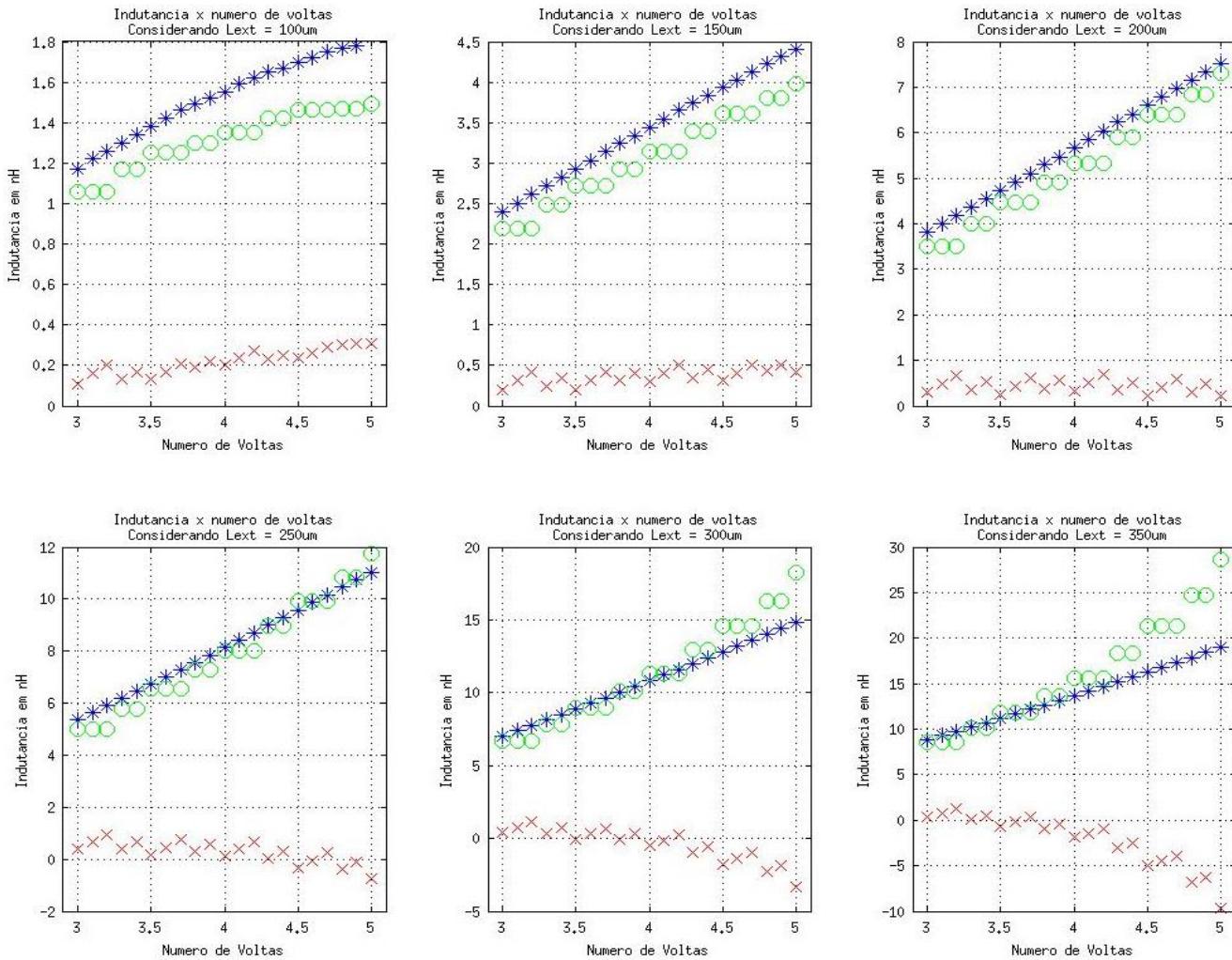

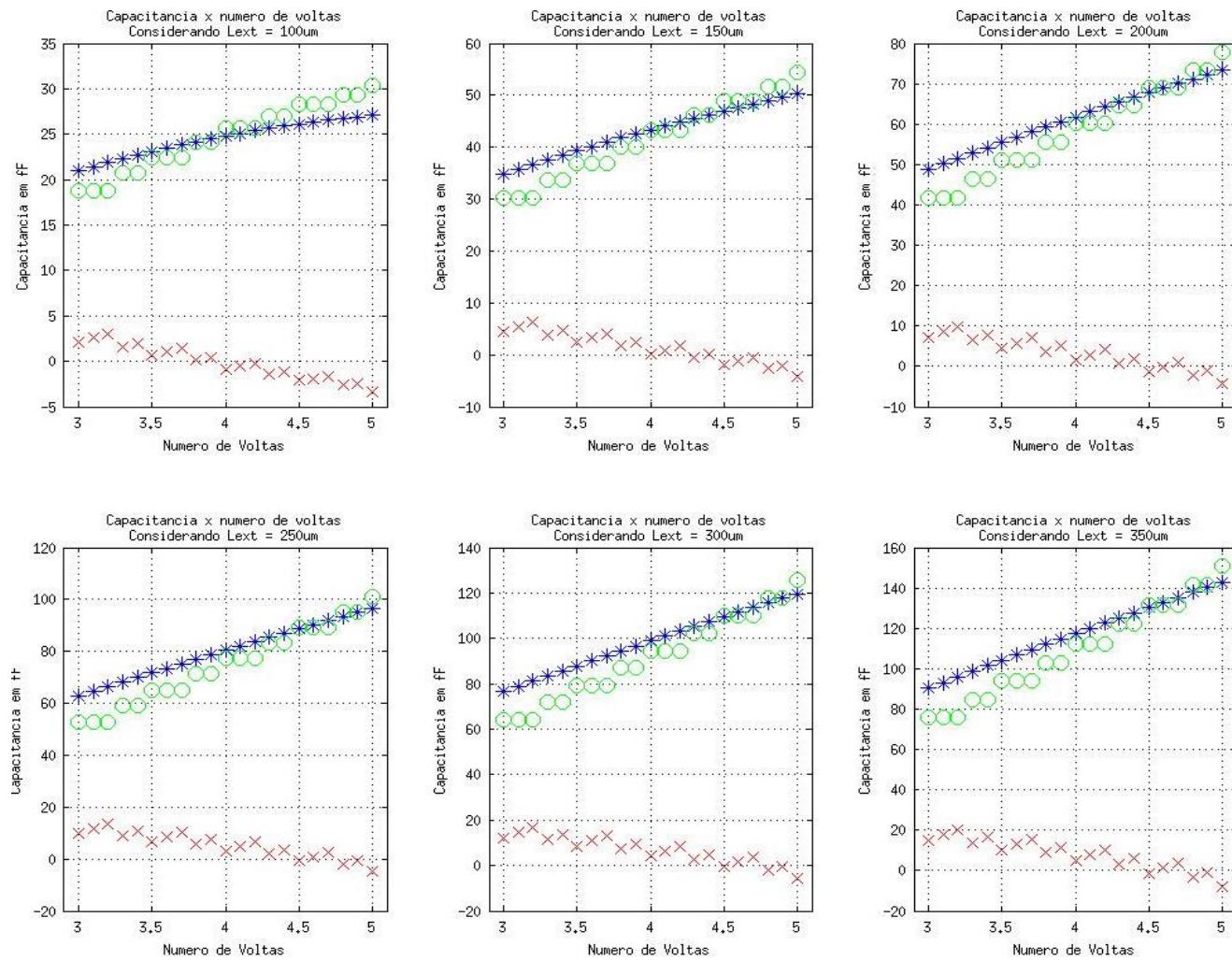

| Figura 40. Indutâncias L geradas pelas equações (asterisco), extraídas pelo ASITIC (círculos) e as diferenças entre os dois valores (x) versus número de voltas do indutor. Diferentes valores de <i>LEXT</i> são empregados (frequência = 1,8 GHz, W = 7,5 $\mu$ m).....                 | 66 |

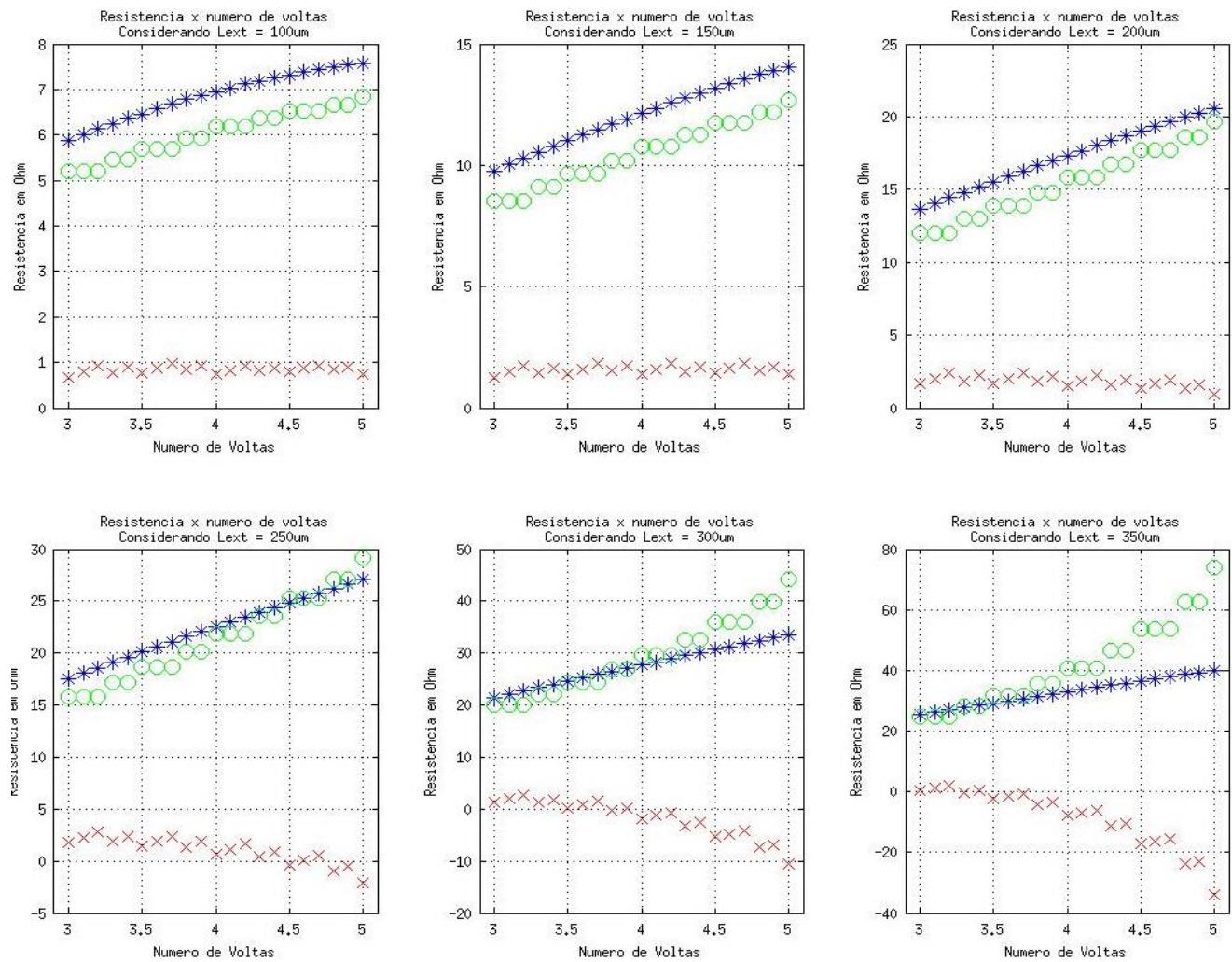

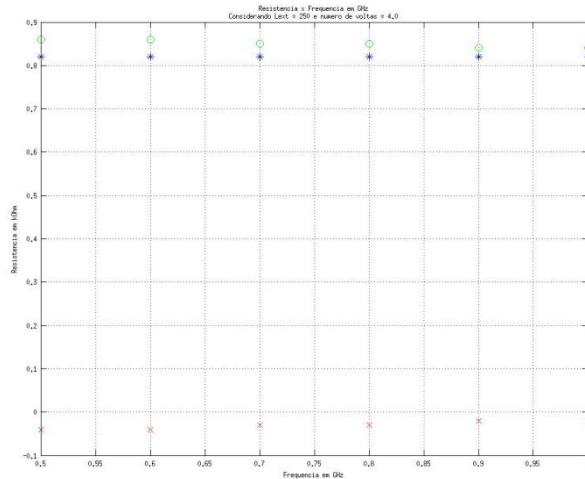

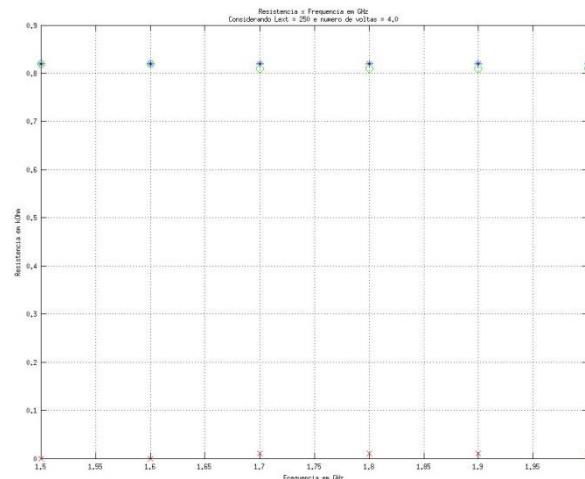

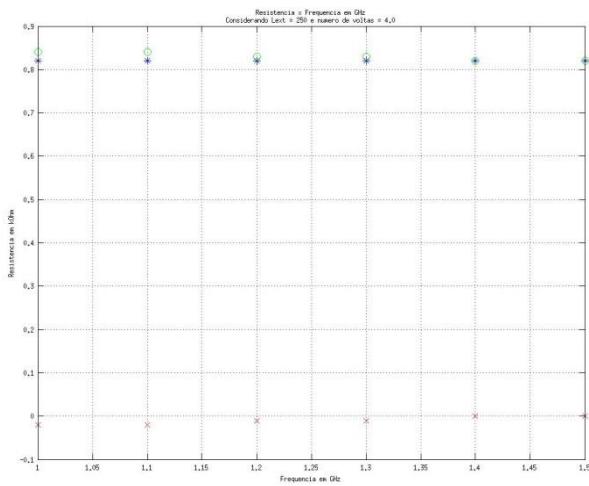

| Figura 41. Resistências em série <i>Rs</i> geradas pelas equações (asterisco), extraídas pelo ASITIC (círculos) e a diferença entre os dois valores(x) versus número de voltas do indutor. Diferentes valores de <i>Lext</i> são empregados (frequência = 1,8 GHz, W = 7,5 $\mu$ m).....  | 67 |

| Figura 42. Capacitâncias de óxido <i>Cox</i> geradas pelas equações (asterisco), extraídas pelo ASITIC (círculos) e a diferença entre os dois valores(x) versus número de voltas do indutor. Diferentes valores de <i>Lext</i> são empregados (frequência =1,8 GHz, W = 7,5 $\mu$ m)..... | 68 |

|                                                                                                                                                                                                                                                                                                               |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

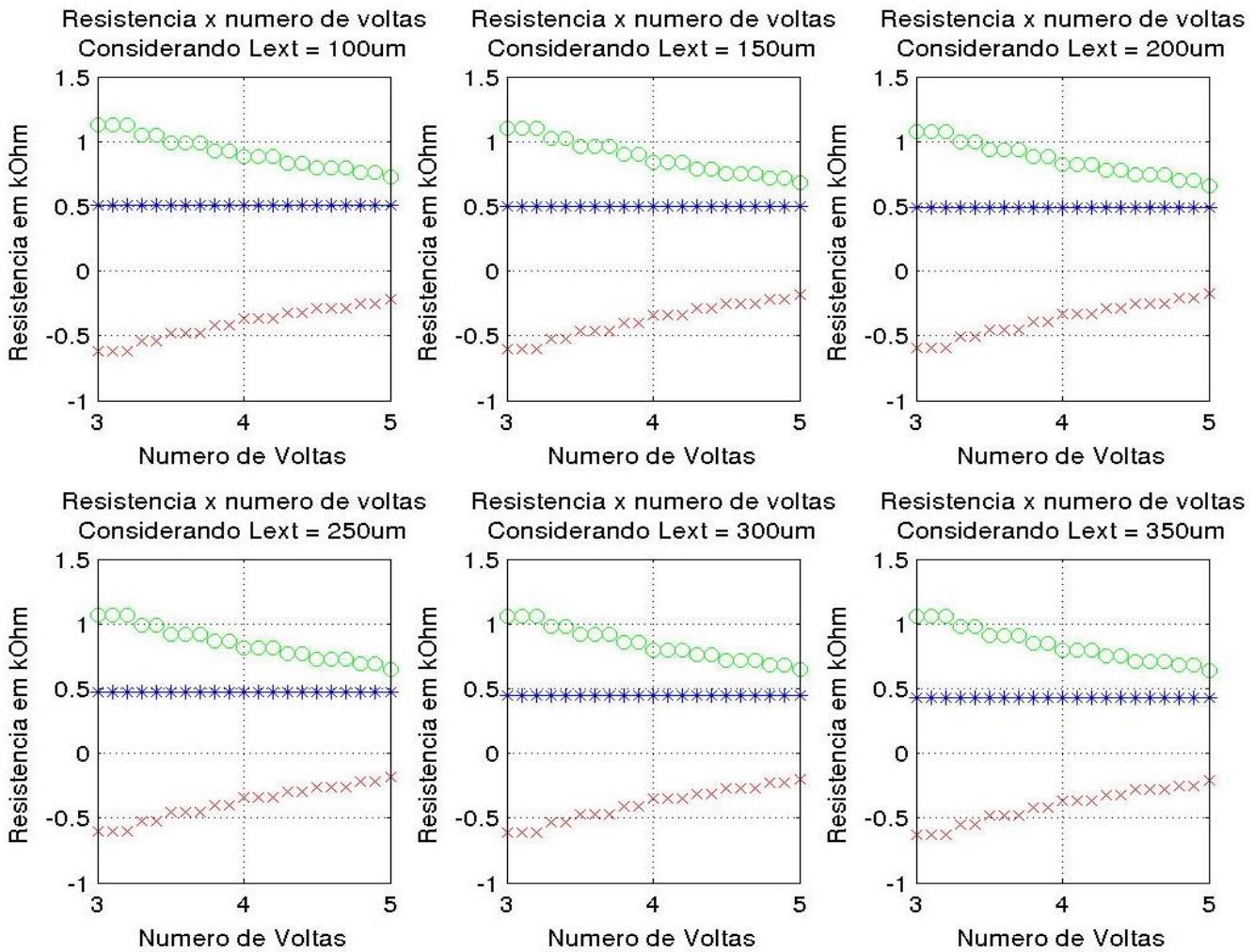

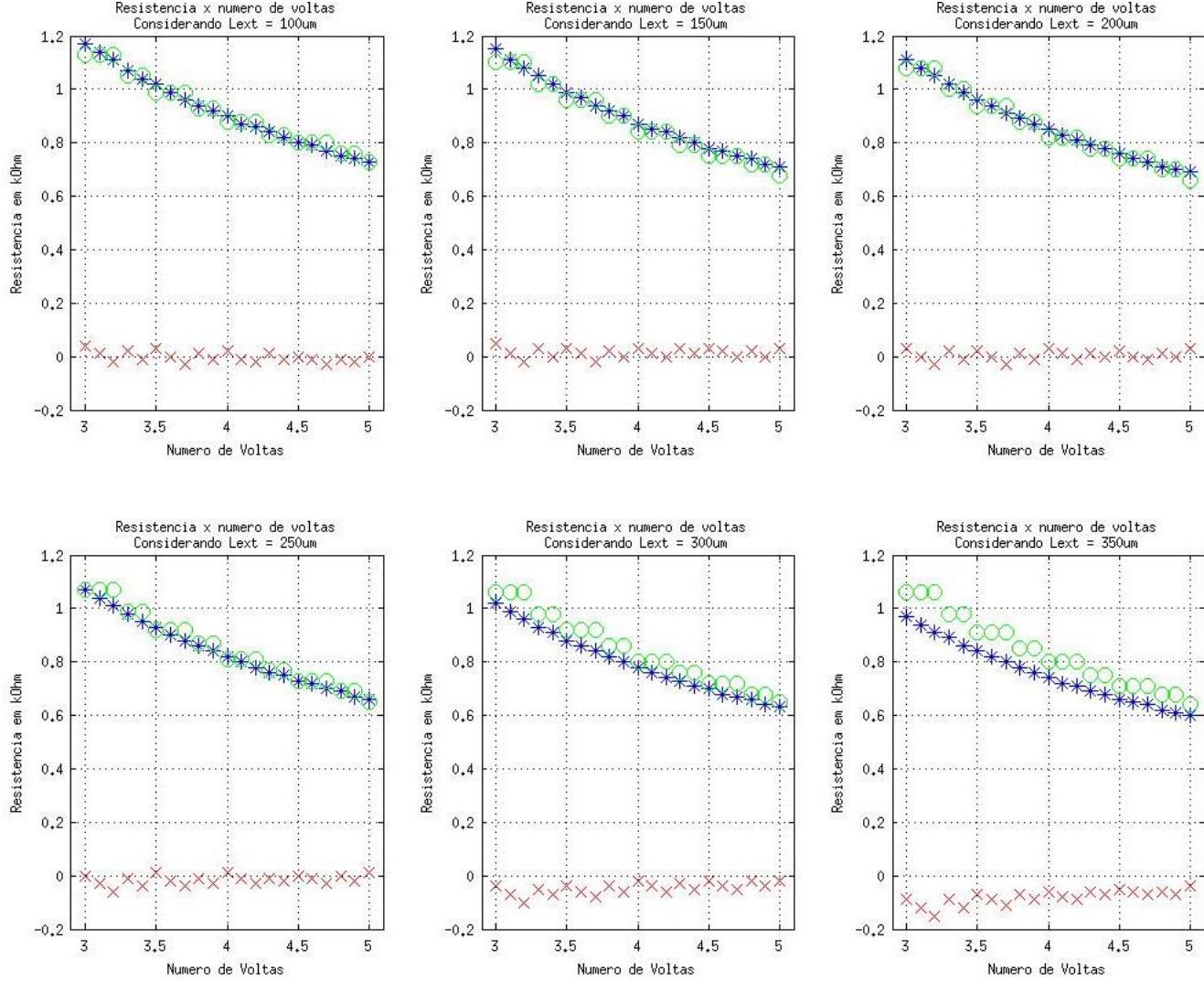

| Figura 43. Resistências de substrato $R_{si}$ geradas pelas equações (asterisco), extraídas pelo ASITIC (círculos) e a diferença entre os dois valores(x) versus número de voltas do indutor. Diferentes valores de $L_{ext}$ são empregados (frequência de 1,8 GHz, $W = 7,5 \mu\text{m}$ ).....             | 69 |

| Figura 44. Resistências de substrato $R_{si}$ geradas pelas equações corrigidas (asterisco), extraídas pelo ASITIC (círculos) e a diferença entre os dois valores(x) versus número de voltas do indutor. Diferentes valores de $L_{ext}$ são empregados (frequência de 1,8 GHz, $W = 7,5 \mu\text{m}$ ) ..... | 70 |

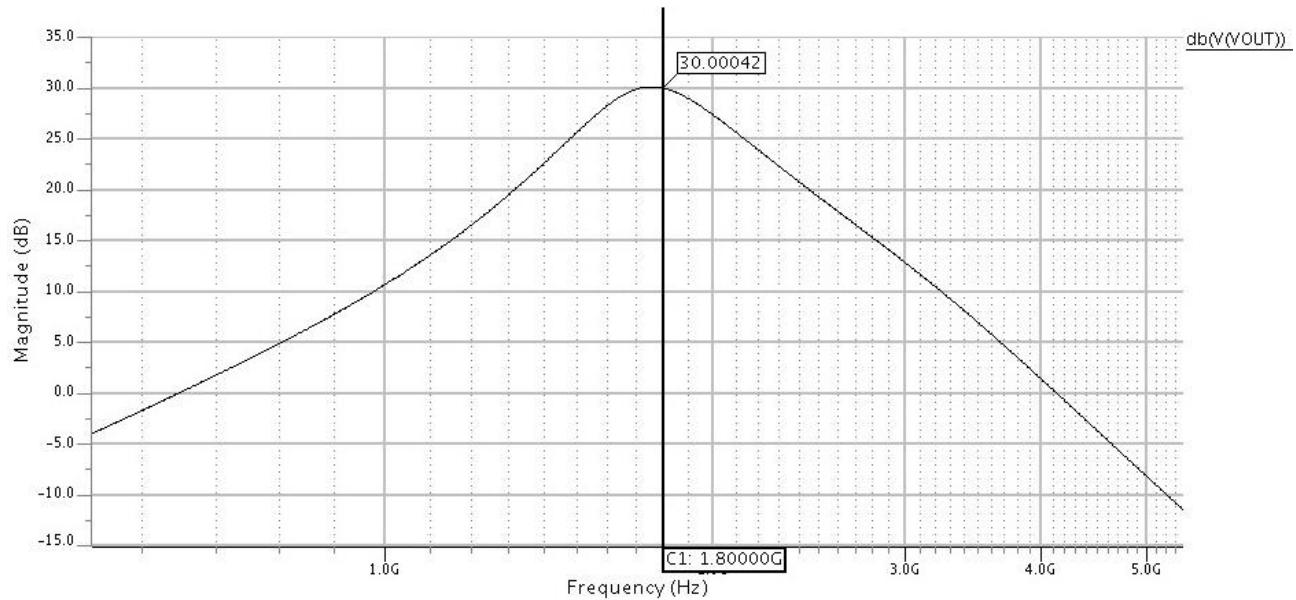

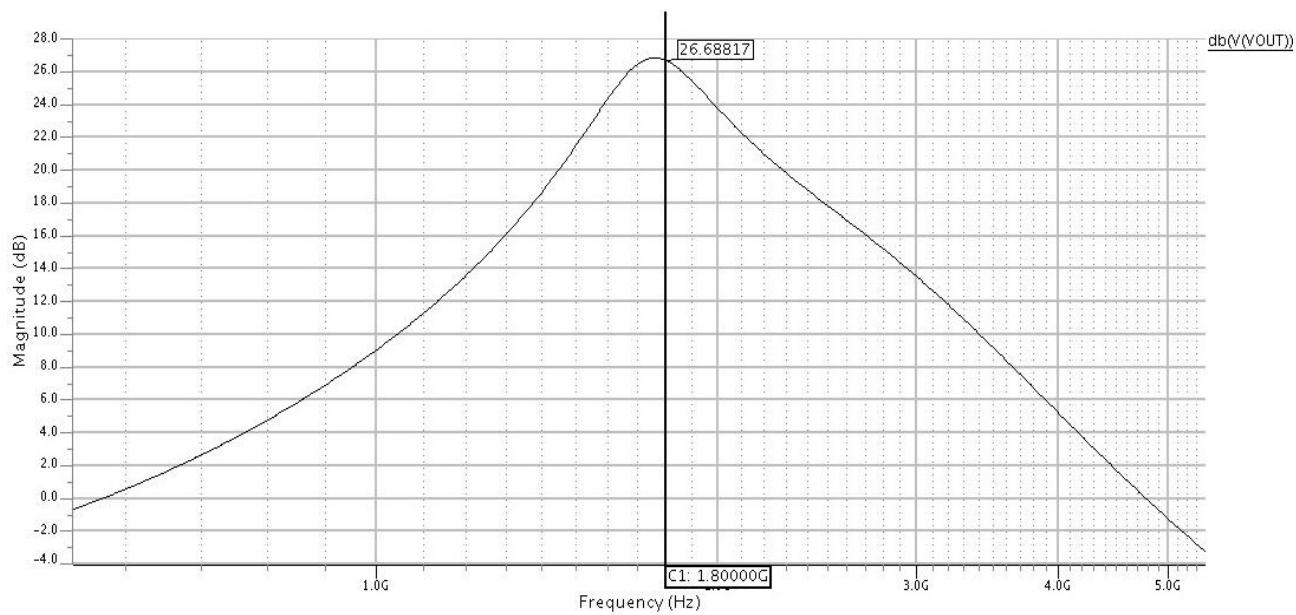

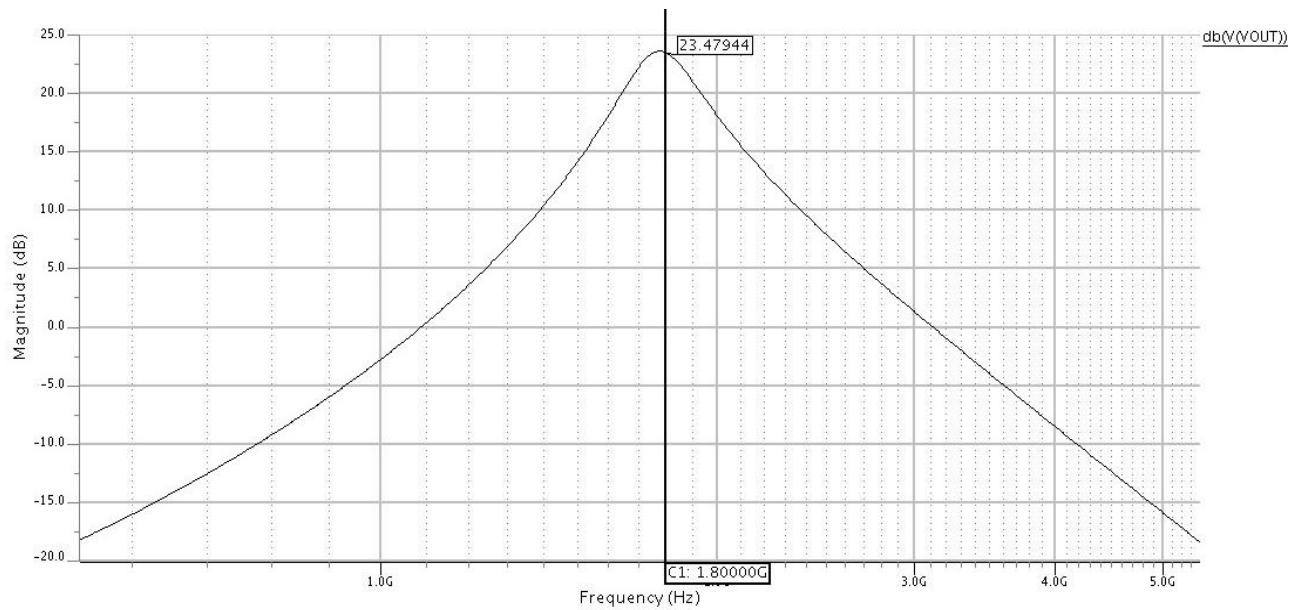

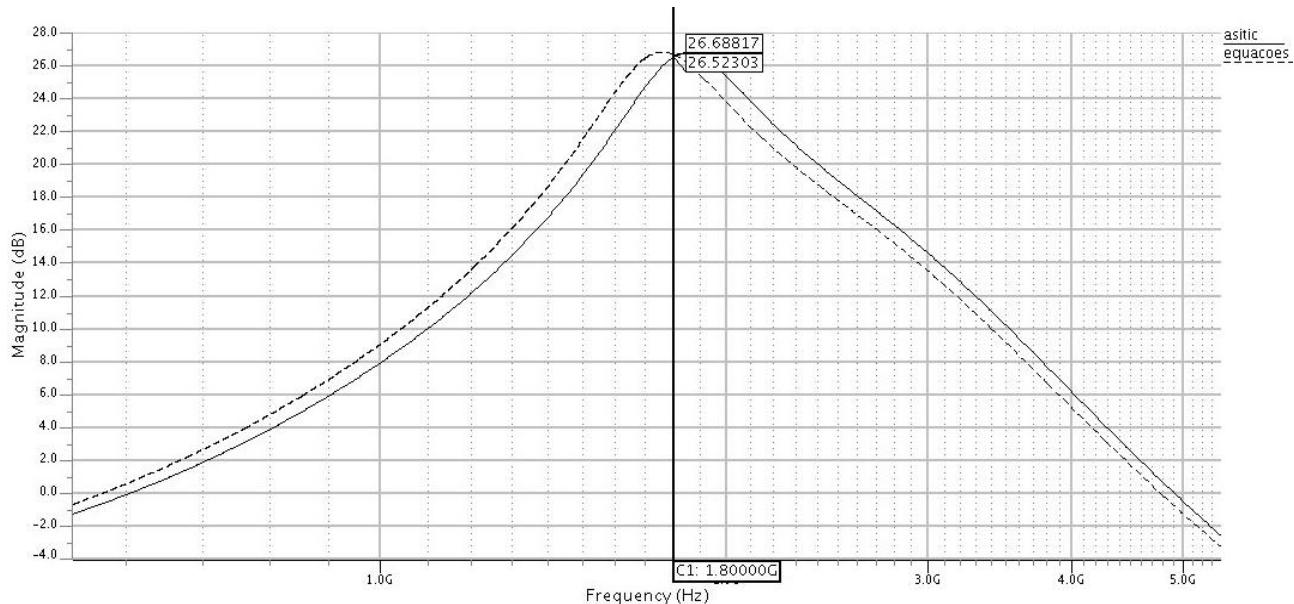

| Figura 45. Ganho de Tensão versus frequência de operação, topologia 1, Figura 39 (a), considerando modelo típico do transistor (modelo BSim3v3). .....                                                                                                                                                        | 74 |

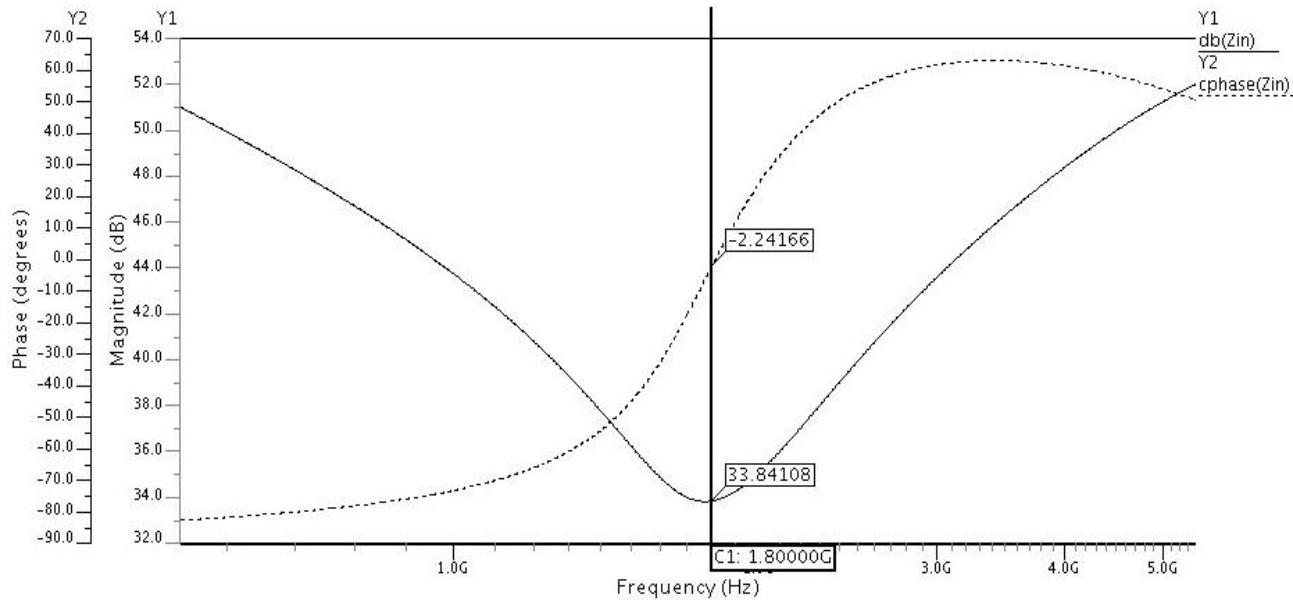

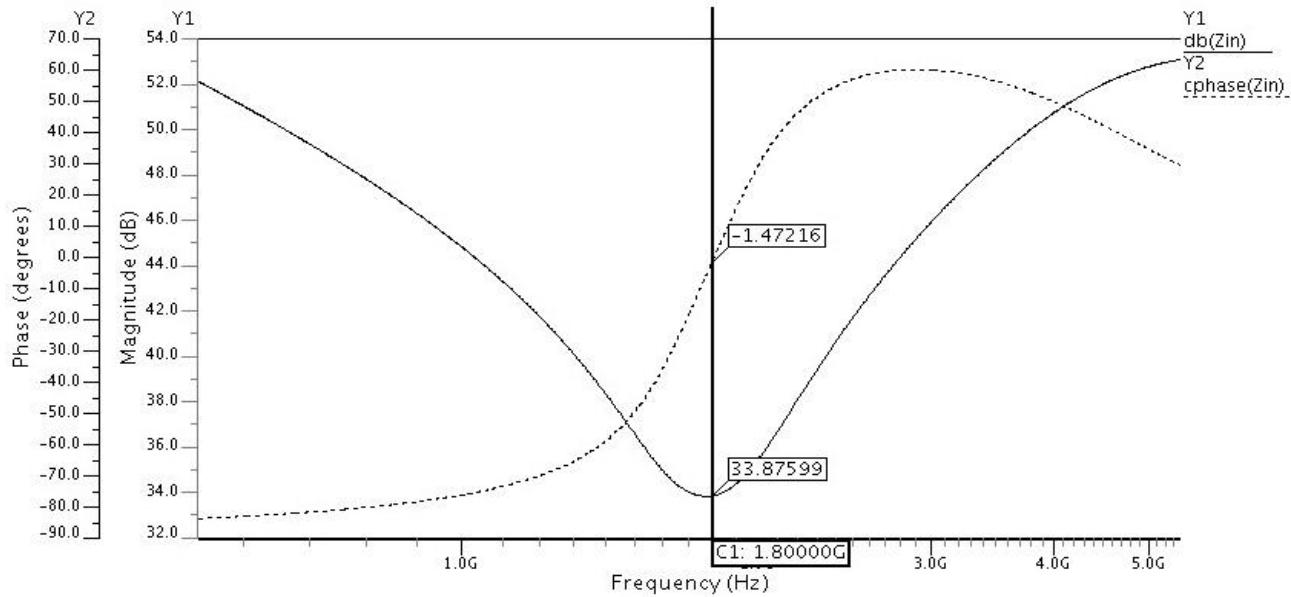

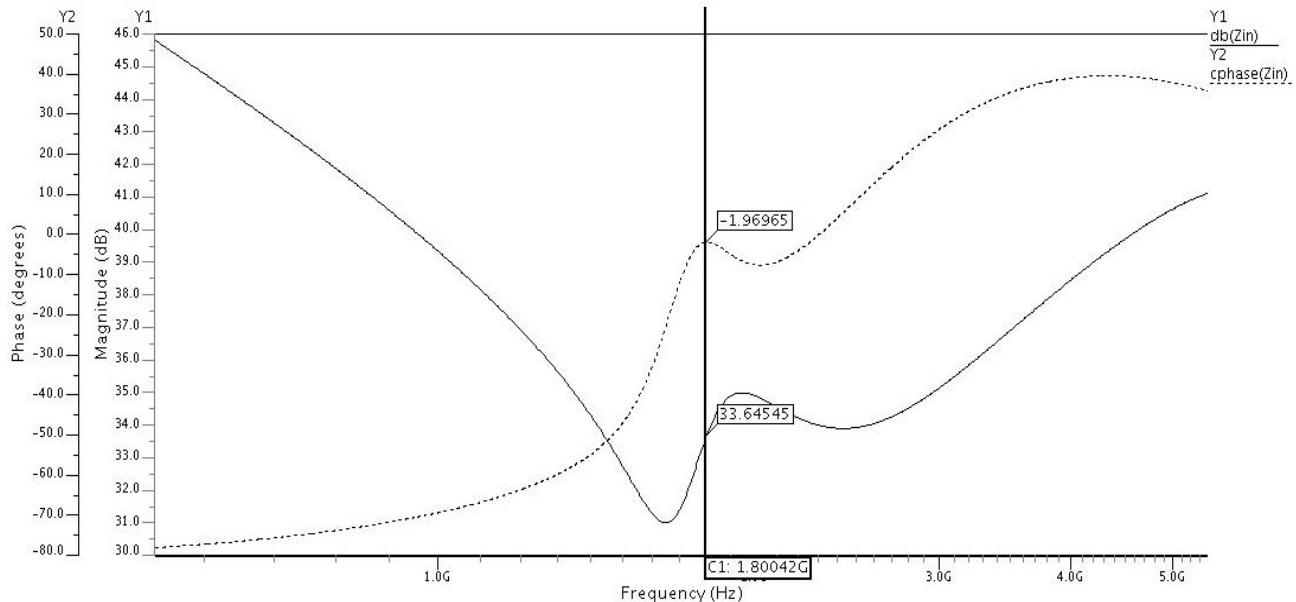

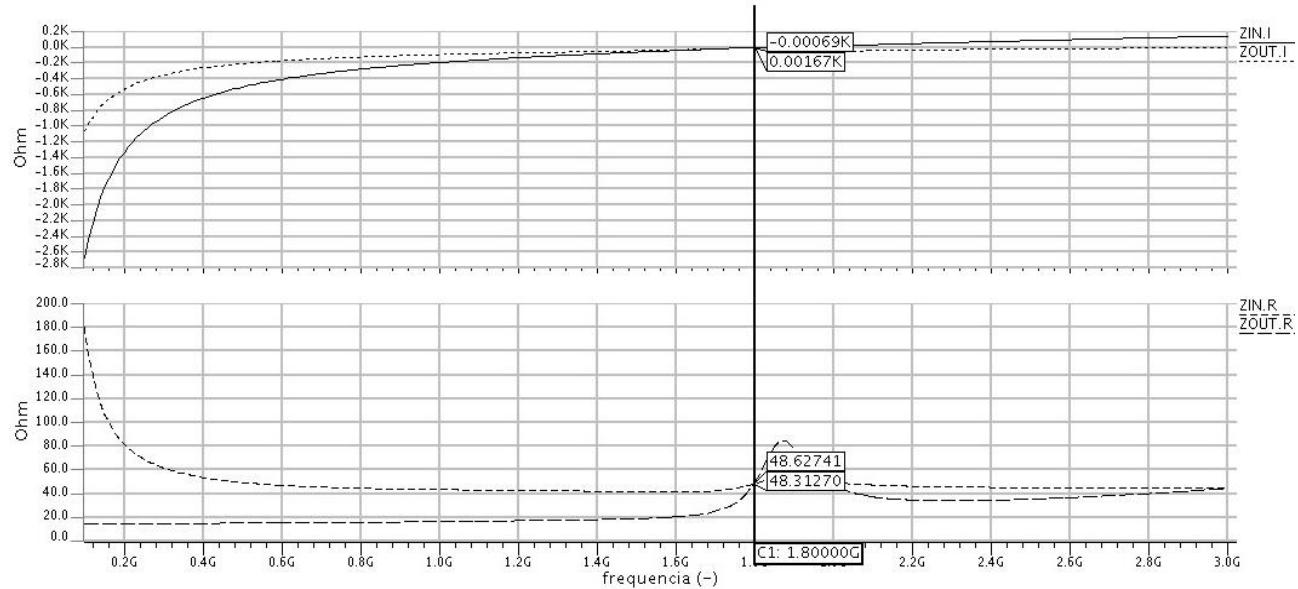

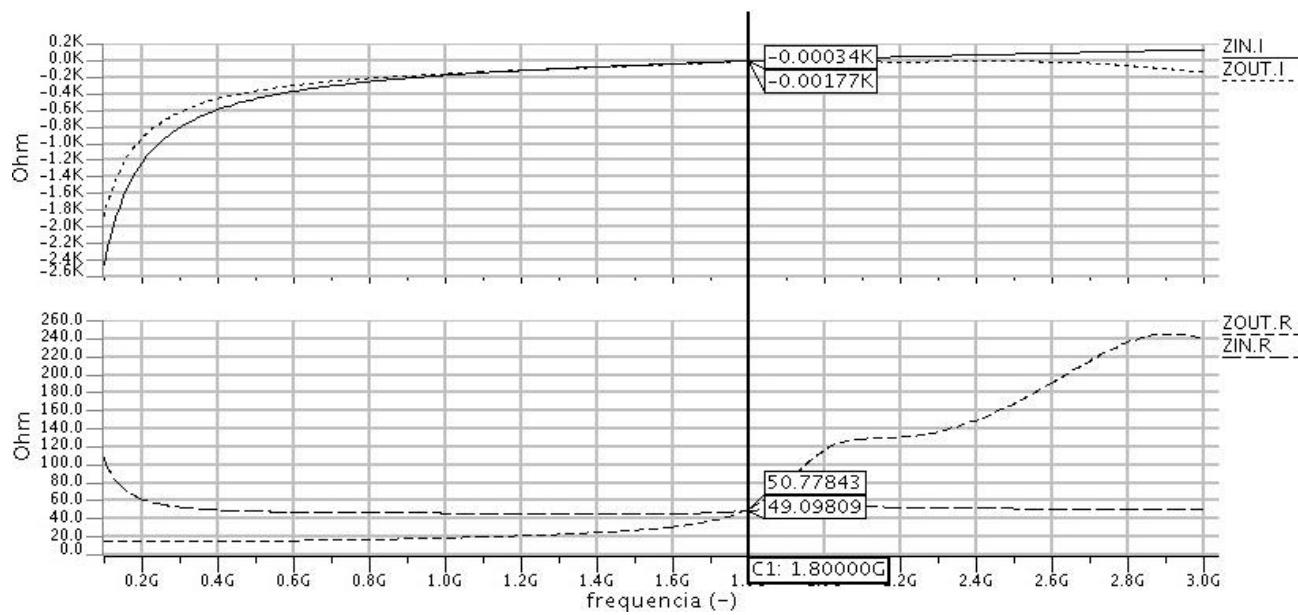

| Figura 46. Impedância de entrada, parte real e imaginária, versus frequência de operação, topologia 1, Figura 39 (a), considerando modelo típico do transistor (modelo BSim3v3).....                                                                                                                          | 74 |

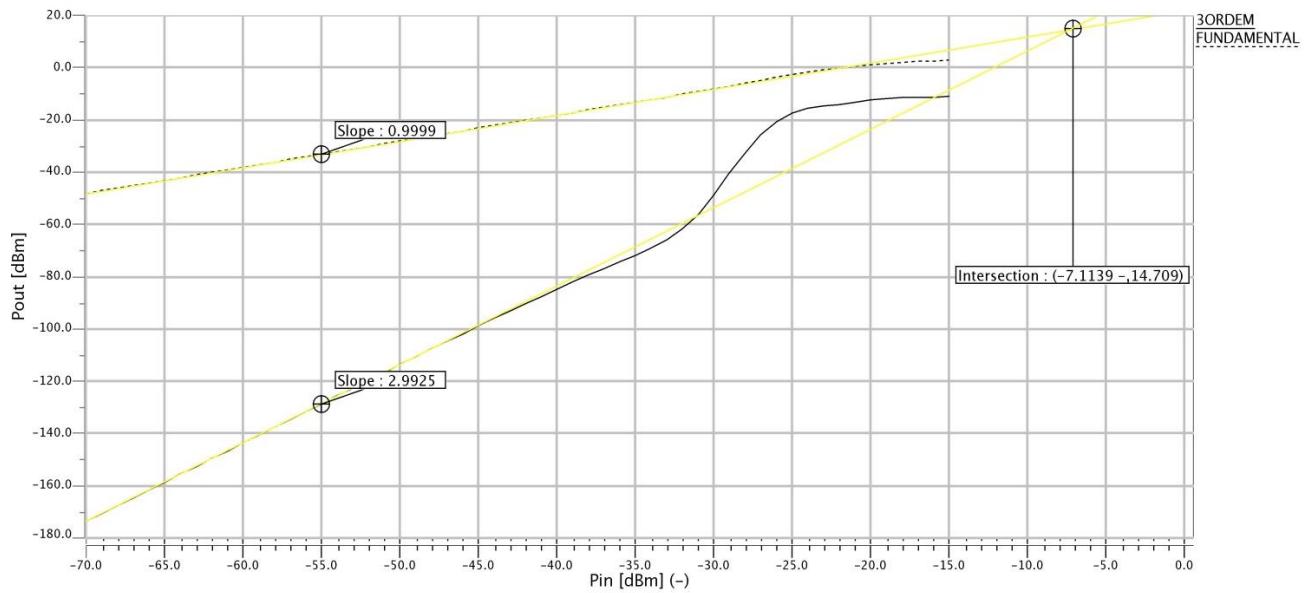

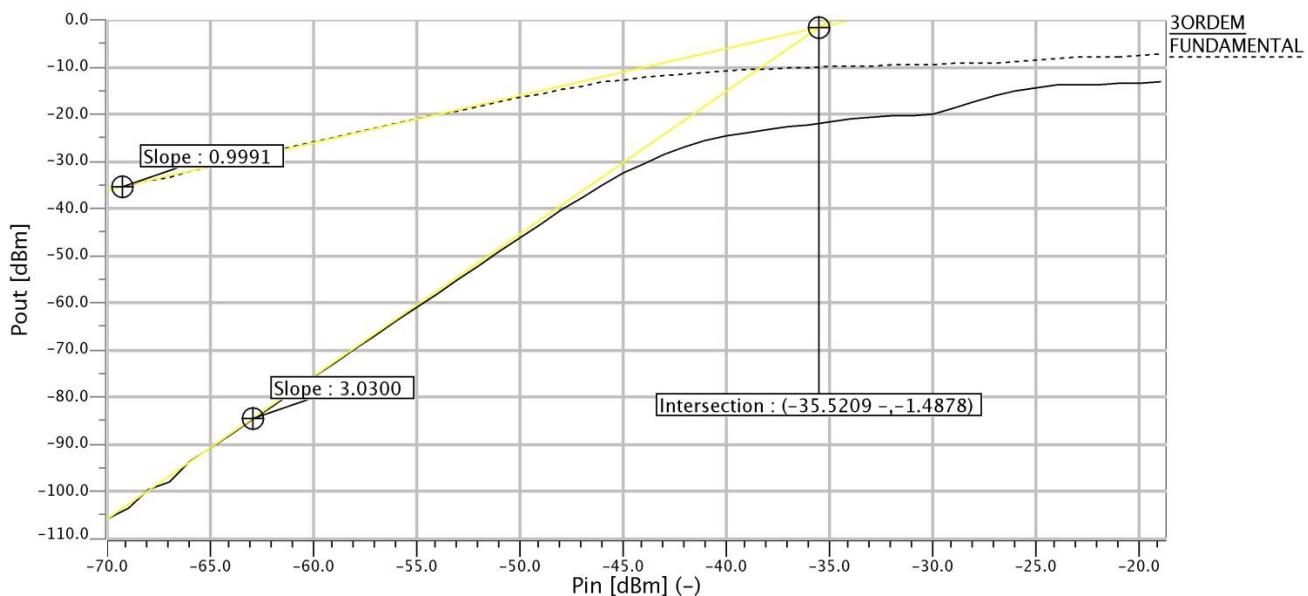

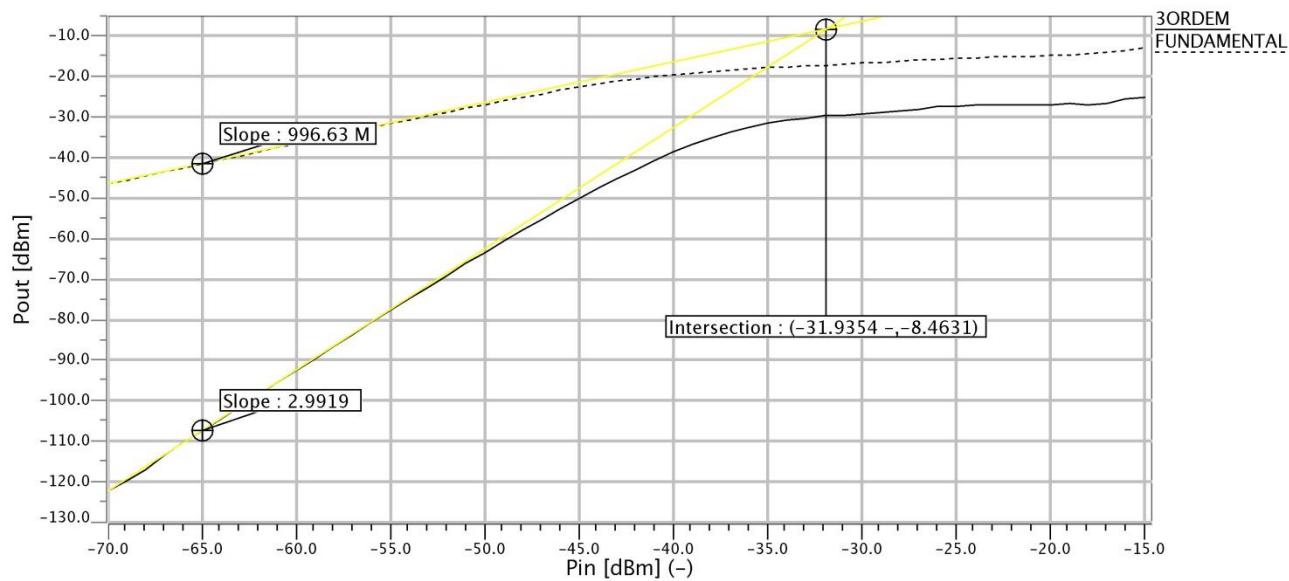

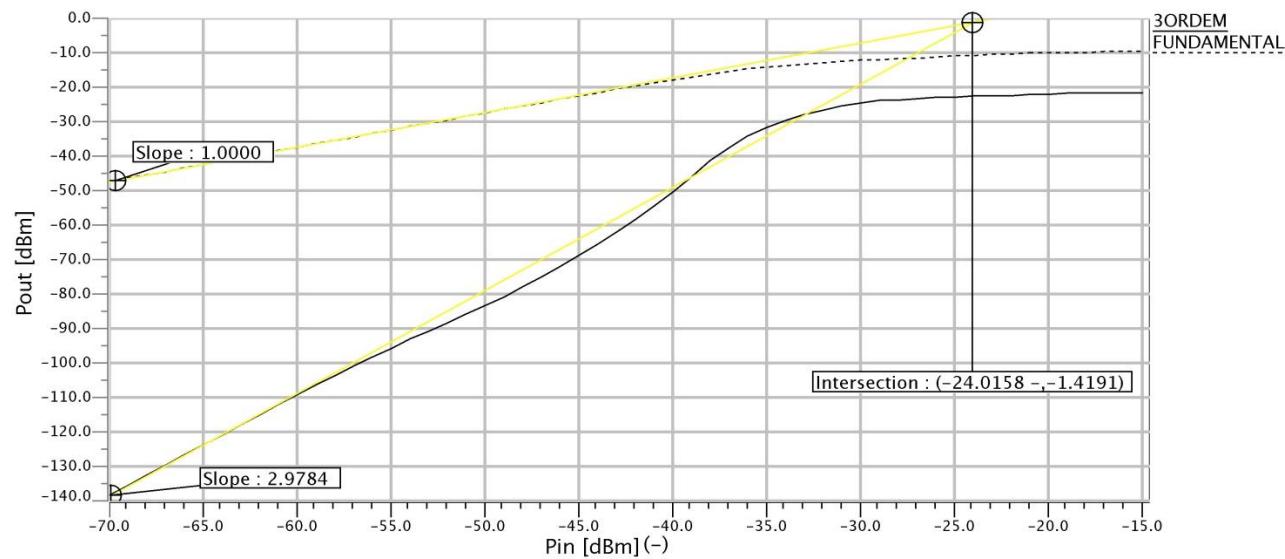

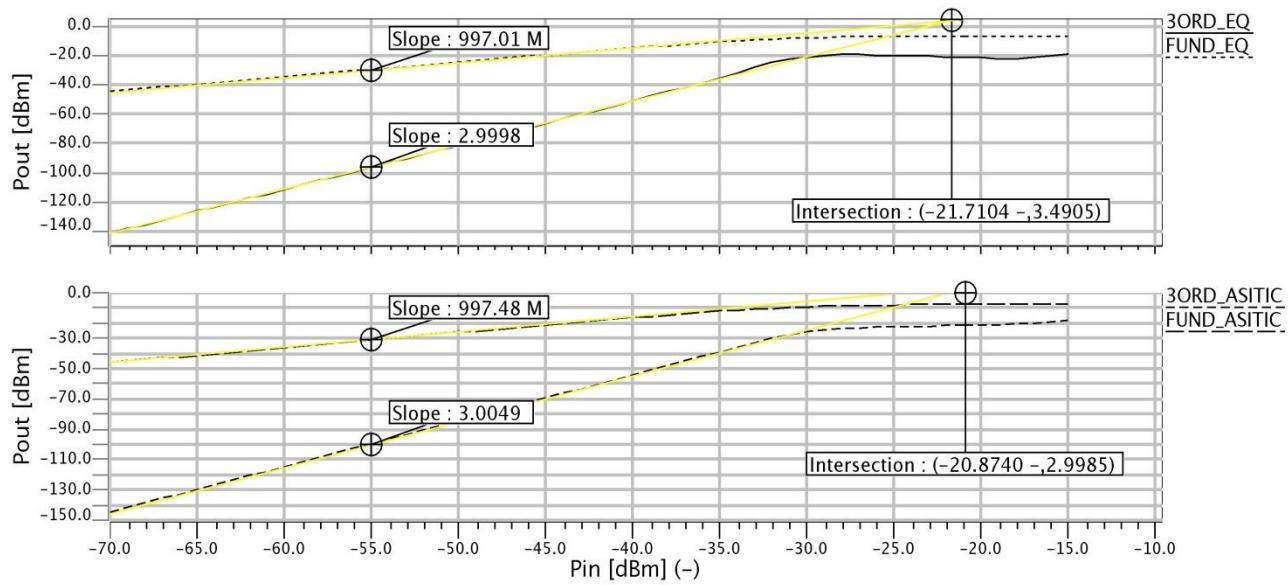

| Figura 47. Potências do sinal de saída, fundamental e produto de intermodulação de terceira ordem, em função da potência no sinal de entrada para os LNAs otimizados OIP3 da topologia 1, Figura 39 (a), considerando modelo típico do transistor (modelo BSim3v3).....                                       | 75 |

| Figura 48. Ganho de Tensão versus frequência de operação, topologia 2, Figura 39 (b), considerando modelo típico do transistor (modelo BSim3v3). .....                                                                                                                                                        | 75 |

| Figura 49. Impedância de entrada, parte real e imaginária, versus frequência de operação, topologia 2, Figura 39 (b), considerando modelo típico do transistor (modelo BSim3v3).....                                                                                                                          | 76 |

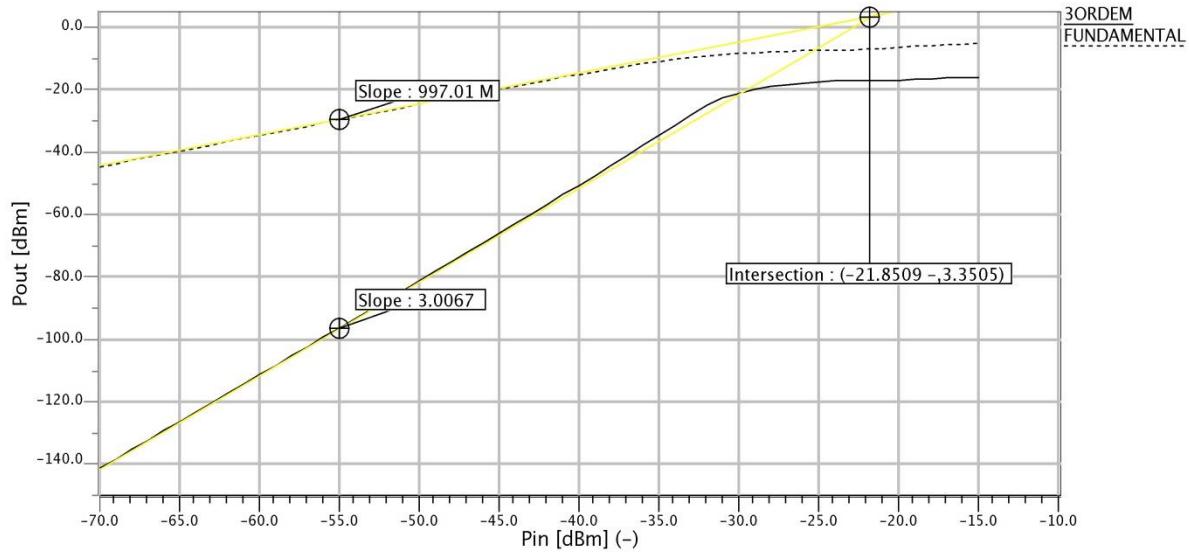

| Figura 50. Potências do sinal de saída, fundamental e produto de intermodulação de terceira ordem, em função da potência no sinal de entrada para os LNAs otimizados OIP3 da topologia 2, Figura 39 (b), considerando modelo típico do transistor (modelo BSim3v3).....                                       | 76 |

| Figura 51. Ganho de Tensão versus frequência de operação, topologia 3, Figura 39 (c), considerando modelo típico do transistor (modelo BSim3v3). .....                                                                                                                                                        | 77 |

| Figura 52. Impedância de entrada, parte real e imaginária, versus frequência de operação, topologia 3, Figura 39 (c), considerando modelo típico do transistor (modelo BSim3v3).....                                                                                                                          | 77 |

| Figura 53. Potências do sinal de saída, fundamental e produto de intermodulação de terceira ordem, em função da potência no sinal de entrada para os LNAs otimizados OIP3 da topologia 3, Figura 39 (c), considerando modelo típico do transistor (modelo BSim3v3).....                                       | 78 |

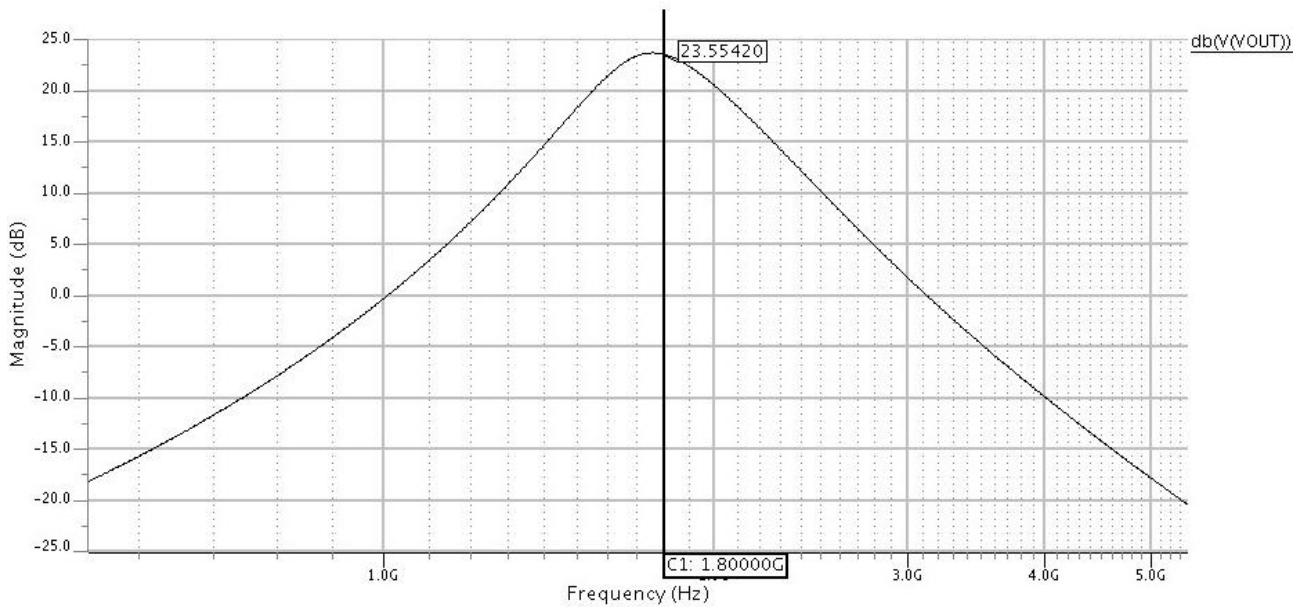

| Figura 54. Ganho de Tensão versus frequência de operação, topologia 2 com casamento de impedância na saída, Figura 39 (b), considerando modelo típico do transistor (modelo BSim3v3). .....                                                                                                                   | 80 |

|                                                                                                                                                                                                                                                                                                               |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figura 55. Impedância de entrada e saída, parte real e imaginária, versus frequência de operação, topologia 2, Figura 39 (b), considerando modelo típico do transistor (modelo BSim3v3) .....                                                                                                                 | 80 |

| Figura 56. Potências do sinal de saída, fundamental e produto de intermodulação de terceira ordem, em função da potência no sinal de entrada para os LNAs otimizados OIP3 da topologia 2 com casamento de impedância na saída, Figura 39 (b), considerando modelo típico do transistor (modelo BSim3v3) ..... | 81 |

| Figura 57. Ganho de Tensão versus frequência de operação, topologia 4 com casamento de impedância na saída, Figura 39 (d), considerando modelo típico do transistor (modelo BSim3v3) .....                                                                                                                    | 81 |

| Figura 58. Impedância de entrada e saída, parte real e imaginária, versus frequência de operação, topologia 4, Figura 39 (d), considerando modelo típico do transistor (modelo BSim3v3) .....                                                                                                                 | 82 |

| Figura 59. Potências do sinal de saída, fundamental e produto de intermodulação de terceira ordem, em função da potência no sinal de entrada para a topologia 4 com casamento de impedância na saída, Figura 39 (d), considerando modelo típico do transistor (modelo BSim3v3) .....                          | 82 |

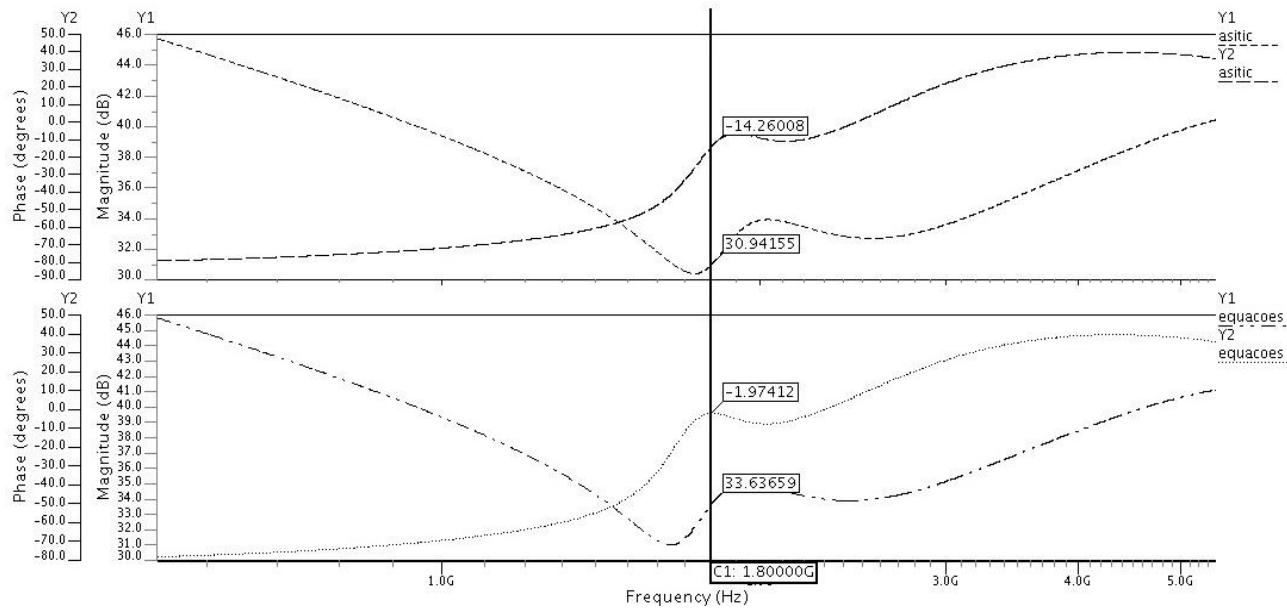

| Figura 60. Ganho de Tensão versus frequência de operação, com os indutores extraídos pelas equações e pelo ASITIC, da topologia 3, Figura 39(c), considerando modelo típico do transistor (modelo BSim3v3) .....                                                                                              | 84 |

| Figura 61. Impedância de entrada e saída, parte real e imaginária, versus frequência de operação, com os indutores extraídos pelas equações e pelo ASITIC, da topologia 3, Figura 39 (c), considerando modelo típico do transistor (modelo BSim3v3) .....                                                     | 85 |

| Figura 62. Potências do sinal de saída, fundamental e produto de intermodulação de terceira ordem, em função da potência no sinal de entrada, com os indutores extraídos pelas equações e pelo ASITIC, da topologia 3, Figura 39 (c), considerando modelo típico do transistor (modelo BSim3v3) .....         | 85 |

## **Lista de Tabelas**

|                                                                                                                                            |    |

|--------------------------------------------------------------------------------------------------------------------------------------------|----|

| Tabela 1. Especificação do projeto de LNA.....                                                                                             | 21 |

| Tabela 2. Correlação entre os estados do transistor MOS e a diferença de tensão entre seus terminais. $V_{GD}$ é a tensão porta-dreno..... | 25 |

| Tabela 3. Capacitâncias entre os terminais de um transistor NMOS e seus valores.....                                                       | 30 |

| Tabela 4. Parâmetros S e suas definições.....                                                                                              | 44 |

| Tabela 5. Resumo das características das configurações com degeneração indutiva.....                                                       | 47 |

| Tabela 6. Parâmetros a serem otimizadas na topologia 1, Figura 30 (a), e a faixa de valores analisada.....                                 | 63 |

| Tabela 7. Parâmetros a serem otimizadas na topologia 2, Figura 30 (b), e a faixa de valores analisada.....                                 | 63 |

| Tabela 8. Parâmetros a serem otimizadas na topologia 3, Figura 30 (c), e a faixa de valores analisada.....                                 | 64 |

| Tabela 9. Parâmetros a serem otimizadas na topologia 4, Figura 30 (d), e a faixa de valores analisada.....                                 | 64 |

| Tabela 10. Características fixas nas topologias usadas.....                                                                                | 65 |

| Tabela 11. Parâmetros do algoritmo SA utilizados pelo CirOp.....                                                                           | 65 |

| Tabela 12. Especificação do projeto de LNA.....                                                                                            | 71 |

| Tabela 13. Pesos da função objetivo sem considerar casamento de impedância na saída.....                                                   | 71 |

| Tabela 14. Pesos da função objetivo considerando o casamento de impedância na saída.....                                                   | 71 |

| Tabela 15. Dimensionamento obtido na topologia 1, Figura 30(a).....                                                                        | 72 |

| Tabela 16. Dimensionamento obtido na topologia 2, Figura 30 (b).....                                                                       | 72 |

| Tabela 17. Dimensionamento obtido na topologia 3, Figura 30 (c).....                                                                       | 73 |

| Tabela 18. Resultados obtidos para cada topologia, sem casamento de impedância na saída, para os parâmetros do projeto.....                | 73 |

| Tabela 19. Dimensionamento obtido na topologia 2, Figura 30 (b).....                                                                       | 78 |

| Tabela 20. Dimensionamento obtido na topologia 4, Figura 30 (d).....                                                                       | 79 |

| Tabela 21. Resultados obtidos para cada topologia considerada.....                                                                         | 79 |

| Tabela 22. Resultados obtidos com os LNAs e da literatura.....                                                                             | 83 |

|                                                                                                                                                              |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Tabela 23. Tempo de execução da otimização considerando o modelo extraído pelas equações e modelo extraído pelo ASITIC, considerando quatro otimizações..... | 83 |

| Tabela 24. Resultado das otimizações da topologia 2 usando a extração dos indutores através das equações e ASITIC.....                                       | 84 |

| Tabela 25. Resultados obtidos para a topologia 1 para o LNA2 do trabalho [47].....                                                                           | 86 |

| Tabela 26. Dimensões dos indutores obtidas para a topologia 1 e para o LNA2 do trabalho [47].....                                                            | 86 |

## Capítulo 1 - Introdução

A necessidade de aperfeiçoar os meios de comunicação está enraizada na cultura humana e sempre que houve avanços na sociedade também houve avanços nas tecnologias de comunicação. Esses avanços são notórios nos últimos dois séculos quando surgiram diversos novos sistemas para a comunicação como o telefone, o rádio, a televisão, a Internet e a transmissão de dados via satélite. Esses mecanismos têm sido intensamente melhorados, o que só foi possível graças ao surgimento e avanço da microeletrônica, que possibilitou o desenvolvimento de circuitos integrados complexos com dimensões, consumo e custos reduzidos. Circuitos integrados, CI's ou *chips*, são circuitos completos feitos sobre um mesmo material semicondutor.

O progresso em microeletrônica permitiu que CI's se tornassem parte essencial de diversos equipamentos de comunicação (satélites, smartphones, roteadores, computadores). Entretanto, os avanços obtidos nestes equipamentos não foram suficientes, fazendo com que o Homem ainda continue procurando aperfeiçoar os equipamentos de comunicação.

Uma área de grande interesse, para a melhoria dos equipamentos de comunicação, é a dos circuitos integrados para radiofrequência (RF). Estes circuitos vêm permitindo o desenvolvimento de dispositivos portáteis menores, com menor consumo de potência e mais baratos.

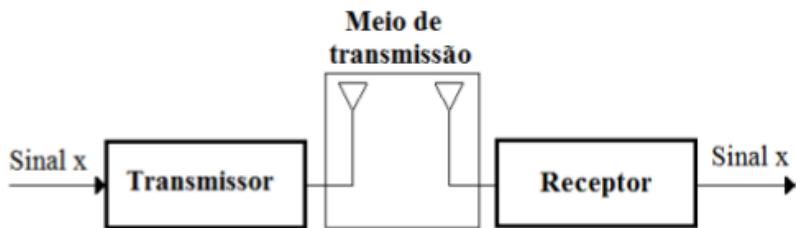

Blocos genéricos para comunicação RF são o transmissor e o receptor, apresentados na Figura 1.

Figura 1. Blocos básicos de um sistema RF.

O transmissor e o receptor podem ser descritos em mais detalhes por um conjunto de outros blocos como apresentado na Figura 2. No transmissor o sinal é digitalizado, se originalmente for analógico, comprimido, codificado, modulado, amplificado e, então, transmitido. Os blocos de um transmissor são:

Figura 2. Bloco transmissor e receptor, em destaque o LNA.

- **Conversor DAC (Digital Analog Converter):** Converte sinais analógicos em sinais digitais;

- **Compressor:** Responsável por remover redundâncias do sinal, ou seja, comprimí-lo a fim de conseguir transmitir a mesma quantidade de informação usando uma menor largura de banda. Essa compressão pode ser realizada através dos algoritmos de *mpeg* para vídeos e MP3 para a transmissão de áudio, por exemplo;

- **Codificador:** Realiza a codificação do sinal digital gerado, através da representação do sinal em pulsos elétricos, como por exemplo, a codificação delta;

- **Modulador:** Circuito responsável pela modulação, processo no qual uma onda portadora é modificada, em amplitude, frequência ou fase, pelo sinal de informação.

- **Amplificador:** Responsável por amplificar o sinal antes de ele ser transmitido.

O receptor, por sua vez, recebe um sinal modulado com ruído e faz o processo inverso do realizado no transmissor, ou seja, amplifica o sinal recebido, demodula-o, decodifica-o, descomprime-o e, por fim, converte novamente em analógico se preciso.

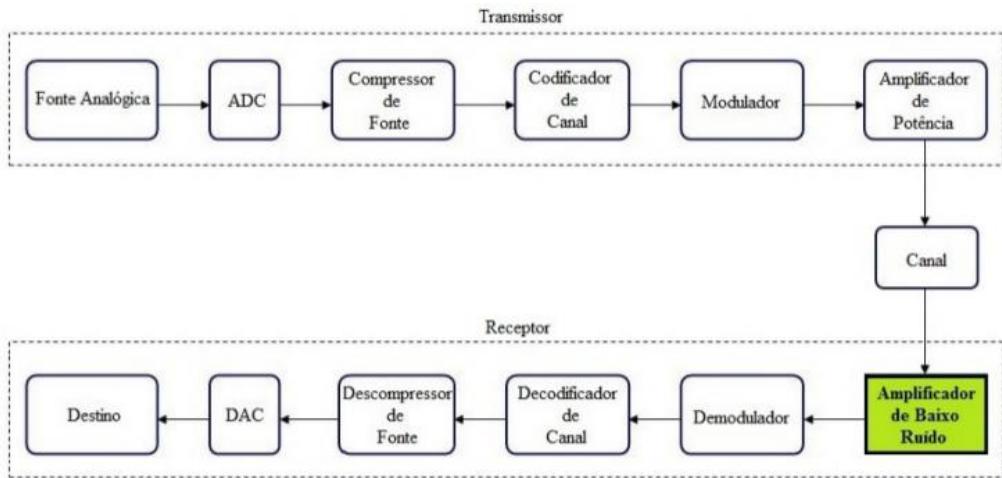

Um dispositivo transceptor (dispositivo transmissor e receptor), com seus principais circuitos analógicos, é detalhado na Figura 3. O receptor é composto dos seguintes circuitos:

Figura 3. Representação de um circuito transceptor RF completo.

- **LNA (Low Noise Amplifier):** Circuito responsável por amplificar o sinal recebido minimizando a introdução de ruídos ao sinal;

- **Mixer:** circuito que cria uma nova frequência de operação através de operações com os sinais de entrada, sinal de entrada mais sinal do oscilador;

- **Filtro:** Na filtragem é feito a seleção do canal desejado dentro da banda de recepção;

- **Amplificador:** Amplifica os sinais para que facilite suas operações nas etapas subsequentes;

- **Demodulador:** Essa etapa é responsável por obter os dados codificados enviados originalmente.

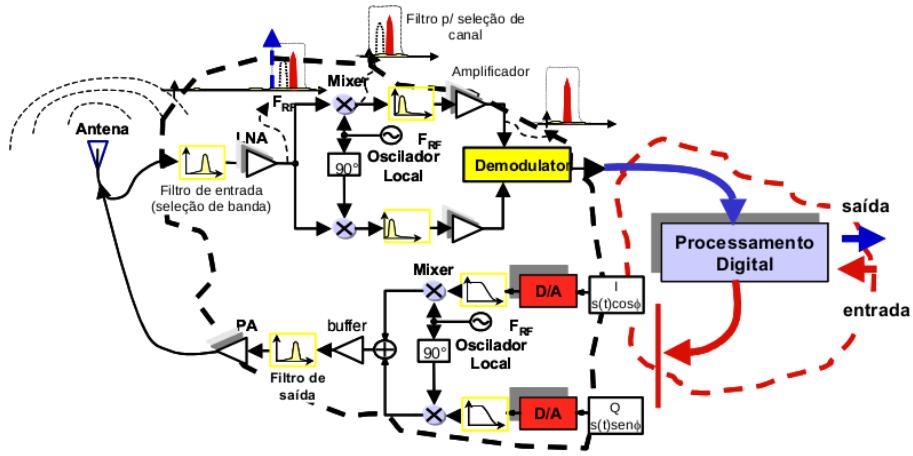

Podemos prosseguir o detalhamento do sistema de comunicação, apresentando outros subníveis, porém focaremos agora no LNA que é o objeto deste trabalho. A função de um LNA é de amplificar sinais de baixa potência (ordem de microvolts), garantindo a menor inserção de ruído possível e sem distorcer significativamente o sinal a amplificar [1] [2]. Na Figura 4 é apresentada uma topologia de LNA MOS (Metal Oxide Semiconductor).

Figura 4. Esquemático de um LNA.

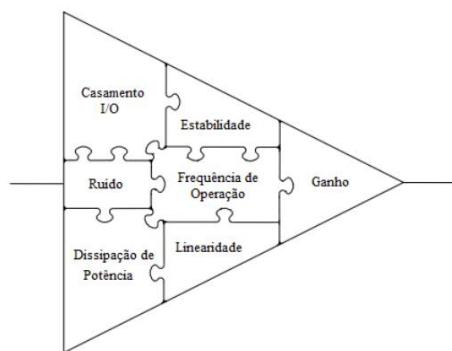

O projeto de um LNA exige a atenção a diversos requisitos além da baixa inserção de ruído e da amplificação do sinal de entrada. Entre esses requerimentos, podemos citar: consumo de potência, frequência de operação, casamento da impedância na entrada, baixa distorção harmônica, estabilidade e, em alguns casos, casamento da impedância na saída. Na Figura 5 [3] são ilustradas os principais requerimentos no projeto de um LNA.

Existe entre esses requerimentos uma grande interdependência, sendo uma das mais importantes a relação entre consumo de potência e a degradação do ruído [1] [2]. Essa interdependência torna o projeto de um LNA um grande problema. Alguns autores, tais como [4] [2] [1] [5], propõem contornar o problema de projetos de LNAs através da otimização da figura de ruído para duas restrições simultâneas: casamento da impedância de entrada e ganho, ou casamento da impedância de entrada e consumo de potência. ROA, [3], por sua vez, propõe um método de projeto que otimiza o desempenho de ruído e linearidade para consumo de potência e ganho de potência especificados. O autor de [6] propõe um método baseado em transistores operando na inversão moderada para alcançar um ótimo desempenho no quesito de figura de ruído.

Figura 5. Parâmetros do projeto de LNA.

Os métodos apresentados acima, contudo, não dão muita atenção a um dos principais elementos para o sucesso de um LNA, o indutor. Os indutores em um LNA são responsáveis pelo casamento de impedâncias, carga de saída e filtragem. Uma modelagem incorreta dos indutores leva a um péssimo projeto de LNA, pois podem resultar em mau casamento de impedância, ganhos diferentes do esperado, filtros não centrados na frequência de operação e em aumento no ruído de saída.

O presente trabalho tem como objetivo contornar as dificuldades encontradas nos projetos de LNAs através do uso de algoritmos meta-heurísticos de otimização. Algoritmos meta-heurísticos são métodos estocásticos de otimização. O comportamento desses algoritmos é guiado por uma função objetivo que calcula a nota para as soluções temporárias encontradas. No presente trabalho esse cálculo foi realizado através de simulações elétricas dos circuitos projetados, se diferenciando de trabalhos que utilizam funções objetivo baseadas em equações aproximadas das características do circuito. Além disso, será analisada a viabilidade do uso de equações que, a partir de características físicas, determinam o modelo elétrico de indutores integrados. Para atingir nossos objetivos serão projetados amplificadores de baixo ruído, a partir de um conjunto inicial de requisitos.

Na Tabela 1 estão contidas as especificações desejadas para um LNA, estabelecidas no começo do projeto. Os valores foram escolhidos como uma média do estado da arte. Para a frequência de operação se pensou em LNAs para aplicações que trabalham em faixas próximas da frequência de 1,8 GHz, como por exemplo, etiquetas de RF-ID (*Radio-Frequency Identification*) para rastrear animais.

*Tabela 1. Especificação do projeto de LNA.*

| Especificações                     |       |

|------------------------------------|-------|

| <b>Figura de Ruído [dB]</b>        | < 3,2 |

| <b>Ganho [dB]</b>                  | > 15  |

| <b>Consumo de Potência [mW]</b>    | < 10  |

| <b>Impedância de Entrada [Ohm]</b> | 50    |

| <b>Impedância de Saída [Ohm]</b>   | 50    |

| <b>OIP3* [dBm]</b>                 | < -10 |

| <b>Frequência [GHz]</b>            | 1,8   |

\* potência de interseção da terceira harmônica, considerada na saída.

A motivação para o presente estudo é a grande e crescente quantidade de aplicações/tecnologias que utilizam comunicações RF e, portanto, LNAs [2]:

- **WLAN's (Wireless Local Area Network):** As redes locais sem fio são aplicações para prover comunicação móvel em escritórios, hospitais, fábricas, etc. Operam na banda de 900 MHz até 2,4 GHz. Portabilidade e reconfiguração são características das WLAN's;

- **GPS (Global Position System):** O sistema de posicionamento global é um sistema de navegação por satélite que fornece a um aparelho receptor móvel a sua posição a qualquer momento. O GPS é uma aplicação útil para trabalhos de exploração em terra ou nos oceanos e para traçar percursos e rotas para veículos terrestres, de voo e navegação. A faixa de operação do GPS é de 1,17 GHz até 1,57 GHz;

- **RF-ID' (Radio-Frequency Identification):** Sistemas de identificação por radiofrequência são aplicações para identificação automática através de sinais de rádio, recuperando e armazenando dados por meio de etiquetas RFID. Uma etiqueta RFID é um dispositivo transceptor que pode ser colocada em objetos, animais ou pessoas. Estes dispositivos operam na faixa de 900 MHz até 2,4 GHz;

- **GSM (Global System for Mobile Communications):** Sistema Global para Comunicações Móveis é o padrão mais popular para telefones celulares do mundo. Permite, além da comunicação de voz, a troca de dados entre telefones, acesso a internet e serviço de *roaming* internacional. Para as tecnologias 2G, a frequência de operação é entre 0,9 a 1,8 GHz e para as tecnologias 3G a frequência de operação é de 2,1 GHz;

- **Bluetooth:** Esta aplicação permite comunicação rápida, segura e barata entre computadores, *smartphones*, telefones celulares, *mouses*, teclados, impressoras e outros dispositivos, utilizando ondas de rádio no lugar de cabos. É um padrão de comunicação de baixo consumo de energia. O alcance depende da potência de transmissão, podendo ser de 1,0 metro (Classe 3), 10 metros (Classe 2) ou até 100 metros (Classe 1). O Bluetooth opera na faixa de 2,4 até 2,5 GHz.

Este trabalho foi desenvolvido na tecnologia AMS (Austria Micro Systems) CMOS (*Complementary Metal Oxide Silicon*) 0,35  $\mu\text{m}$  [7], com o auxílio da ferramenta de simulação de circuitos elétricos ELDO da Mentor Graphics (ELDO 13.2 64 bits) e da ferramenta MATLAB (versão 8.10.604 R2013a), onde os algoritmos meta-heurísticos foram implementados.

O presente texto está organizado da seguinte forma: no capítulo dois trata-se dos aspectos teóricos da figura de ruído, dos transistores MOS, dos indutores integrados, do projeto de LNAs e de algoritmos meta-heurísticos; no capítulo três é apresentado o método utilizado para a realização do trabalho; no capítulo 4 são apresentados os resultados obtidos e os mesmos são discutidos; e, por fim, no capítulo 5 são apresentadas as conclusões do trabalho.

## Capítulo 2 – Revisão Teórica

### Fator/Figura de ruído

O fator de ruído é a medida da degradação na relação sinal-ruído - SNR (*Signal to Noise Ratio*) – causado por um componente em RF[8]. O SNR é definido como a relação entre a potência do sinal e a potência de ruído. Para um bloco que tem na sua entrada uma relação sinal ruído  $SNR_{in}$  e na sua saída a relação sinal ruído  $SNR_{out}$ , define-se fator de ruído  $F$  como:

$$F = \frac{SNR_{in}}{SNR_{out}}$$

O ideal seria que o  $SNR_{out}$  fosse igual ao  $SNR_{in}$ , mas circuitos reais sempre introduzem novos ruídos ao sinal.

A figura de ruído, NF (*Noise Figure*), é a transformação à escala logarítmica do fator de ruído:

$$NF = 10\log_{10}(F)$$

Neste trabalho será empregado o conceito de figura de ruído, ou seja, as medições de ruído são transformadas na escala logarítmica.

### Transistores MOS

Existem dois tipos de transistores MOS: o NMOS, onde a condução é realizada por elétrons, e o PMOS, onde a condução é realizada por lacunas. A tecnologia CMOS, que permite a fabricação de circuitos integrados com transistores tanto NMOS como PMOS, se tornou a principal tecnologia de fabricação de circuitos integrados, pois oferece, entre outras vantagens, altos níveis de integração, baixo consumo de potência e simplicidade de projeto. Nos últimos anos, 75% dos circuitos semicondutores (tanto em quantidade como em valor) foram produzidos em CMOS, fato que adiciona outra vantagem à tecnologia CMOS: a redução de custos devido à escala de produção. Este quadro não deve ser ainda alterado nos próximos anos [9].

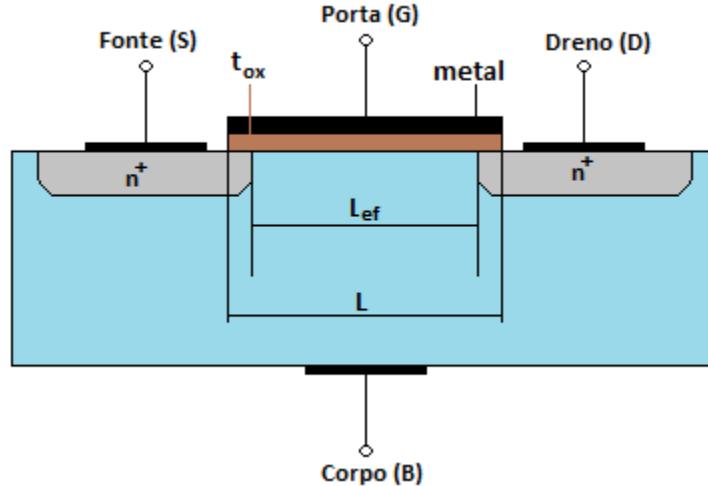

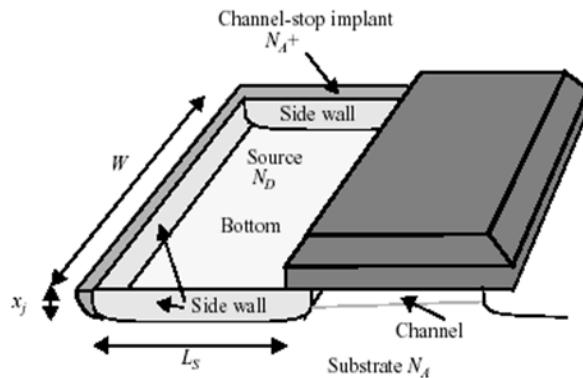

Na Figura 6 é apresentada a estrutura simplificada de um transistor NMOS. Esse tipo de transistor é fabricado sobre um substrato (corpo ou *bulk*) de silício tipo P (silício onde a condução é feita predominantemente por lacunas). O dispositivo consiste de duas regiões fortemente dopadas tipo N (silício onde a condução é feita predominantemente por elétrons) formando o dreno (D) e a fonte (S), de uma região condutora, metal ou silício

policristalino fortemente dopado, formando a porta (G) e de uma delgada camada de isolante, geralmente óxido de silício, que isola a região condutora do substrato P [10].

Figura 6. Estrutura física de um transistor NMOS.

Por construção do transistor MOS, normalmente dreno e fonte são iguais, entretanto, por convenção e para as relações elétricas, considera-se a fonte como a região no menor potencial. O comprimento de canal é a distância entre as áreas de dreno e fonte. Na Figura 6 nota-se que além de  $L$ , comprimento de máscara, está indicado o  $L_{ef}$ , comprimento do canal efetivo. O  $L$  é o comprimento desenhado no *layout*, enquanto  $L_{ef}$ , que surge devido às difusões do dreno e da fonte, fazendo com que essas áreas avancem sobre a região coberta pela porta, é o comprimento de fato do dispositivo. A tecnologia de fabricação utilizada nesse trabalho permite a construção de transistores com  $L$  de tamanho tão pequeno quanto 0,35  $\mu\text{m}$ .

O transistor MOS, quando conduzindo, pode trabalhar em três regiões distintas, classificadas pela densidade de portadores no canal, e que são:

- **Forte Inversão:** a tensão  $V_{GS}$ , entre porta e fonte, é suficiente para formar um canal com concentração de portadores igual ou superior à concentração de portadores intrínseca do substrato. Observemos que o tipo de portador no canal é diferente do portador intrínseco do substrato. É esta a região de operação estudada normalmente;

- **Fraca Inversão:** a tensão  $V_{GS}$  está próxima à tensão de *threshold*, ou de tensão de limiar de condução ( $V_{TH}$ ), do transistor, formando um canal com concentração de portadores inferior a concentração intrínseca de portadores do substrato. Utilizada para circuitos de baixíssimo consumo de potência;

- **Inversão Moderada:** é uma região de transição, não muito bem definida, entre as regiões de inversão forte e inversão fraca. Equações que descrevem o transistor nesta faixa não são muito precisas.

No presente trabalho, devido à faixa de frequências de operação dos LNAs, consideramos somente o transistor em forte inversão. Neste caso o transistor poderá operar em dois estados, tríodo e saturado, ou estar cortado. Essas regiões e o corte podem ser caracterizados pela diferença de tensão entre os terminais do transistor. Na Tabela 2 são apresentadas as tensões necessárias para que o transistor opere em cada uma dessas regiões ou no corte.

*Tabela 2. Correlação entre os estados do transistor MOS e a diferença de tensão entre seus terminais.  $V_{GD}$  é a tensão porta-dreno.*

| Estado          | Fonte             | Dreno             |

|-----------------|-------------------|-------------------|

| <b>Corte</b>    | $V_{GS} < V_{TH}$ | $V_{GD} < V_{TH}$ |

| <b>Saturado</b> | $V_{GS} > V_{TH}$ | $V_{GD} < V_{TH}$ |

| <b>Tríodo</b>   | $V_{GS} > V_{TH}$ | $V_{GD} > V_{TH}$ |

Em circuitos integrados analógicos, os transistores normalmente operam em saturação. Neste trabalho, portanto, consideram-se os transistores em forte inversão e saturados. Na saturação a corrente de dreno se torna praticamente constante, sendo dada por:

$$I_D = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TH})^2$$

onde  $W$  é a largura do canal do transistor,  $\mu_n$  é a mobilidade dos elétrons para os transistores NMOS,  $C_{ox}$  é a capacitância por unidade de área associada à porta e é igual a  $C_{ox} = \frac{k_{ox} \epsilon_0}{t_{ox}}$ ,  $k_{ox}$  é a constante dielétrica do isolante (aproximadamente 3,9 para óxido de silício),  $\epsilon_0$  é a permeabilidade no vácuo ( $8,85 \times 10^{-12}$  F/m) e  $t_{ox}$  a espessura do isolante.

O transistor da tecnologia utilizada neste trabalho tem uma espessura de isolante, óxido de silício, de 7,57 nm e, portanto, o  $C_{ox}$  é aproximadamente  $4,56 \text{ fF}/\mu\text{m}^2$ . Na equação de corrente com transistor em saturação, o projetista tem controle das dimensões do dispositivo e da tensão  $V_{GS}$ . Assim para uma relação  $(W/L)$  fixa, se variarmos a tensão  $V_{GS}$ , obtém-se diferentes respostas de corrente de dreno.

A equação de corrente em saturação também mostra que, quando dobrarmos  $W$  e  $L$ , a corrente não se altera, pois a relação  $(W/L)$  se mantém. As capacitâncias associadas às dimensões do dispositivo, por outro lado, aumentam e alteram-se as respostas para sinais rápidos.

Na equação da corrente há termos que o projetista não tem controle, como a tensão limiar  $V_{TH}$ ,  $C_{ox}$  e a mobilidade  $\mu_o$ , pois são parâmetros que dependem da tecnologia.

## Efeito de Corpo

O efeito de corpo ocorre quando há a diferença de potencial entre fonte-corpo,  $V_{SB}$ . Essa diferença de potencial faz com que a tensão de limiar do dispositivo,  $V_{TH}$ , aumente à medida que a fonte se torna mais positiva em relação ao corpo, dificultando a formação de um canal de condução. A equação abaixo mostra como  $V_{TH}$  se comporta [11]:

$$V_{TH} = V_{TH_0} + \gamma(\sqrt{|2\phi_F + V_{SB}|} - \sqrt{|2\phi_F|})$$

onde  $V_{TH_0}$  é a tensão de limiar quando  $V_{SB} = 0$ ,  $\gamma$  é o coeficiente de efeito de corpo, *bulk*, e  $\phi_F$  é o potencial de junção.  $\gamma$  e  $\phi_F$  são parâmetros que dependem da tecnologia e, portanto, estão fora do controle do projetista.

## Modulação de Canal

Quando o transistor está em saturação, o aumento da tensão entre dreno e fonte causa um aumento da corrente no dreno. Esse efeito é conhecido como modulação de canal e ocorre pela diminuição do comprimento efetivo do canal  $L_{ef}$  do transistor. A modulação de canal é modelada através de uma correção na formula da corrente em saturação, onde a nova equação é:

$$I_D = \frac{1}{2} \mu_o C_{ox} \frac{W}{L} (V_{GS} - V_{TH})^2 (1 + \lambda V_{DS})$$

onde  $\lambda$  é o coeficiente de modulação de comprimento de canal.

A modulação de comprimento de canal está de certa forma sobe controle do projetista porque  $\lambda$  é inversamente proporcional a  $L$  [12]. Uma expressão para  $\lambda$  [13] é:

$$\lambda = \frac{k_{ds}}{2L\sqrt{V_{DS} - V_{eff} + \phi_F}}$$

onde  $V_{eff} = V_{GS} - V_{TH}$ ,  $k_{ds} = \sqrt{\frac{2k_{si}\epsilon_0}{qN_A}}$ ,  $k_{si}$  é a constante dielétrica do silício (igual a 11,8),  $q$  é a carga do elétron  $1,602 \times 10^{-19} C$ ,  $N_A$  é a concentração da dopagem no substrato.

## Transcondutância

A relação entre a corrente de dreno e variação de tensão entre porta e fonte é denominada transcondutância e dada por:

$$g_m = \frac{\partial I_D}{\partial V_{GS}}$$

Aplicando a relação acima a equação de corrente do transistor, obtemos:

$$g_m = \mu_o C_{ox} \frac{W}{L} (V_{GS} - V_{TH})$$

Esta equação revela que  $g_m$  é linearmente proporcional a  $W/L$ , se  $(V_{GS} - V_{TH})$  é fixo, e linearmente proporcional a  $(V_{GS} - V_{TH})$ , se  $W/L$  é fixo. Outras duas relações para  $g_m$  podem ser derivadas a partir da relação acima e da equação de corrente. São elas

$$g_m = \sqrt{2\mu_o C_{ox} \frac{W}{L} I_D}$$

$$g_m = \frac{2I_D}{(V_{GS} - V_{TH})}$$

## Capacitâncias Intrínsecas

No tratamento de circuitos RF é importante considerarmos as capacitâncias intrínsecas do transistor MOS. Essas capacitâncias influenciam diretamente no comportamento da resposta do circuito e são classificadas por suas origens em: capacitâncias de *overlap*, capacitâncias de canal e capacitâncias de junção.

### *Capacitâncias de overlap*

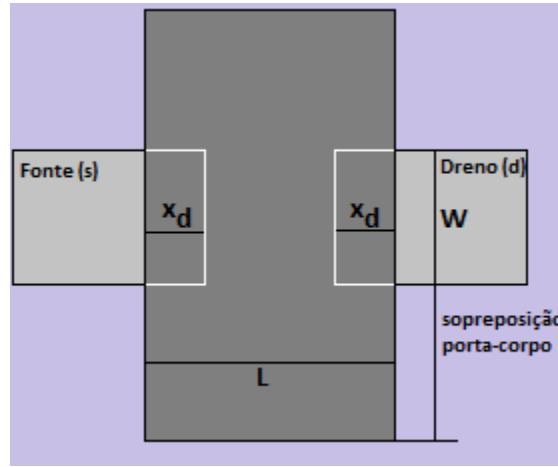

As capacitâncias de *overlap* surgem devido ao processo de fabricação dos transistores MOS. Idealmente as regiões de dreno e fonte deveriam terminar nas extremidades da região do isolante de porta. Porém, como é apresentado na Figura 7, as regiões de dreno e fonte tendem a se estenderem abaixo da camada de isolante, por uma distância  $x_d$ , conhecida como difusão lateral.

Figura 7. Capacitâncias de overlap no transistor MOS.

Essa extensão faz com que apareçam capacitâncias parasitas entre a porta e as regiões de fonte e dreno conhecidas como capacitâncias de *overlap*. Estas capacitâncias são fixas e possuem o valor de:

$$C_{GSO} = C_{GDO} = C_{ox}x_dW$$

### Capacitâncias de canal

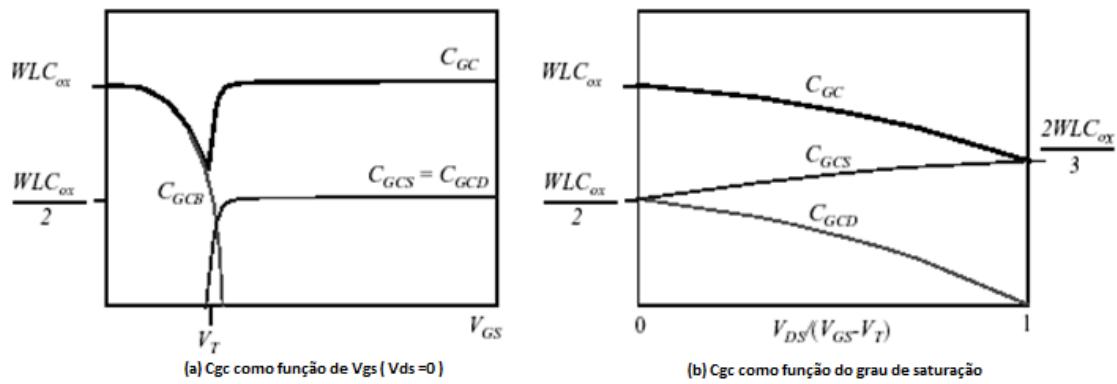

A capacitância entre porta-canal,  $C_{GC}$ , é a mais importante no transistor devido a seus valores. Ela é decomposta em três componentes:  $C_{GCS}$ , capacitância entre porta e fonte,  $C_{GCD}$ , capacitância entre porta e dreno, e  $C_{GCB}$ , capacitância entre porta e corpo. O valor destas componentes depende do ponto de operação do transistor, sendo seu comportamento melhor compreendido quando se observam os gráficos da Figura 8.

Figura 8. Variação das componentes da capacidade de porta-canal em função de  $V_{GS}$  e  $V_{DS}$  (tensão dreno-fonte).

Da Figura 8 (a), notamos que quando  $V_{GS} = 0$ , o transistor está em corte e não há canal formado; existe apenas a capacitância  $C_{GCB}$ , com valor de  $WLC_{OX}$ . Aumentando o valor de  $V_{GS}$ , há a formação de uma região de depleção abaixo da porta e posteriormente a formação do canal. Quando  $V_{GS}$  atinge  $V_{TH}$ , surge o canal e o circuito está em tríodo ( $V_{DS} = 0$ ), assim a capacitância da porta divide-se igualmente entre fonte e dreno, possuindo o valor de  $C_{GCD} = C_{GCS} = \frac{1}{2}WLC_{OX}$ .

Da Figura 8 (b) notamos que  $C_{GCD}$  gradualmente reduz a zero, enquanto  $C_{GCS}$  cresce até  $\frac{2}{3}WLC_{OX}$  com o aumento de  $\frac{V_{DS}}{(V_{GS}-V_t)}$ . A variação da tensão  $V_{DS}$  faz com que o transistor entre em saturação e as capacitâncias no canal dependem do grau de saturação, ou de  $\frac{V_{DS}}{(V_{GS}-V_t)}$ .

### Capacitâncias de junção

As capacitâncias de junção ocorrem devido às regiões de depleção dos diodos corpo-fonte e corpo-dreno, reversamente polarizados. Para uma melhor compreensão dessas capacitâncias é útil analisar a região de fonte (dreno) e a região de depleção formada em seu entorno. Na Figura 9 é apresentada a região de fonte, no qual se destacam duas regiões de depleção:

Figura 9. Detalhamento da região em torno da fonte.

- Região de depleção bottom: região de depleção formada entre a região inferior da fonte e o substrato. O valor da capacitância nessa região é  $C_{Bottom} = C_j WL_S$ , onde  $W$  é a largura do transistor,  $C_j$  é a capacitância de junção por unidade de área e  $L_S$ , o comprimento da fonte;

- Região de depleção *side-wall*: região de depleção formada entre a região lateral da fonte e o *channel-stop*, delimitador da região de fonte na fabricação. O *channel-stop* possui dopagem muito maior que o substrato, implicando em maior capacidade por área. O valor da capacidade desse componente é dado por:  $C_{SW} = C'_{jsw}x_j (W + 2L_S)$ , onde  $x_j$  é a profundidade da junção e  $C'_{jsw}$  é a capacidade de junção *side-wall* por unidade de perímetro.

Observe que não há contribuição do lado da porta para a região de depleção *side-wall*. Isso ocorre porque as capacidades ai já são consideradas nas capacidades de canal.

Combinando as capacidades vistas, temos como capacidade de junção:

$$C_{diff} = C_{Bottom} + C_{SW} = C_jWL_S + C'_{jsw}x_j(W + 2L_S)$$

### Modelo do transistor MOS com os capacitores parasitas

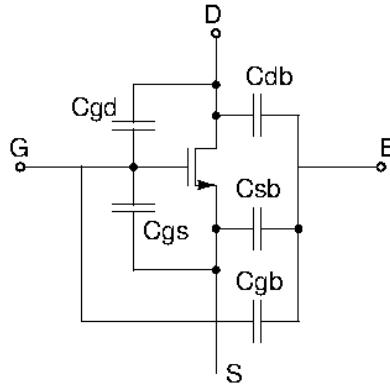

Na Figura 10 é apresentado o transistor MOS, juntamente com suas capacidades. Na Tabela 3 são apresentados os valores de cada capacitor representado na Figura 10.

Figura 10. Capacidades entre os terminais do transistor NMOS.

Tabela 3. Capacidades entre os terminais de um transistor NMOS e seus valores.

| Capacitâncias | Equação             |

|---------------|---------------------|

| $C_{GS}$      | $C_{GCS} + C_{GSO}$ |

| $C_{GB}$      | $C_{GCB}$           |

| $C_{GD}$      | $C_{GCD} + C_{GDO}$ |

| $C_{SB}$      | $C_{S_{diff}}$      |

| $C_{DB}$      | $C_{D_{diff}}$      |

### Modelo de pequenos sinais.

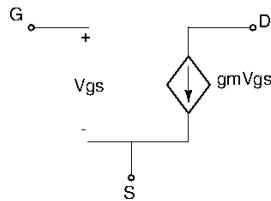

Pequenas variações nas tensões e correntes do transistor podem ser modeladas por um conjunto básico de componentes eletrônicos chamado modelo de pequenos sinais. Esse modelo é utilizado para realizar análises de circuitos. O modelo mais simples para o transistor é apresentado na Figura 11, o qual consiste de apenas uma fonte de corrente controlada por tensão. Esse modelo serve para um transistor operando em forte inversão na região de saturação.

Figura 11. Modelo de pequenos sinais simples do transistor NMOS.

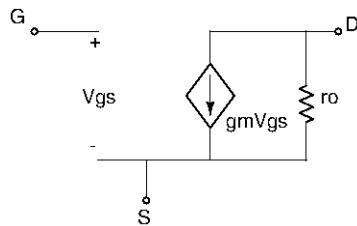

A figura revela que a corrente de dreno é controlada pela tensão de entrada, ou seja,  $I_D = gmV_{GS}$ . A porta permanece aberta o que implica, neste modelo, uma corrente de porta nula. Agregando um resistor ao circuito, como mostrado na Figura 12, se representa a modulação de comprimento de canal e a variação de  $I_D$  com respeito à  $V_{DS}$ .

Figura 12. Modelo de pequenos sinais do transistor NMOS, considerando a modulação de canal.

A variável  $r_o$  é a resistência de saída do transistor para análise de pequenos sinais. Essa resistência é definida como  $r_o = (\frac{\partial I_D}{\partial V_{DS}})^{-1}$ . Na literatura esse valor é aproximado por [14]:

$$r_o \cong \frac{1}{\lambda I_D}$$

Modelos mais completos consideram capacitâncias com relação aos terminais do transistor, como apresentado na Figura 13, para baixas frequências, e na Figura 14, para altas frequências.

Figura 13. Modelo de pequenos sinais para baixas frequências.

Na Figura 14 também está modelado o efeito de corpo através de uma fonte de corrente dependente controlada pela tensão  $V_{SB}$ . Os resistores  $r_D$ ,  $r_S$  e  $r_B$  modelam os contatos ôhmicos dos terminais de dreno, fonte e corpo respectivamente. O resistor  $r_G$ , modela além do contacto ôhmico da porta também a resistência do material de porta.

Figura 14. Modelo de pequenos sinais do transistor NMOS completo.

## Indutores Integrados

Indutores são componentes utilizados em circuitos integrados normalmente para acertar a resposta em frequência. As principais características de um indutor são os valores da indutância e do seu fator de qualidade,  $Q$ .

O parâmetro  $Q$  é uma figura de mérito adimensional importante em indutores. Fisicamente é a correlação entre energia que pode ser armazenada no componente e a energia que ele dissipada em consequência de sua não idealidade. Seu valor pode ser calculado por [1] [15]:

$$Q = 2\pi \frac{\text{máxima energia instantânea armazenada no circuito}}{\text{energia dissipada em um ciclo}}$$

Outras características importantes dos indutores são frequência de ressonância e dimensões.

Indutores integrados podem ser passivos ou ativos. Os passivos são construídos com espiras de metal coladas sobre o substrato. As espiras podem ter diversos formatos geométricos e sua forma e tamanho determinarão a indutância e o fator de qualidade do indutor. Na Figura 15 é ilustrado um indutor retangular e os parâmetros associados: o comprimento externo ( $L_{EXT}$ ), a espessura do segmento do indutor ( $t$ ), a largura do segmento ( $w$ ) e o espaçamento entre os segmentos ( $s$ ).

Figura 15. Indutor retangular e seus parâmetros geométricos.

A Figura 16 ilustra alguns formatos geométricos de indutores comumente utilizados: retangular, octogonal, hexagonal, circular [16] [17].

Figura 16. Formatos de indutores integrados: (a) retangular, (b) octogonal, (c) hexagonal e (d) circular.

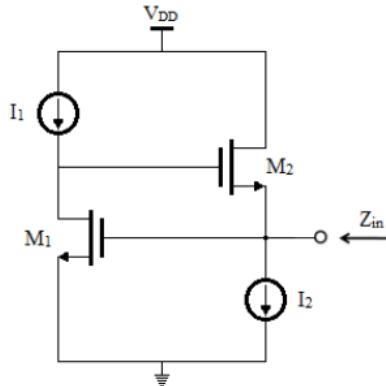

Indutores ativos são construídos com transistores e apresentam comportamento indutivo numa faixa específica de frequências. A operação de um indutor ativo é baseada no bloco gyrator [18]. Na Figura 17 é apresentado o indutor ativo utilizando transistores [19]. A configuração fonte comum, do transistor  $M_1$ , apresenta transcondutância negativa enquanto a dreno comum, do transistor  $M_2$ , apresenta transcondutância positiva. As transcondutâncias opostas emulam o atraso de fase necessário para se ter a reatância indutiva.

Figura 17. Circuito MOS Indutor ativo.

O presente trabalho utilizou-se de indutores passivos retangulares. Os indutores passivos apresentam os seguintes benefícios em comparação aos indutores ativos: menor ruído, não consomem potência e podem ser usados em altas frequências de operação. Como desvantagem, indutores passivos têm dimensões muitos elevadas.

### Degradação em indutores passivos integrados

Nos indutores passivos, devido às variações de corrente, há variações do campo magnético, causando efeitos indesejados que o degradam. Os principais efeitos indesejados são: o efeito pelicular, o efeito de proximidade e as correntes eddy [20].

#### Efeito Pelicular

Quando se tem um sinal elétrico em alta frequência aplicado a um condutor qualquer, o sinal não é transmitido no interior deste condutor, mas se propaga pela região periférica. Isso é consequência do fato dos elétrons do condutor se distribuírem para a superfície. Há dessa forma uma redução na área efetiva por onde passa o sinal e, consequentemente, o aumento da resistência do condutor. Este é o chamado efeito pelicular que ocorre também nos segmentos dos indutores integrados, o que acarreta um aumento nas perdas do indutor à medida que se aumenta a frequência de operação.

A partir das equações de campo elétrico e magnético, podemos encontrar o fator  $\delta$ , chamado de profundidade de penetração ou profundidade pelicular, *skin depth*, sendo o valor para o qual a densidade de corrente vale  $1/e$  relativamente a superfície [21]. Seu valor é dado pela equação [17]:

$$\delta = \sqrt{\frac{2}{\mu\sigma\omega}}$$

onde  $\mu$  é a permeabilidade magnética do material ( $\sim 4\pi 10^{-7} H/m$ ),  $\sigma$  é a condutividade do material do condutor e  $\omega$  é a frequência em rad/s ( $\omega = 2\pi f$ ).

### Efeito de Proximidade

O campo magnético dos condutores adjacentes altera a distribuição de correntes de um segmento, gerando altas densidades de corrente nas bordas que estão mais afastadas das linhas de campo dos campos magnéticos. Este é o chamado efeito de proximidade.

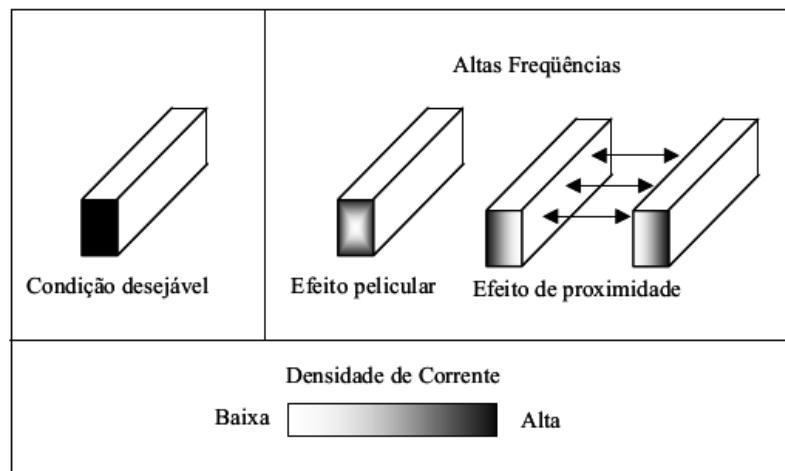

Tanto o efeito pelicular como o efeito de proximidade causa o aumento da resistência dos segmentos, o que degrada o fator de qualidade do indutor (devido ao aumento da dissipação de energia por efeito Joule no próprio condutor) [22]. A Figura 18 ilustra o comportamento das correntes nos segmentos de um indutor, à medida que a frequência aumenta [23]. São mostrados tanto o efeito pelicular como o efeito de proximidade.

Figura 18. Distribuição das correntes nos segmentos de um indutor para baixas e altas frequências.

## Correntes Eddy

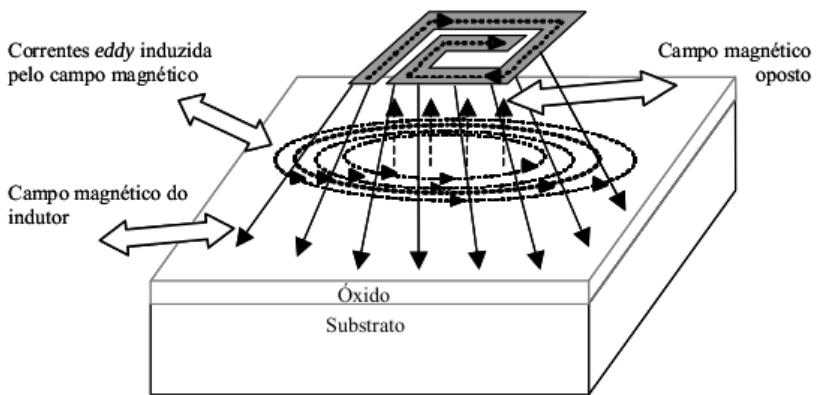

As correntes elétricas que passam pelo indutor geram um campo magnético e parte deste acaba penetrando no substrato. Quando há variações nas correntes do indutor, o campo magnético gerado também varia, causando o aparecimento de um campo elétrico no substrato. Este campo fará com que surjam correntes no substrato, as chamadas correntes eddy [24]. As correntes eddy causarão o aparecimento de um campo magnético que, segundo a lei de Lenz, é oposto ao campo induzido pelo indutor, como pode ser observado na Figura 19.

Figura 19. Correntes induzidas no substrato.

As correntes de eddy têm três efeitos negativos: reduzem o valor de  $L$ , devido ao fluxo magnético reverso gerado no substrato; reduzem o valor do  $Q$ , devido à dissipação de energia no substrato (efeito Joule); aumentam o ruído no *chip*, pois parte da corrente gerada no substrato se difunde e pode atingir circuitos próximos.

A intensidade da corrente do substrato é inversamente proporcional à sua resistividade, o que sugere que substratos de alta resistividade são melhores para se obter indutores de qualidade. Infelizmente substratos de alta resistividade aumentariam muito a possibilidade de disparo de estruturas bipolares parasitas, causando o chamado *latch-up*.

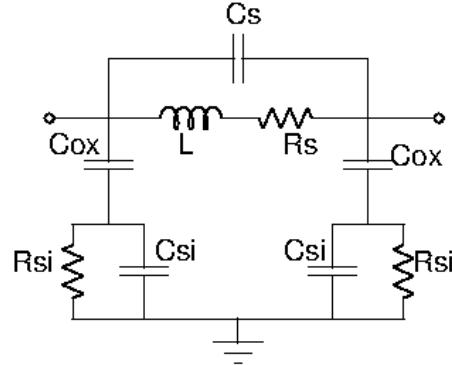

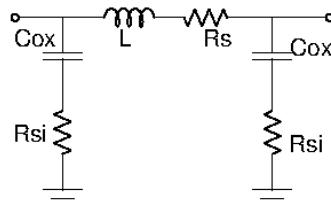

## Círcuito Equivalente

Um modelo elétrico muito utilizado para indutores integrados está ilustrado na Figura 20 e denomina-se modelo PI [25]. O modelo abrange a indutância das espiras ( $L$ ), a resistência série dos segmentos ( $R_S$ ), a capacitância entre os segmentos ( $C_S$ ), a capacitância entre os segmentos do indutor e o substrato ( $C_{OX}$ ), a capacitância do substrato ( $C_{si}$ ) e a resistência do substrato ( $R_{si}$ ). Assim, por este modelo, o indutor é caracterizado eletrica-

mente por seis parâmetros (que podem ou não variar com a frequência): a indutância  $L$ , as resistências  $R_S$  e  $R_{si}$  e as capacitâncias  $C_S$ ,  $C_{OX}$ , e  $C_{si}$ .

Figura 20. Modelo equivalente para o indutor integrado.

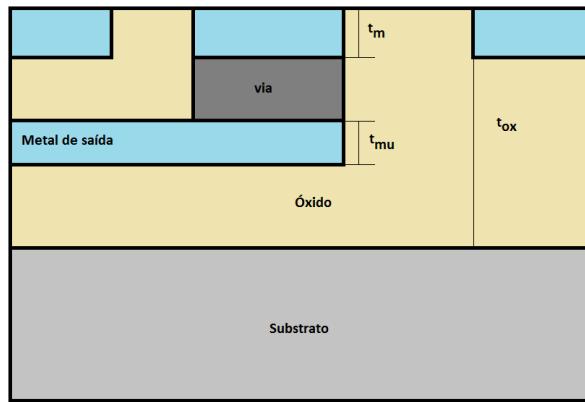

A Figura 21 ilustra as várias espessuras que caracterizam um indutor de uma espira: espessura do segmento de metal ( $t_m$ ); espessura do metal utilizado para a saída do indutor ( $t_{ms}$ ); espessura total das camadas de isolante ( $t_{ox}$ ), espessura do isolante entre a camada de metal dos segmentos e o metal de saída ( $t_{ox,ms-m}$ ) [17].

Figura 21. Espessuras que caracterizam o indutor de uma espira.

Nas próximas seções serão apresentadas expressões para cada um dos seis parâmetros descritos anteriormente. Estas serão utilizadas no *software* MATLAB para determinar os parâmetros do modelo PI de um indutor. Vale ressaltar que o conjunto de equações analíticas descrito abaixo, para determinar os parâmetros do indutor, é um dos muitos encontrados na literatura.

## Indutância

A indutância  $L$ , para indutor passivo retangular Figura 15, pode ser dada pela equação abaixo [26]:

$$L = k_L \left( \frac{A_T^{\frac{3}{2}}}{w^2} \right) \left( \frac{A_M^{\frac{5}{3}}}{A_T} \right) \left( \frac{w}{w+s} \right)^{\frac{1}{4}}$$

onde  $k_L$  é uma constante de proporcionalidade ( $1,3 \times 10^{-7}$ ),  $A_M$  é área total de metal do indutor retangular e  $A_T$  é a área total ocupada pelo indutor, sendo ela caracterizada por  $L_{EXT}$ .

## Resistência Série

A resistência série  $R_s$  pode ser dada pela equação a seguir [27], que modela à resistividade dos segmentos de metal e o efeito pelicular [28].

$$R_s = \frac{\rho_M l_T}{w \delta (1 - e^{-(\frac{t_M}{\delta})})}$$

onde  $\rho_M$  é a resistividade do metal,  $t_M$  é a espessura da camada metálica,  $l_T$  é o comprimento total do metal do indutor e  $\delta$  é a profundidade pelicular dada por [20]:

$$\delta = \sqrt{\frac{2\rho_M}{\omega\mu}}$$

## Capacitância entre os Segmentos

A capacidade entre os segmentos do indutor ( $C_s$ ) tem um valor muito pequeno e pode ser calculada pela expressão [20] [17].

$$C_s = nw^2 \frac{\epsilon_{ox}}{t_{ox,ms-m}}$$

onde  $n$  é o número de voltas do indutor,  $w$  é a largura dos segmentos,  $t_{ox,ms-m}$  é a espessura entre metais e  $\epsilon_{ox}$  é a constante dielétrica do isolante entre a primeira camada de metal utilizada no indutor e o metal de saída ( $3,45 \times 10^{-11} F/m$  para óxido de silício).

## Capacitância do Isolante

O valor desta capacitância depende, principalmente, da espessura do isolante entre o indutor e o substrato ([20], [16]) e pode ser dada por:

$$C_{ox} = \frac{1}{2} \frac{\epsilon_{ox}}{t_{ox}} l_T w$$

onde  $t_{ox}$  é a espessura do isolante entre indutor e substrato. O fator 1/2 da equação é decorrente do modelo do indutor considerar dois elementos  $C_{ox}$  em paralelo (Figura 15).

## Capacitância do Substrato

A capacitância do substrato pode ser calculada pela equação [29]:

$$C_{si} = \frac{1}{2} \frac{\epsilon_{si}}{t_{si}} l_T w$$

onde  $\epsilon_{si}$  permissividade dielétrica do silício ( $1,04 \times 10^{-10} F/m$ ) e  $t_{si}$  é a espessura do silício. O fator 1/2 da equação é decorrente do modelo do indutor considerar dois  $C_{si}$  em paralelo.

## Resistência do Substrato

Uma das equações para esta resistência está apresentada a seguir [26]. Ela modela as perdas no substrato causadas pelas correntes que aí aparecem (correntes eddy).

$$R_{si} = 2\rho_{si} \left( \frac{t_{si}^2}{t_{si}^2 + A_T} \right)$$

onde  $\rho_{si}$  é a resistividade do substrato e  $A_T$  é a área total do indutor. O fator 2 da equação é decorrente do modelo do indutor considerar dois  $R_{si}$  em paralelo.

## Limitações do Circuito Equivalente

Embora sejam considerados muitos elementos parasitas no modelo do circuito equivalente do indutor, algumas relações fornecidas apresentam limitações. Uma primeira limitação é que na equação da resistência série não está incluído o efeito de proximidade, que causa o aumento do valor da resistência. Felizmente o efeito de proximidade é praticamente insignificante se comparado com o efeito pelicular [17]. Outra limitação é que o

efeito da indutância mútua entre o substrato e o indutor não está sendo considerado. Essa indutância mútua aparece devido tanto ao fluxo magnético gerado pelo indutor, que atravessa o substrato, quanto ao fluxo magnético gerado pelas correntes eddy no substrato, que atravessa o indutor [17]. Por fim, também não estão incluídas no modelo utilizado as capacitâncias laterais entre os segmentos do indutor.

## Amplificadores de baixo ruído – LNA

### Parâmetros de projeto

#### Ruído

Ruído é definido como qualquer sinal de interferência aleatória que não tem relação com o sinal de interesse. Essas interferências, para resistores e transistores MOS, são principalmente do tipo térmico [10].

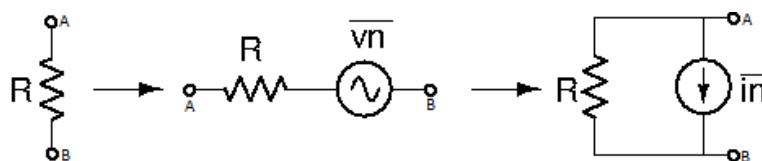

**Ruído térmico:** São sinais aleatórios causados pelo movimento térmico dos portadores de um dispositivo. É modelado por valores estatísticos [1], pois não é possível determinar um valor específico para o sinal em um determinado instante de tempo. Para um resistor, o ruído térmico pode ser modelado com uma fonte de tensão em série ao resistor, Figura 22, sendo a tensão dada por:

$$\overline{v_n^2} = 4kTR\Delta f$$

onde  $\overline{v_n^2}$  é o valor quadrático médio da tensão de ruído numa faixa de frequências  $\Delta f$ ,  $R$  o valor da resistência,  $k$  a constante de Boltzmann ( $1,38 \times 10^{-23} \text{ J/K}$ ) e  $T$  a temperatura absoluta em Kelvin.

Conforme ilustrado na Figura 22 a modelagem do ruído térmico em um resistor pode ser feita com uma fonte de corrente paralela ao resistor, ao invés de uma fonte de tensão, sendo a corrente dada por:

$$\overline{i_n^2} = 4kTG\Delta f$$

onde  $\overline{i_n^2}$  é o valor quadrático médio da corrente de ruído numa faixa de frequências  $\Delta f$  e  $G = R^{-1}$ .

Para a análise de ruído, um resistor pode ser modelado, portanto, com um resistor ideal mais uma fonte de ruído, em tensão ou em corrente, como mostra a Figura 22.

Figura 22. Modelo do ruído térmico do resistor.

Em transistores MOS o ruído térmico também está presente. A resistência no canal contribui com o chamado ruído da corrente de dreno. Esse ruído pode ser modelado com uma fonte de corrente entre fonte e dreno, sendo seu valor dado por [1]:

$$\overline{i_{nd}^2} = 4kTg_{do}\gamma\Delta f$$

onde  $\overline{i_{nd}^2}$  é o valor quadrático médio da corrente de ruído numa faixa de frequências  $\Delta f$ ,  $g_{do}$  é a condutância do canal quando  $V_{DS} = 0$ ,  $\gamma$  é o coeficiente de ruído no dreno (tem valor de 1,0 quando  $V_{DS} = 0$  e decresce até 2/3 na saturação).

Além do ruído de corrente de dreno, existe devido à agitação térmica no canal, uma segunda fonte de ruído, sendo modelado por uma fonte de corrente na porta do transistor. O valor da corrente é dado pela seguinte expressão [30]:

$$\overline{i_{ng}^2} = 4kTg_g\delta\Delta f$$

onde  $\overline{i_{ng}^2}$  é o valor quadrático médio da corrente de ruído numa faixa de frequências  $\Delta f$ ,  $\delta$  é o coeficiente de ruído da porta,  $g_g$  é a condutância formada entre porta e fonte e se expressa como:

$$g_g = \frac{\omega^2 C_{GS}^2}{5g_{do}}$$

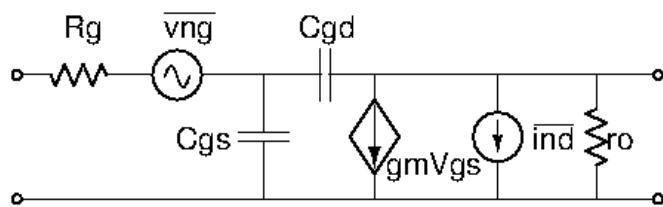

Na Figura 23 é ilustrado o modelo do transistor MOS com fontes de ruído para uso em análises de ruído. Nessa figura a fonte de corrente  $\overline{i_{ng}}$  foi substituída pela fonte de tensão equivalente, possível graças aos teoremas de dualidade de Thevenin e Norton,  $\overline{v_{ng}}$ .

Figura 23. Modelo do transistor NMOS considerando o ruído.

## Ganho

Inicialmente vamos diferenciar ganho de tensão de ganho de potência. Em amplificadores de baixo ruído o ganho de tensão é utilizado quando na saída do LNA a carga é capacitiva, onde não é preciso realizar casamento da impedância de saída. Por outro lado, quando na saída do LNA a carga é resistiva é normalmente necessário realizar casamento da impedância de saída e, nesse caso, o ganho de potência é mais interessante de ser aplicado

[31]. Neste segundo caso, quando o casamento é perfeito ou quase perfeito, o ganho de potência coincide com o ganho de tensão. O ganho de tensão é definido como a razão entre a amplitude do sinal da saída,  $v_o$ , pela amplitude do sinal da entrada,  $v_i$ . Portanto o ganho de tensão,  $A_v$ , é:

$$A_v = \frac{v_o}{v_i}$$

Uma forma interessante de expressar o ganho é através do logaritmo do seu valor:

$$A_{v_{dB}} = 20\log(|A_v|)$$

O ganho de potência  $A_p$ , por sua vez, será:

$$A_p = \frac{P_o}{P_i}$$

onde  $P_o$  e  $P_i$  correspondem às potência fornecida à saída e a potência recebida na entrada do amplificador respectivamente.

O ganho de potência também pode ser expresso por logaritmo do seu valor:

$$A_{p_{dB}} = 10\log(|A_p|)$$

O ganho de potência pode ser ainda escrito como:

$$A_p = \frac{v_o^2 R_i}{v_i^2 R_o}$$

onde  $R_i$  é a resistências de entrada e  $R_o$ , a de saída.

Quando as resistências de entrada e de saída forem iguais, o ganho de potência é igual ao quadrado do ganho de tensão:

$$A_p = {A_v}^2$$

Transformando os ganhos de tensão e potência em logaritmo, temos:

$$A_{p_{dB}} = 10 \log(|A_v|^2) = A_{v_{dB}}$$

## Linearidade

Um LNA deve fazer mais que amplificar sem acrescentar ruído. Ele deve manter um comportamento linear tanto na presença de sinais fracos como de sinais fortes [1]. Um LNA de ganho de tensão  $A_v$ , tem um comporta-

mento linear quando para um sinal de entrada com amplitude  $v_i$  o sinal de saída  $v_o$  tem amplitude  $A_v v_i$ , qualquer que seja  $v_i$ . Essa amplificação linear ocorre somente no caso ideal.

As medidas de linearidade mais utilizadas são o ponto de compressão de 1 dB (*compression point 1 dB* - CP 1 dB) e o ponto de interseção de terceira ordem ( $IP_3$ ) (Figura 24). O ponto de compressão de 1 dB referido na entrada,  $ICP_{1dB}$  ( $OCP_{1dB}$  quando referido a saída), é definido como a amplitude do sinal de entrada (amplitude do sinal de saída quando referida a saída) que faz com que o ganho tenha uma queda de 1 dB [32] (Figura 24(a)) relativamente ao valor ideal (amplificado) na saída.

A partir do ponto de compressão de 1 dB calcula-se a faixa dinâmica (FD) do circuito. A FD é a diferença entre a máxima amplitude permitida para o sinal de entrada, o valor  $ICP_{1dB}$ , e a mínima amplitude do sinal de entrada que pode ser detectada, limitada inferiormente pelo plano de ruído.

Figura 24. Amplitude de saída versus amplitude de entrada; a) ponto de compressão 1,0 dB e b) ponto de interseção de terceira ordem.

O ponto  $IP_3$  (Figura 24(b)) é um parâmetro para medir a influência das componentes de intermodulação de terceira ordem. Essas componentes de terceira ordem, geradas por tons com frequências próximas, podem dificultar a identificação do sinal original.

O  $IIP_3$  ( $IP_3$  referido a entrada) é a amplitude  $A$  do sinal na entrada  $v_i = A[\cos(\omega_1 t) + \cos(\omega_2 t)]$ , onde  $\omega_1 \approx \omega_2$ , para o qual os sinais de saída na frequência  $\omega_1$  ou  $\omega_2$  e as componentes de intermodulação de terceira ordem, nas frequências  $(2\omega_1 - \omega_2)$  ou  $(2\omega_2 - \omega_1)$ , tem amplitudes iguais.

Caso aproximemos o comportamento do ganho do LNA por [33]:

$$v_o = a_0 + a_1 v_i + a_2 v_i^2 + a_3 v_i^3 + \dots$$

onde  $v_o$  é o sinal de saída e  $a_0, a_1, \dots$  são constantes, pode-se mostrar que [2]:

$$IIP_3 = \sqrt{\frac{4|a_1|}{3|a_3|}}$$

Pode-se mostrar também que os parâmetros  $ICP_{1dB}$  e  $IIP_3$  estão relacionados por [2]:

$$20 \log \left( \frac{IIP_3}{ICP_{1dB}} \right) = 9,6 \text{ dB}$$

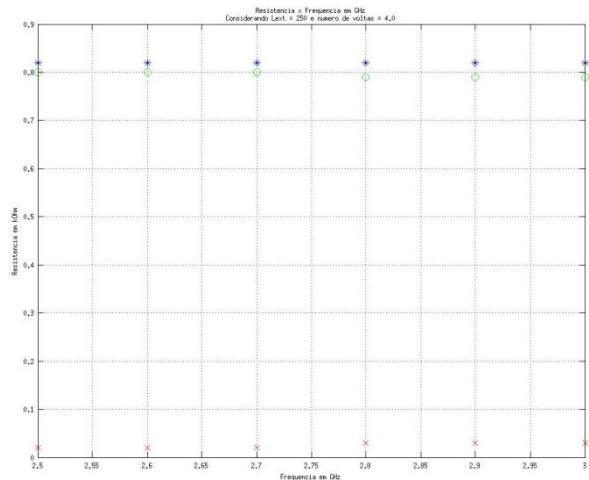

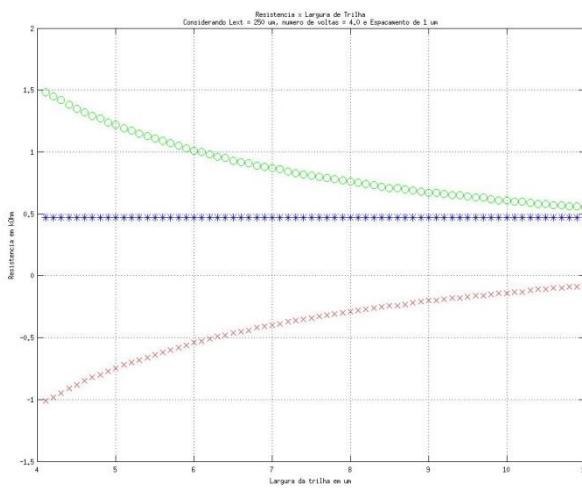

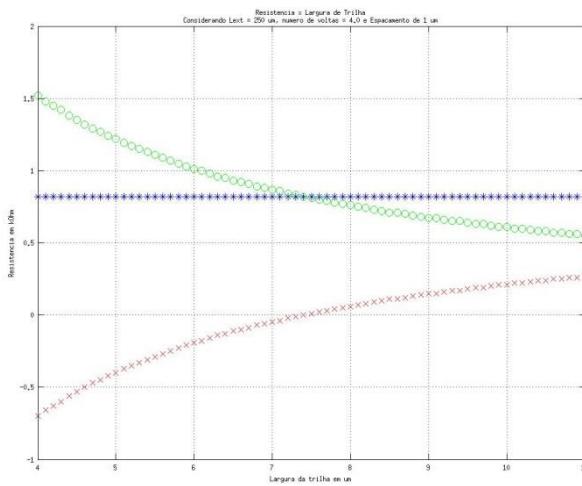

## Estabilidade