**UNIVERSIDADE DE SÃO PAULO

ESCOLA DE ENGENHARIA DE SÃO CARLOS**

**Leonardo Maronezi Pizani**

**Estudo sobre métodos para aceleração de um algoritmo

de reconstrução de imagens de tomossíntese digital

mamária baseado em hardware GPU e programação

CUDA**

**São Carlos**

**2020**

**Leonardo Maronezi Pizani**

**Estudo sobre métodos para aceleração de um algoritmo

de reconstrução de imagens de tomossíntese digital

mamária baseado em hardware GPU e programação

CUDA**

Monografia apresentada ao Curso de Engenharia Elétrica com Ênfase em Eletrônica, da Escola de Engenharia de São Carlos da Universidade de São Paulo, como parte dos requisitos para obtenção do título de Engenheiro Eletricista.

Orientador: Prof. Dr. Marcelo A. C. Vieira

**São Carlos

2020**

AUTORIZO A REPRODUÇÃO TOTAL OU PARCIAL DESTE TRABALHO,

POR QUALQUER MEIO CONVENCIONAL OU ELETRÔNICO, PARA FINS

DE ESTUDO E PESQUISA, DESDE QUE CITADA A FONTE.

Ficha catalográfica elaborada pela Biblioteca Prof. Dr. Sérgio Rodrigues Fontes da

EESC/USP com os dados inseridos pelo(a) autor(a).

P695e      Pizani, Leonardo Maronezi

Estudo sobre métodos para aceleração de um

algoritmo de reconstrução de imagens de tomossíntese

digital mamária baseado em hardware GPU e programação

CUDA / Leonardo Maronezi Pizani; orientador Marcelo

Andrade da Costa Vieira. São Carlos, 2020.

Monografia (Graduação em Engenharia Elétrica com

ênfase em Eletrônica) -- Escola de Engenharia de São

Carlos da Universidade de São Paulo, 2020.

1. GPU. 2. Programação paralela. 3. CUDA. 4.

Tomossíntese digital mamária. I. Título.

# FOLHA DE APROVAÇÃO

Nome: Leonardo Maronezi Pizani

Título: "Aceleração e Optimização de Código via Programação em GPU com CUDA"

Trabalho de Conclusão de Curso defendido e aprovado

em 25/06/2020,

com NOTA 9,0 ( Nove, Zero ), pela Comissão Julgadora:

**Prof. Associado Marcelo Andrade da Costa Vieira - Orientador -

SEL/EESC/USP**

**Prof. Associado Evandro Luis Linhari Rodrigues - SEL/EESC/USP -

Aposentado**

**Mestre Rodrigo de Barros Vimieiro - Doutorando - SEL/EESC/USP**

**Coordenador da CoC-Engenharia Elétrica - EESC/USP:

Prof. Associado Rogério Andrade Flauzino**

## **AGRADECIMENTOS**

Agradeço primeiramente a meus pais, por todo apoio e confiança demonstrados desde muito antes de eu ingressar na universidade.

Agradeço a meus amigos, por tornarem suportável mesmo as experiências mais estressantes. Agradeço especialmente ao Daniel e ao Rafael, com quem dividi minhas dúvidas e frustrações durante o desenvolvimento deste trabalho.

Agradeço ao Rodrigo, pelas dicas e pelos conhecimentos ofertados, sem os quais este trabalho não seria possível.

Agradeço por fim ao meu professor orientador, Marcelo, e a todos os outros professores e funcionários desta universidade, cujo trabalho contribui ativamente para a existência do ensino público superior de qualidade no país.

## RESUMO

Pizani, L. M. **Estudo sobre métodos para aceleração de um algoritmo de reconstrução de imagens de tomossíntese digital mamária baseado em hardware GPU e programação CUDA**. 2020. 73p. Monografia (Trabalho de Conclusão de Curso) - Escola de Engenharia de São Carlos, Universidade de São Paulo, São Carlos, 2020.

Este trabalho tem como objetivo explorar algumas das funcionalidades do CUDA *toolkit*, utilizando uma *toolbox* de reconstrução de imagens de tomossíntese digital mamária desenvolvida para MATLAB. Foram testadas diferentes abordagens nesse processo, modificando o algoritmo empregado nos testes a fim de aumentar seu grau de paralelismo e permitir a aplicação de algumas das principais ferramentas disponibilizadas pelo CUDA *toolkit*, como *shared memory*, *texture objects* e *streams*. Como o algoritmo utilizados nos testes tem a função de gerar projeções 2D, foram aplicadas métricas de comparação de imagens em todos as projeções geradas utilizando as imagens do algoritmo original como controle, a fim de validar os resultados. Foram calculados os tempos médios de cada abordagem e os valores obtidos foram comparados para permitir uma análise de quais métodos apresentaram os melhores resultados e quais fatores mais influenciaram no tempo de execução. Com os testes foi possível concluir que, dependendo do algoritmo utilizado, a redução de tempo na execução do algoritmo pode chegar a mais de 180 vezes ao empregar CUDA. Os resultados mais significativos foram consequência das mudanças que aumentaram o grau de paralelismo do algoritmo, porém o uso de ferramentas mais específicas do CUDA *toolkit* também podem fazer uma diferença de até 1,8 vezes quando aplicadas nas condições certas.

**Palavras-chave:** GPU, programação paralela, CUDA, tomossíntese digital mamária.

## **ABSTRACT**

Pizani, L. M. **Study on methods for accelerating an image reconstruction algorithm for digital breast tomosynthesis based on GPU hardware and CUDA programming.** 2020. 73p. Undergraduate Final Project, Sao Carlos School of Engineering, University of Sao Paulo, Sao Carlos, Brazil, 2020.

This work aims to explore some of the CUDA toolkit features, using the toolbox for reconstruction of digital breast tomosynthesis images developed in MATLAB. Different approaches were tested in this process, modifying the algorithm used in the tests to increase its degree of parallelism and allow the application of some of the main tools available by CUDA toolkit, such as shared memory, texture objects and streams. In order to validate this work, the accelerated projection images were compared against the results provided by the original toolbox. For each acceleration method, the average execution time was evaluated in order to choose the best algorithm, and also what are the most important factors that impact the acceleration procedure. Depending on the technique applied, the time reduction factor, in the algorithm execution, can reach more than 180 times, when using GPU with the CUDA toolkit. The higher speed improvements were achieved due to the higher parallelism applied in the algorithms. Moreover, specific CUDA techniques can also increase the speedup up to 1.8 times, when applied in the right manner.

**Keywords:** GPU, parallel programming, CUDA toolkit, digital breast tomosynthesis.

## LISTA DE FIGURAS

|                                                                                                                         |    |

|-------------------------------------------------------------------------------------------------------------------------|----|

| Figura 1 – Comparativo entre quantidade de operações em ponto flutuante por segundo em CPU e em GPU. . . . .            | 23 |

| Figura 2 – Comparativo entre largura de banda de memória em CPU e em GPU. .                                             | 24 |

| Figura 3 – Cronologia das linguagens de programação de GPUs. . . . .                                                    | 25 |

| Figura 4 – Comparativo entre o <i>hardware</i> das GPUs e das CPUs. . . . .                                             | 26 |

| Figura 5 – Exemplo de uma arquitetura de GPU. . . . .                                                                   | 27 |

| Figura 6 – Exemplo de um <i>streaming multiprocessor</i> . . . . .                                                      | 28 |

| Figura 7 – Linguagens de programação e aplicações suportadas pelo <i>CUDA toolkit</i> . .                               | 29 |

| Figura 8 – Fluxo de execução de um programa utilizando CUDA. . . . .                                                    | 30 |

| Figura 9 – Formação de uma <i>grid</i> de <i>threads</i> paralelas. . . . .                                             | 31 |

| Figura 10 – Hierarquia de memória. . . . .                                                                              | 33 |

| Figura 11 – Localização dos diferentes tipos de memória. . . . .                                                        | 34 |

| Figura 12 – Funcionamento da <i>pinned memory</i> . . . . .                                                             | 36 |

| Figura 13 – Sobreposição de tarefas com o uso de <i>streams</i> . . . . .                                               | 37 |

| Figura 14 – Aquisição das projeções por um equipamento de tomossíntese. . . . .                                         | 39 |

| Figura 15 – Geometria de um equipamento de tomossíntese digital mamária. . . . .                                        | 41 |

| Figura 16 – Representação dos <i>phantoms</i> utilizados. . . . .                                                       | 45 |

| Figura 17 – Interpolação Bilinear. . . . .                                                                              | 52 |

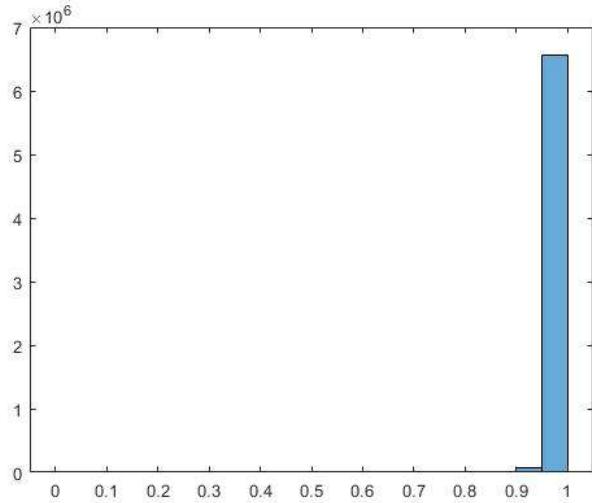

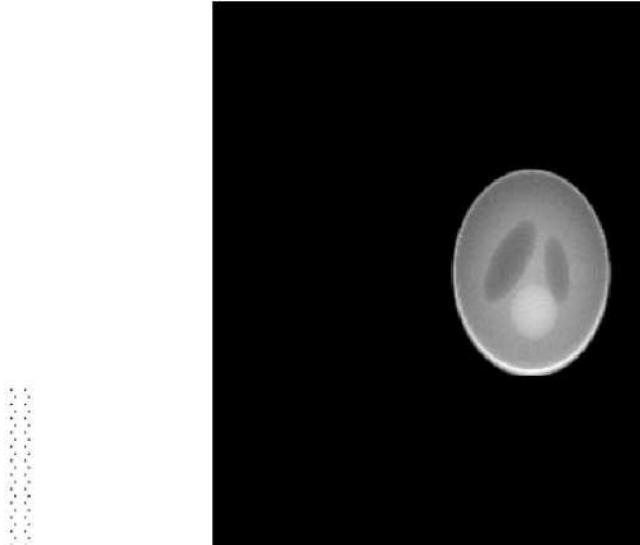

| Figura 18 – Projeções obtidas com o algoritmo de controle. . . . .                                                      | 55 |

| Figura 19 – Projeções obtidas com o algoritmo feito em C++. . . . .                                                     | 57 |

| Figura 20 – Mapa de SSIM de uma das projeções do <i>phantom</i> BR3D, feita em C++. .                                   | 58 |

| Figura 21 – Exemplo de projeção obtida com uso da ferramenta de interpolação própria da <i>texture memory</i> . . . . . | 62 |

| Figura 22 – Diferença entre a projeção da figura 21 e sua correspondente de controle. .                                 | 62 |

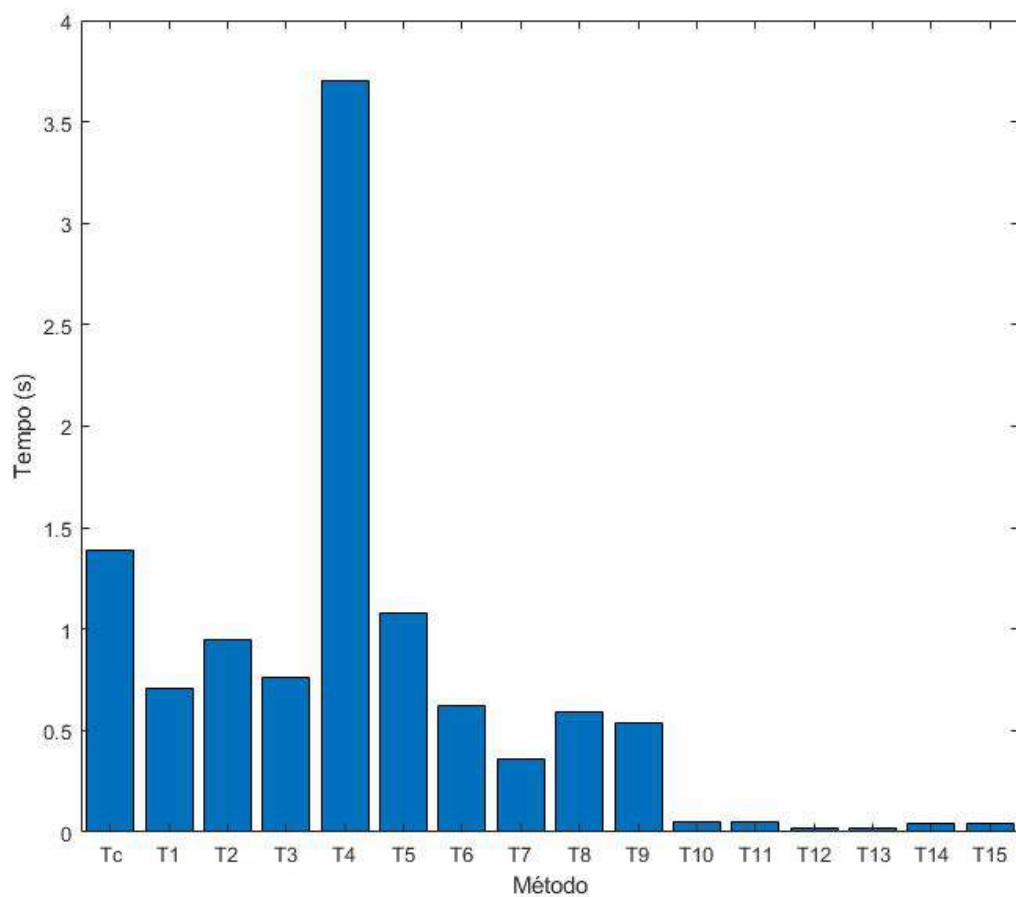

| Figura 23 – Tempos de execução do <i>phantom</i> de Shepp-Logan para cada método testado. . . . .                       | 66 |

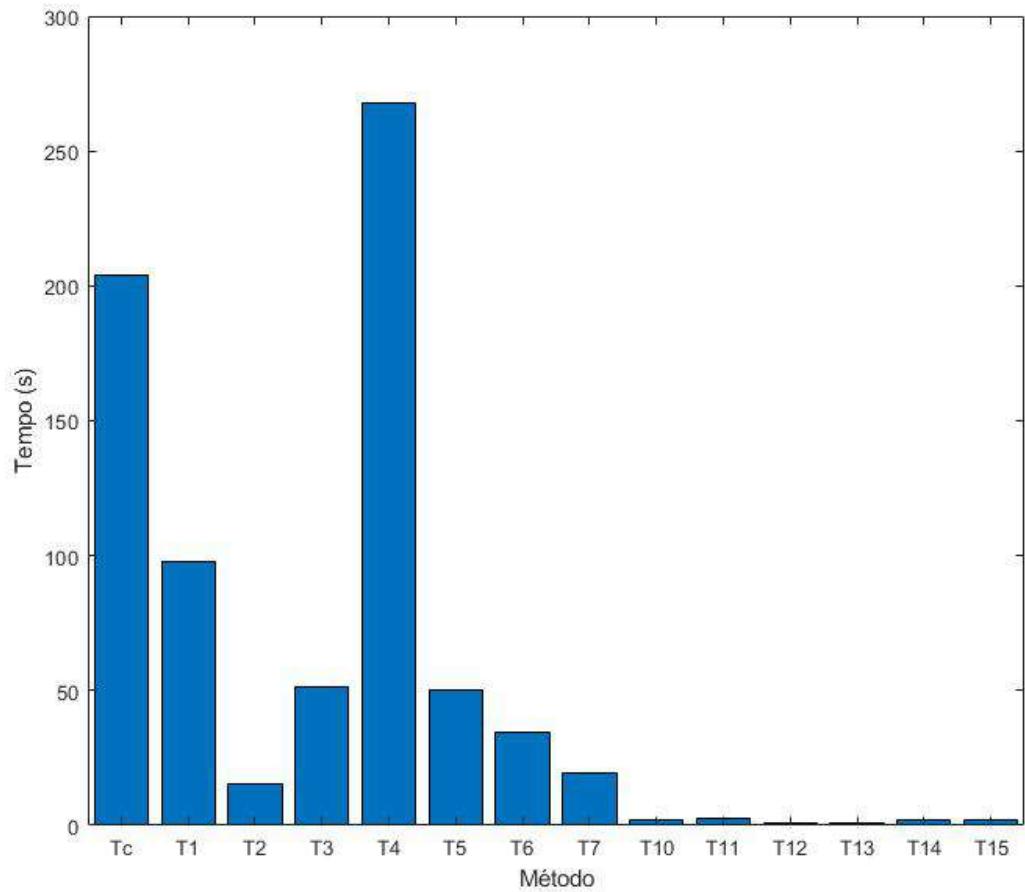

| Figura 24 – Tempos de execução do <i>phantom</i> BR3D para cada método testado. . .                                     | 67 |

## LISTA DE TABELAS

|                                                                                                                                                                                                                           |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Tabela 1 – Principais parâmetros que descrevem o sistema. . . . .                                                                                                                                                         | 41 |

| Tabela 2 – Componentes de <i>hardware</i> e versões de <i>software</i> utilizados. . . . .                                                                                                                                | 45 |

| Tabela 3 – Parâmetros que descrevem os sistemas de cada <i>phantom</i> . . . . .                                                                                                                                          | 46 |

| Tabela 4 – Resultado da função "gpuDevice". . . . .                                                                                                                                                                       | 47 |

| Tabela 5 – Argumentos de uma "mexFunction". . . . .                                                                                                                                                                       | 48 |

| Tabela 6 – Tempo ( $T_c$ ), em segundos, que o algoritmo de controle demorou para ser executado. . . . .                                                                                                                  | 55 |

| Tabela 7 – Resultados da aplicação de métricas comparativas em cada uma das 9 projeções adquiridas usando a GPU diretamente no MATLAB com as suas correspondentes de controle. . . . .                                    | 56 |

| Tabela 8 – Tempo ( $T_1$ ), em segundos, que o algoritmo de controle demorou para ser executado ao usar <i>gpuArray</i> como tipo de variável de entrada. . . . .                                                         | 56 |

| Tabela 9 – Tempo ( $T_2$ ), em segundos, que o algoritmo de controle demorou para ser executado ao usar a função "arrayfun"para calcular X e Y. . . . .                                                                   | 56 |

| Tabela 10 – Resultados da aplicação de métricas comparativas em cada uma das 9 projeções adquiridas com os métodos que usaram C++, mas não usaram <i>shared memory</i> , com as suas correspondentes de controle. . . . . | 58 |

| Tabela 11 – Tempo ( $T_3$ ), em segundos, que o algoritmo feito em C++ demorou para ser executado. . . . .                                                                                                                | 59 |

| Tabela 12 – Tempo ( $T_4$ ), em segundos, que o algoritmo feito em C++ demorou para ser executado usando CUDA somente nos cálculos da interpolação, fatia por fatia. . . . .                                              | 59 |

| Tabela 13 – Tempo ( $T_5$ ), em segundos, que o algoritmo feito em C++ demorou para ser executado usando CUDA somente nos cálculos de X e Y, fatia por fatia. . . . .                                                     | 59 |

| Tabela 14 – Tempo ( $T_6$ ), em segundos, que o algoritmo feito em C++ demorou para ser executado usando CUDA nos cálculos de X, Y e interpolação, fatia por fatia. . . . .                                               | 59 |

| Tabela 15 – Resultados da aplicação de métricas comparativas em cada uma das 9 projeções adquiridas com os métodos que usaram C++ e <i>shared memory</i> com as suas correspondentes de controle. . . . .                 | 60 |

| Tabela 16 – Tempo ( $T_7$ ), em segundos, que o algoritmo feito em C++ demorou para ser executado usando CUDA nos cálculos de X, Y e interpolação, fatia por fatia, com uso de <i>shared memory</i> . . . . .             | 60 |

|                                                                                                                                                                                                                                                                    |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Tabela 17 – Tempo ( $T_8$ ), em segundos, que o algoritmo feito em C++ demorou para ser executado usando CUDA nos cálculos de X, Y e interpolação, fatia por fatia, com uso de <i>texture memory</i> . . . . .                                                     | 61 |

| Tabela 18 – Tempo ( $T_9$ ), em segundos, que o algoritmo feito em C++ demorou para ser executado usando CUDA nos cálculos de X, Y e interpolação, fatia por fatia, com uso de <i>texture memory</i> diretamente no cálculo da interpolação. . . . .               | 61 |

| Tabela 19 – Tempo ( $T_{10}$ ), em segundos, que o algoritmo feito em C++ demorou para ser executado usando CUDA nos cálculos de X, Y e interpolação, todas as fatias simultaneamente, sem usar <i>shared memory</i> . . . . .                                     | 63 |

| Tabela 20 – Tempo ( $T_{11}$ ), em segundos, que o algoritmo feito em C++ demorou para ser executado usando CUDA nos cálculos de X, Y e interpolação, todas as fatias simultaneamente, usando <i>shared memory</i> . . . . .                                       | 63 |

| Tabela 21 – Tempo ( $T_{12}$ ), em segundos, que o algoritmo feito em C++ demorou para ser executado usando CUDA nos cálculos de X, Y e interpolação, todas as fatias simultaneamente, alterando a disposição das <i>threads</i> e <i>thread blocks</i> . . . . .  | 64 |

| Tabela 22 – Tempo ( $T_{13}$ ), em segundos, que o algoritmo feito em C++ demorou para ser executado usando CUDA nos cálculos de X, Y e interpolação, todas as projeções simultaneamente. . . . .                                                                  | 64 |

| Tabela 23 – Tempo ( $T_{14}$ ), em segundos, que o algoritmo feito em C++ demorou para ser executado usando CUDA nos cálculos de X, Y e interpolação, todas as projeções simultaneamente, mas uma fatia de cada vez. . . . .                                       | 65 |

| Tabela 24 – Tempo ( $T_{15}$ ), em segundos, que o algoritmo feito em C++ demorou para ser executado usando CUDA nos cálculos de X, Y e interpolação, todas as projeções simultaneamente, mas uma fatia de cada vez, utilizando múltiplas <i>streams</i> . . . . . | 65 |

| Tabela 25 – Tempo de execução obtido em cada método. . . . .                                                                                                                                                                                                       | 66 |

## **LISTA DE ABREVIATURAS E SIGLAS**

|       |                                           |

|-------|-------------------------------------------|

| 1D    | Uma Dimensão                              |

| 2D    | Duas Dimensões                            |

| 3D    | Três Dimensões                            |

| CPU   | Central Processing Unit                   |

| CUDA  | Compute Unified Device Architecture       |

| DRAM  | Dynamic Random Access Memory              |

| FLOPS | FLoating-point Operations Per Second      |

| FPGA  | Field Programmable Gate Array             |

| GPU   | Graphics Processing Unit                  |

| GPGPU | General Purpose Graphics Processing Unit  |

| NaN   | Not a Number                              |

| PCIe  | Peripheral Component Interconnect Express |

| PSNR  | Peak Signal to Noise Ratio                |

| RAM   | Random Access Memory                      |

| SM    | Streaming Multiprocessor                  |

| SSIM  | Structural Similarity Index               |

## SUMÁRIO

|              |                                                                  |           |

|--------------|------------------------------------------------------------------|-----------|

| <b>1</b>     | <b>INTRODUÇÃO</b>                                                | <b>19</b> |

| <b>1.1</b>   | <b>Contextualização e Motivação</b>                              | <b>19</b> |

| <b>1.2</b>   | <b>Objetivo</b>                                                  | <b>22</b> |

| <b>1.3</b>   | <b>Organização da Monografia</b>                                 | <b>22</b> |

| <b>2</b>     | <b>TEORIA</b>                                                    | <b>23</b> |

| <b>2.1</b>   | <b>Unidades de Processamento Gráfico</b>                         | <b>23</b> |

| <b>2.1.1</b> | <b>Histórico</b>                                                 | <b>24</b> |

| <b>2.2</b>   | <b>Arquitetura Das placas gráficas da NVIDIA</b>                 | <b>25</b> |

| <b>2.3</b>   | <b>CUDA toolkit</b>                                              | <b>29</b> |

| <b>2.4</b>   | <b>Reconstrução de Imagens para Tomossíntese Digital Mamária</b> | <b>39</b> |

| <b>2.4.1</b> | <b>Geometria do Equipamento</b>                                  | <b>40</b> |

| <b>2.4.2</b> | <b>Algoritmos</b>                                                | <b>42</b> |

| <b>3</b>     | <b>MATERIAIS E MÉTODOS</b>                                       | <b>45</b> |

| <b>3.1</b>   | <b><i>Phantoms 3D</i></b>                                        | <b>45</b> |

| <b>3.2</b>   | <b>MATLAB</b>                                                    | <b>46</b> |

| <b>3.3</b>   | <b>Metodologia</b>                                               | <b>49</b> |

| <b>4</b>     | <b>RESULTADOS E DISCUSSÕES</b>                                   | <b>55</b> |

| <b>4.1</b>   | <b>Utilizando os recursos do MATLAB</b>                          | <b>55</b> |

| <b>4.2</b>   | <b>Utilizando CUDA</b>                                           | <b>57</b> |

| <b>5</b>     | <b>CONCLUSÃO</b>                                                 | <b>69</b> |

|              | <b>Referências</b>                                               | <b>71</b> |

# 1 INTRODUÇÃO

## 1.1 Contextualização e Motivação

Em 1965 o cofundador da Intel, Gordon Earle Moore, montou um gráfico que descrevia a quantidade de transistores que era possível integrar em um único chip desde 1959, ano da invenção do circuito integrado, até então. Observando a tendência do gráfico Moore previu que a quantidade de transistores por chip dobraria a cada ano, previsão essa que veio a se tornar conhecida como Lei de Moore (Huang et al., 2010; Yao, 2004). Posteriormente essa previsão foi revisada e o período de tempo necessário para dobrar a quantidade de transistores em um chip foi alterada para dois anos (Denning and Lewis, 2017; McCool et al., 2012).

A Lei de Moore se mostrou uma estimativa razoável durante décadas, entretanto o aumento no número de componentes não foi o único responsável pelo crescimento exponencial na velocidade de processamento observada, sendo o aumento da frequência de chaveamento dos transistores, também chamada de frequência de clock, um fator igualmente relevante (Theis and Solomon, 2010; Ramanathan et al., 2015; Denning and Lewis, 2017). Durante muito tempo esses dois fatores foram suficientes para manter a elevada taxa de desenvolvimento tecnológico praticamente inalterada, porém ambos possuem limites físicos fundamentais.

Transistores menores necessitam de menos energia, mas isso requer que a tensão de operação diminua juntamente com o tamanho dos transistores, o que pode afetar sua operação, uma vez que é necessária uma tensão mínima para que o componente mude sua característica condutiva corretamente e represente o nível lógico que deveria (Theis and Solomon, 2010; Ramanathan et al., 2015). Além disso as altas velocidades de clock induzem grandes variações de corrente, o que implica em maiores correntes de fuga e em um consumo de energia que não diminui na mesma proporção que a dimensão dos transistores. Em outras palavras aumentar o número de componentes em um chip de área fixa, como um processador por exemplo, também aumenta seu consumo de energia e, como consequência, gera mais calor(Huang et al., 2010; Ramanathan et al., 2015; Yao, 2004). Esse aumento progressivo no consumo de potência e geração de calor dos processadores é chamado pela Intel de *power wall*.

Ao juntar as limitações da *power wall* com a latência de acesso a memória é possível entender porque a indústria passou a fixar a tensão de alimentação dos transistores e parou de simplesmente aumentar sua velocidade de chaveamento, mesmo que ainda continuem diminuindo seu tamanho (Theis and Solomon, 2010; Ramanathan et al., 2015). Sabendo da impossibilidade de manter o crescimento exponencial da velocidade de processamento

pelos meios supracitados foi necessário a adoção de um novo paradigma.

Uma opção muito estudada recentemente é a integração de chips tridimensionais, uma nova tecnologia que, em vez de integrar todos os transistores de um chip lado a lado em um mesmo plano, visa empilhar verticalmente vários desses planos. Essa tecnologia possibilita maior densidade de componentes por chip e novas organizações de circuitos, porém isso também resulta em um drástico aumento na dissipação de calor no componente, fator que já é preocupante mesmo nas tecnologias bidimensionais (Ahmed and Schuegraf, 2011; Loh et al., 2007; Huang et al., 2010).

Outra opção é diminuir os esforços em desenvolver máquinas com um único processador cada vez mais poderoso e concentrá-los em desenvolver computadores com vários núcleos de processamento, e é exatamente isso que a indústria tem feito nos últimos anos (Adve et al., 2008). Praticamente todos os computadores modernos já se utilizam deste princípio, possuindo pelo menos um recurso paralelo em seu *hardware*, de fato chips *multicore* estão tão difundidos atualmente que até no simples ato de comprar um *smartphone* novo é comum se deparar com a escolha de processadores *dualcore*, *quadcore* e até *octacore* (McCool et al., 2012), embora nem todo mundo saiba o que essas terminologias significam. Os processadores *multicore*, como são chamados, podem não ser necessariamente mais rápidos que um modelo de um núcleo dos mais avançados, mas utilizando do princípio de programação paralela podem apresentar desempenho geral superior (Keckler et al., 2009; Geer, 2005).

A programação paralela consiste de dividir grandes tarefas em frações menores e mais simples, que são executadas de forma independente entre si, concomitantemente, e em diferentes núcleos de processamento. Desta forma diretivas de *loop*, por exemplo, dependendo de sua natureza, podem ter todos seus ciclos efetuados de uma única vez, pouRANDO grande quantidade de tempo. Contudo poucas são as ferramentas que efetivamente foram desenvolvidas pensando em programação em paralelo (McCool et al., 2012).

As primeiras linguagens de máquina eram fundamentalmente seriais, ou seja, efetuavam tarefas consecutivas sequencialmente, até mesmo diretivas de *loop* eram apenas uma forma abreviada de executar tarefas sequenciais uma grande quantidade de vezes. Com o passar do tempo a serialização se arraigou no processo de programação de tal forma que a maioria dos recursos e dos conhecimentos sobre programação difundidos até hoje são essencialmente serializados, mesmo que o *hardware* utilizado possua alto grau de paralelismo (McCool et al., 2012).

Isso porém está mudando, recentemente o paralelismo vem sendo cada vez mais utilizado em vários domínios, incluindo computação gráfica, computação de alto desempenho e também em ambas combinadas (Adve et al., 2008). As chamadas GPUs (Graphics Processing Unit) são processadores altamente especializados em renderização de imagens, efetuando grandes quantidades de cálculos de ponto flutuante rapidamente, chegando até

a alcançar a casa dos GFLOPS ( $10^9$  Floating-point Operations Per Second) (McClanahan, 2010; Shah and Yousaf, 2019). Uma vez que o cálculo da cor de um pixel na tela é independe da cor dos demais pixels, a paralelização das placas gráficas foi a escolha lógica, escolha essa que tem feito com que o desenvolvimento das GPUs acelerasse ainda mais que o previsto pela Lei de Moore (McClanahan, 2010; Brodkorb et al., 2013).

De fato a tecnologia das placas gráficas cresceram tão rapidamente que tem também sido utilizada em computação de propósito geral juntamente com as CPUs (Central Processing Unit), recebendo assim o nome de GPGPU (General Purpose Graphics Processing Unit)(Brodkorb et al., 2013). As GPGPUs não são a única alternativa para programar paralelamente de forma eficiente, mas tendem a ser as mais utilizadas, uma vez que placas gráficas já são facilmente encontradas em computadores atuais por padrão, não necessitando de um hardware completamente avesso ao cotidiano da maioria dos programadores, como é o caso das FPGAs (Field Programmable Gate Array), por exemplo (Brodkorb et al., 2013).

Os maiores fabricantes de placas gráficas atualmente são dois, AMD e NVIDIA, porém a NVIDIA tem apresentado mais destaque no meio acadêmico devido a concepção de sua arquitetura de computação paralela própria, chamada CUDA (Compute Unified Device Architecture) (Brodkorb et al., 2013).

A demanda por custo computacional vem crescendo rapidamente e é seguro dizer que vai continuar crescendo, principalmente no meio acadêmico, no qual novos algoritmos cada vez mais complexos são desenvolvidos a todo momento. Esses novos algoritmos necessitam ser cada vez mais velozes, uma vez que para serem refinados e validados são necessários inúmeros testes, do contrário todo o processo de desenvolvimento será lento e dispendioso.

Além disso, a simples aplicabilidade de um algorítimo pode depender de sua velocidade, como é o caso das aplicações médicas, já que muitas vezes os médicos e seus pacientes necessitam dos resultados de exames o mais rápido possível. O processo de reconstrução de tomossíntese digital mamária, por exemplo, composto por métodos de projeção, retroprojeção e técnicas de filtragem de ruído, já é conhecido há bastante tempo, mas devido ao seu alto custo computacional tardou a ser foco de pesquisas (Vimieiro, Rodrigo de Barros, 2019).

Os processos iterativos de reconstrução são lentos sequencialmente mesmo quando executados em CPUs modernas, mas acarretam em grandes benefícios no âmbito da saúde, uma vez que tem por objetivo gerar imagens para o rastreio do câncer de mama (Vimieiro, Rodrigo de Barros, 2019). Por esse motivo são ótimas opções para se acelerar usando programação paralela, e a tecnologia CUDA, além de permitir isso, proporciona uma experiência de programação familiar ao usuário, permitindo que ele programe em uma linguagem que já domine (Arora, 2012).

## **1.2 Objetivo**

O presente trabalho visa investigar o funcionamento de algumas das diferentes ferramentas e métodos de optimização e aceleração de código que a NVIDIA disponibiliza através do CUDA *Toolkit*, utilizando como objeto de estudo uma *toolbox* de reconstrução de tomossíntese digital mamária que, em trabalhos anteriores, já foi testada em um modelo de programação serial. Contudo, como o objetivo deste trabalho é entender como empregar CUDA de forma efetiva, o único algoritmo utilizado nos testes foi o que gera as projeções, a fim de que, futuramente, os aprendizados deste trabalho possam ser aplicados para acelerar o processo de reconstrução por completo.

## **1.3 Organização da Monografia**

Além deste capítulo o presente trabalho está dividido em mais 4 secções, que são respectivamente Teoria, Materiais e Métodos, Resultados e Conclusão.

O Capítulo 2, Teoria, apresenta de maneira detalhada os conceitos da programação paralela, bem como sua aplicação por meio das novas diretivas de C++ proporcionadas pela arquitetura CUDA. Nesse capítulo também são explicados os conceitos básicos a respeito de reconstrução de imagens de tomossíntese digital mamária, de forma breve e resumida, apenas a fim de orientar adequadamente o leitor e possibilitar melhor entendimento da secção de Resultados.

O Capítulo 3, Materiais e Métodos, descreve como foi a abordagem utilizada para efetuar a tradução dos códigos seriais previamente estudados em códigos paralelizados por meio de CUDA.

O Capítulo 4, Resultados, tem a finalidade de expor os resultados obtidos durante o decorrer do trabalho e discorrer a respeito deles.

Por fim no Capítulo 5, Conclusão, é apresentada uma visão geral de como se procedeu o trabalho e se ele alcançou as expectativas.

## 2 TEORIA

Esta seção visa apresentar os conceitos fundamentais sobre os quais o presente trabalho se sustenta e sem os quais não seria possível discorrer sobre as seções que se seguem. Primeiramente é apresentada a arquitetura das placas de vídeo da NVIDIA, seguida do princípio de funcionamento do CUDA e por fim o algoritmo utilizado na análise.

### 2.1 Unidades de Processamento Gráfico

As placas de vídeo são projetadas para efetuar quantidades massivas de cálculos por segundo, a fim de renderizar imagens de alta resolução sem comprometer a sua taxa de quadros, um problema inerente de *video-games*. De fato a evolução das placas gráficas foi, de início, quase que exclusivamente impulsionada pelos *video-games*, mas quando seu potencial computacional foi percebido, elas passaram a ser utilizadas para as mais diversas aplicações (Owens et al., 2008).

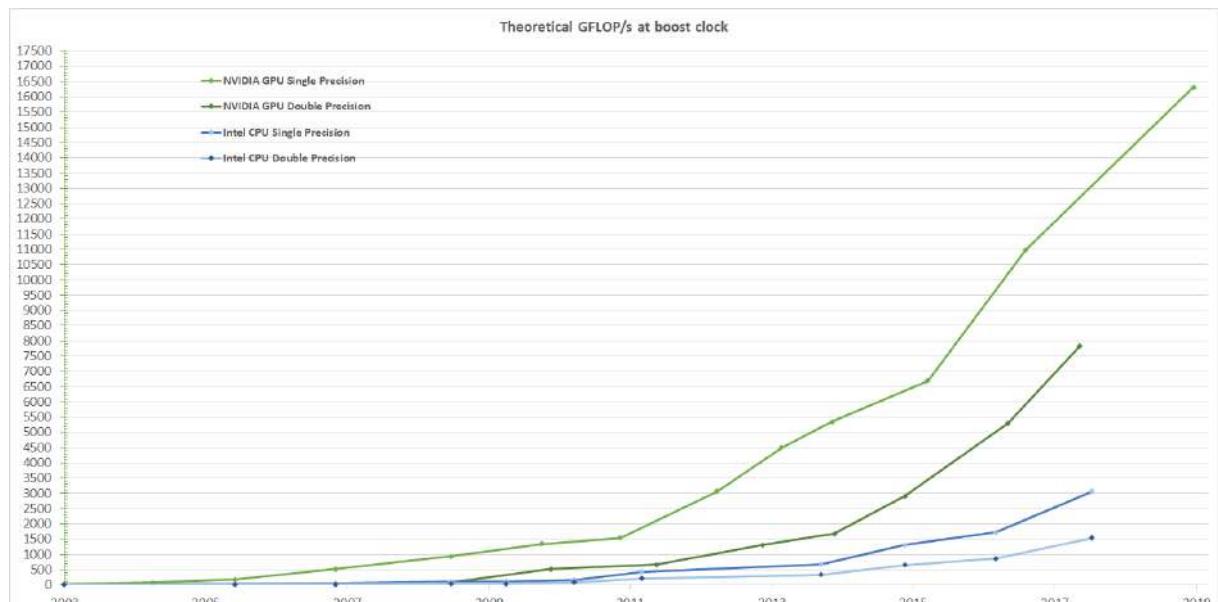

A crescente demanda por capacidade de processamento gráfico continua a impulsionar o desenvolvimento de placas gráficas cada vez mais poderosas, conforme demonstrado nas figuras 1 e 2 (NVIDIA, 2020).

Figura 1: Comparativo entre quantidade de operações em ponto flutuante por segundo em CPU e em GPU.

Fonte: NVIDIA (2020).

Figura 2: Comparativo entre largura de banda de memória em CPU e em GPU.

Fonte: NVIDIA (2020).

### 2.1.1 Histórico

Conforme seu nome sugere, as primeiras *graphics processing units* (GPUs) possuíam *hardware* dedicado a renderização gráfica, sendo concebidas para efetuar operações utilizando apenas primitivas geométricas, mais especificamente pontos, linhas e triângulos. Formas geométricas complexas por sua vez eram divididas em múltiplas faces triangulares, cujo brilho, matiz e saturação eram calculadas e direcionadas a seus respectivos *pixels* (Arora, 2012; Kim et al., 2012).

As primeiras GPUs trabalhavam com uma quantidade significativamente limitada de operações, que tinham como único propósito converter estruturas no espaço tridimensional em imagens bidimensionais (Owens et al., 2008). Era difícil desenvolver e optimizar programas voltados a GPUs, mas quando tais programas funcionavam eles demonstravam uma incrível melhora no quesito de velocidade quando comparado com códigos similares que eram executados em CPU, o que conduziu ao desenvolvimento de novas e intuitivas formas de programar em GPU (Owens et al., 2008).

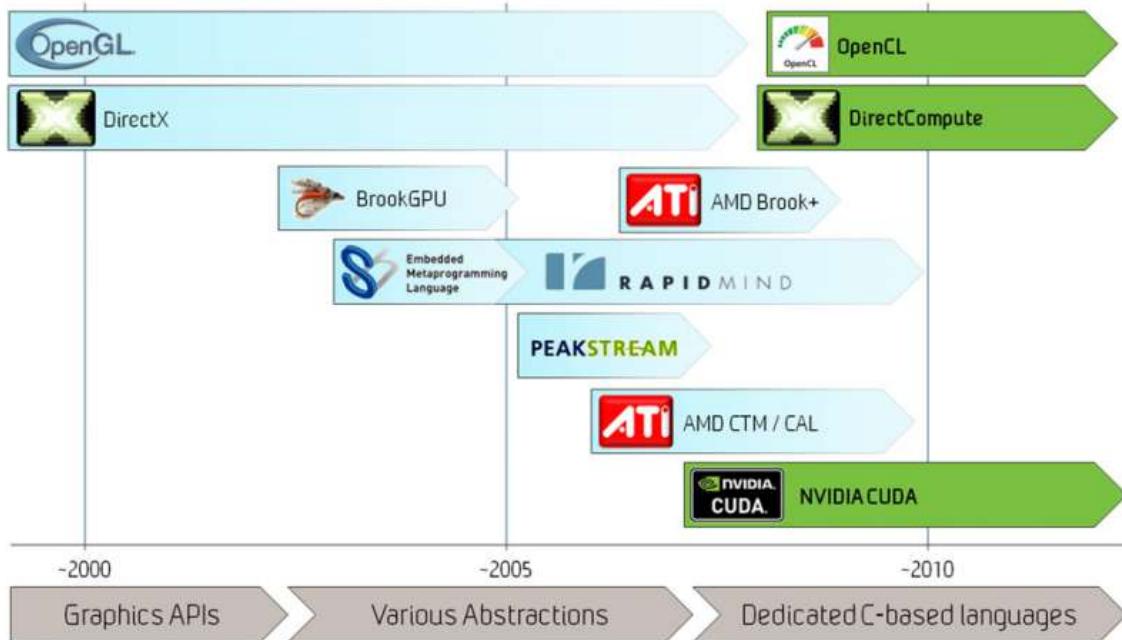

Quando as GPUs começaram a ser usadas para aplicações não gráficas, tais aplicações tinham que ser reformuladas para se adequar linguagens de *shaders*, como OpenGL ou DirectX por exemplo, sendo necessário descrever problemas de todos os tipos através de primitivas gráficas apenas. A dificuldade de se fazer isso levou ao desenvolvimento de outras formas de utilizar as GPUs visando facilitar o processo (Nickolls and Dally, 2010; Kim et al., 2012).

Figura 3: Cronologia das linguagens de programação de GPUs.

Fonte: Owens et al. (2008).

O avanço no *hardware* das GPUs também foi direcionado no sentido de melhorar sua programabilidade, inclusive para aplicações de uso geral, possibilitando até mesmo o surgimento de ferramentas com CUDA, DirectCompute, and OpenCL, que atualmente são as predominantes no uso de GPGPUs (Owens et al., 2008). O CUDA *toolkit* da NVIDIA permite ao programador utilizar uma abordagem mais tradicional ao lidar com sua GPU, de forma que ele possa programar em uma linguagem já familiar a ele, como C ou Fortran, por exemplo (Kim et al., 2012). A figura 3 ilustra de forma simplificada a cronologia do desenvolvimento das linguagens de programação de GPUs.

## 2.2 Arquitetura Das placas gráficas da NVIDIA

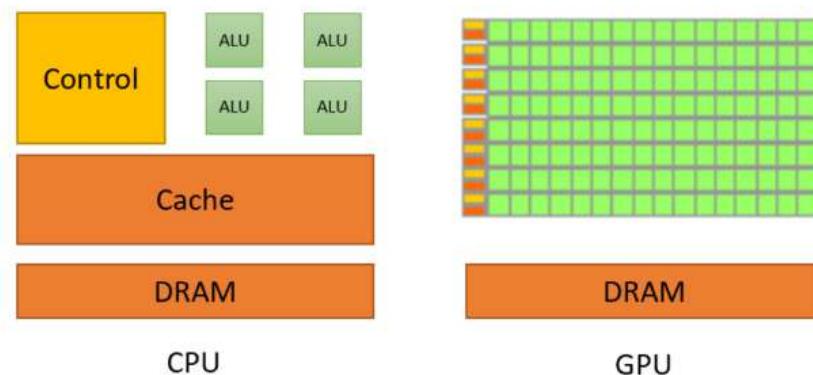

A evolução da arquitetura das GPUs e das CPUs tomaram direções bem diferentes. As CPUs evoluíram para executar uma única tarefa por vez, uma após a outra, sistematicamente, aplicando todos seus recursos e potencial em cada operação, de forma a tomar a menor quantidade de tempo possível em cada tarefa. As GPUs por sua vez utilizam seus recursos para executar grandes quantidades de trabalho independente entre si a cada ciclo, isso porque a resolução das imagens que deve renderizar continuam crescendo, mas a quantidade de imagens que o olho humano consegue perceber por segundo se mantém inalterada (Owens et al., 2008) Essa diferença de paradigma teve consequências claras no *hardware* dos dispositivos, conforme ilustra a figura 4.

O fluxo de trabalho das GPUs pode ser definido como do tipo *feed-forward* de múltiplas etapas, ou seja, os resultados obtidos a cada ciclo de trabalho efetuado por

uma GPU são diretamente usados no ciclo seguinte e assim sucessivamente. Ao seguir esse modelo de funcionamento todos os ciclos de trabalho demandam elevado grau de paralelismo para atuar com eficiência, e não por coincidência, o hardware das GPUs foi desenvolvido para proporcionar exatamente isso. Quando comparada com as CPUs, a execução de cada tarefa é mais lenta, mas nesse meio tempo a quantidade de trabalho executado tende a ser muito maior, tornando o processo como um todo mais rápido em diversas situações (Owens et al., 2008).

Figura 4: Comparativo entre o *hardware* das GPUs e das CPUs.

Fonte: NVIDIA (2020).

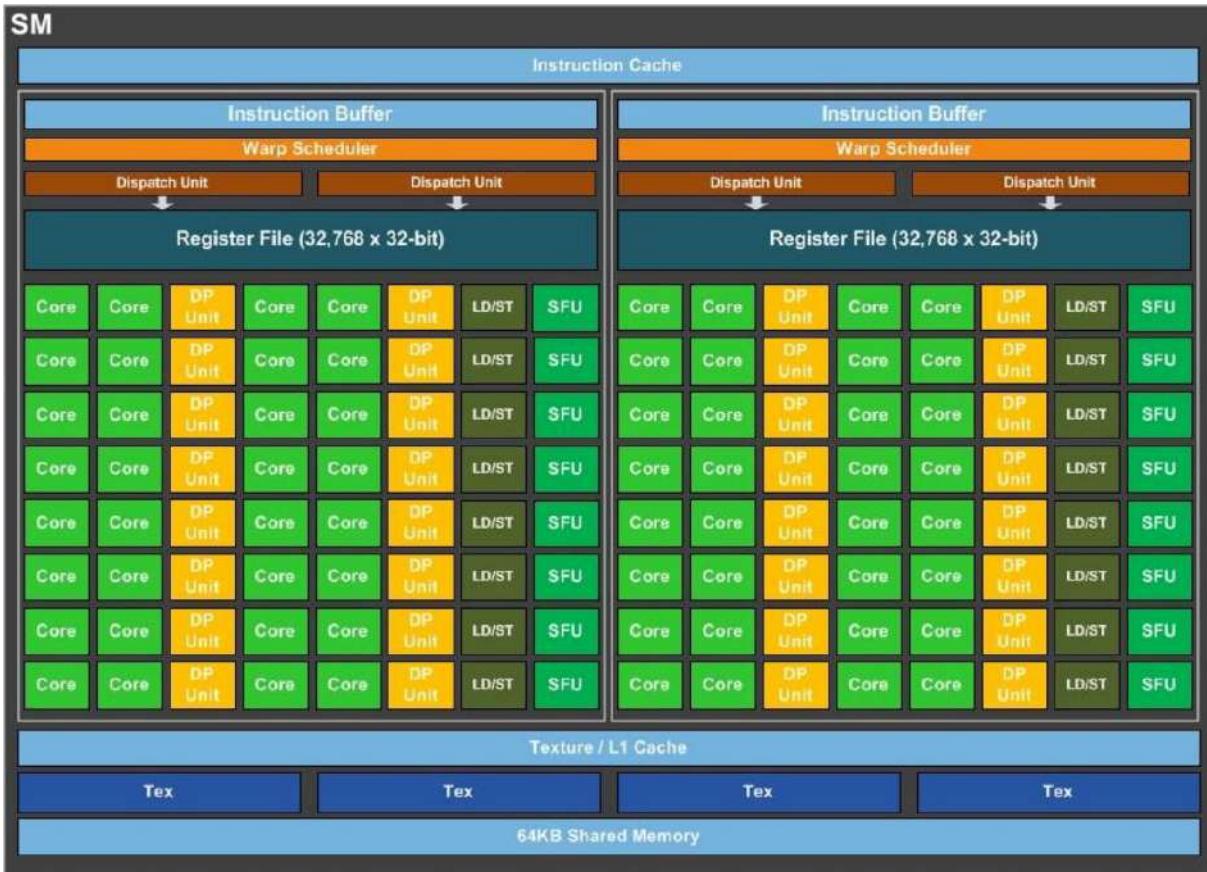

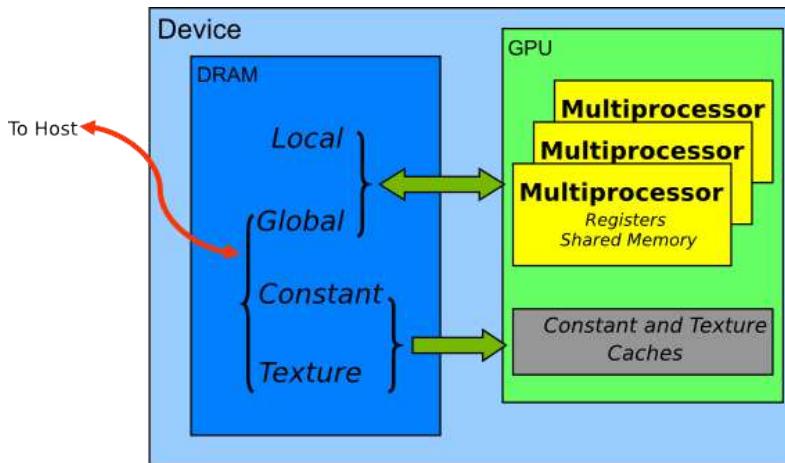

A arquitetura das GPUs da NVIDIA é formada basicamente por um conjunto de *streaming multiprocessors* (SMs), DRAM (Dynamic Random Access Memory) de alta largura de banda e registradores, conforme demonstrado na figura 5 (Arora, 2012). Os diferentes modelos de GPUs da NVIDIA variam no número de *streaming multiprocessors* (SMs) e na quantidade de memória RAM. Quanto mais numerosos são os SMs em uma GPU, melhor sua performance computacional, e quanto mais memória a GPU possui, maior sua *memory bandwidth* (Nickolls and Dally, 2010).

A comunicação entre CPU e GPU se da por meio de barramento PCIe (Peripheral Component Interconnect Express), enquanto a comunicação entre GPUs é feita pela interface NVLink. O acesso a memória DRAM da GPU por parte dos seus SMs é interfaceado por controladores de memória que trabalham de forma independente uns dos outros, permitindo acessos paralelos e direcionados, mas que mantêm alta a largura de banda (Nickolls and Dally, 2010).

Cada *thread* representa um fluxo de operações paralelo às demais *threads*, tendo seus próprios registradores, memória, pilha, endereço de instrução e flags (Nickolls and Dally, 2010). A quantidade de *threads* que compõem um *thread block* é definida pelo usuário, até um limite que pode variar a depender do modelo de GPU utilizado, como será visto mais adiante. Já as chamadas *warps* são conjuntos de 32 *threads* executadas

Figura 5: Exemplo de uma arquitetura de GPU.

Fonte: adaptada de NVIDIA (2016).

simultaneamente por um mesmo SM, o que pode ter mais ou menos *threads* que as de um *thread block* (Arora, 2012).

*GigaThread* é a unidade responsável por direcionar *CUDA threads* a SMs disponíveis, distribuindo o trabalho da melhor forma possível. Os SMs por sua vez organizam as *threads* em blocos e as executam. Conforme cada *thread block* termina de executar suas tarefas e liberam os recursos de seu respectivo SM, a *GigaThread* atribui a esse SM novas tarefas (Nickolls and Dally, 2010).

Os SMs das GPUs modernas são compostos basicamente por unidades de processamento, unidades de gerenciamento e memória (Nickolls and Dally, 2010). Algumas dessas unidades são:

- *CUDA cores*: são os núcleos de processamento da GPU, realizam um cálculo aritmético de número inteiro ou de flutuante (32bits) a cada ciclo de trabalho;

- *Special function units*: são projetadas para rápido cálculo de funções de raiz quadrada, seno, cosseno, exponencial e logarítmica usando ponto flutuante;

- *Load/store units*: executam instruções de acesso a memória. Essas unidades combinam o acesso múltiplas *threads* por vez, de forma a minimizar o número de acessos;

- *Double precision unit*: efetuam cálculos aritméticos de ponto flutuante com 64bits;

- *Warp scheduler*: seleciona, a cada ciclo de trabalho, uma *warp* para executar instruções;

- *Dispatch units*: despacham instruções retiradas da fila do *instruction cache* às *warps* que irão executá-las.

Figura 6: Exemplo de um *streaming multiprocessor*.

Fonte: adaptada de NVIDIA (2016).

Os SMs compartilham entre si memória cache de segundo nível interfaceada com a DRAM da GPU, mas cada SM também possui sua própria memória cache de primeiro nível. Cada SM é independente e dispõe de núcleos de processamento e memória o suficiente para rodar um ou mais *CUDA thread blocks*. Somando o potencial de todos os SM de uma GPU é possível rodar milhares de *threads* simultaneamente (Nickolls and Dally, 2010).

A *shared memory* contida nos SMs, como seu nome sugere, é compartilhada entre todas as *threads* em um mesmo *thread block*. O rápido acesso a *shared memory* aumenta significativamente a performance de muitas aplicações, enquanto ao mesmo tempo diminui a requisição de dados na DRAM (Nickolls and Dally, 2010).

## 2.3 CUDA toolkit

CUDA é uma plataforma de computação desenvolvida pela NVIDIA capaz de aplicar o elevado potencial de paralelização das placas de vídeo em computação de uso geral de forma simples e eficiente (NVIDIA, 2020).

Seu *toolkit* possui de um conjunto muito amplo de ferramentas para expressar paralelismo, mesmo usando de linguagens intrinsecamente seriais para isso, o que permite ao programador criar algoritmos eficientes e com elevado grau de paralelismo utilizando uma linguagem já familiar (Nickolls and Dally, 2010).

Figura 7: Linguagens de programação e aplicações suportadas pelo *CUDA toolkit*.

| GPU Computing Applications                         |                                    |                                          |                           |                             |                               |                       |

|----------------------------------------------------|------------------------------------|------------------------------------------|---------------------------|-----------------------------|-------------------------------|-----------------------|

| Libraries and Middleware                           |                                    |                                          |                           |                             |                               |                       |

| cuDNN<br>TensorRT                                  | cuFFT, cuBLAS,<br>cuRAND, cuSPARSE | CULA MAGMA                               | Thrust<br>NPP             | VSIPL, SVM,<br>OpenCurrent  | PhysX, OptiX,<br>iRay         | MATLAB<br>Mathematica |

| Programming Languages                              |                                    |                                          |                           |                             |                               |                       |

| C                                                  | C++                                | Fortran                                  | Java, Python,<br>Wrappers | DirectCompute               | Directives<br>(e.g., OpenACC) |                       |

| CUDA-enabled NVIDIA GPUs                           |                                    |                                          |                           |                             |                               |                       |

| Turing Architecture<br>(Compute capabilities 7.x)  | DRIVE/JETSON<br>AGX Xavier         | GeForce 2000 Series                      |                           | Quadro RTX Series           | Tesla T Series                |                       |

| Volta Architecture<br>(Compute capabilities 7.x)   | DRIVE / JETSON<br>AGX Xavier       |                                          |                           |                             | Tesla V Series                |                       |

| Pascal Architecture<br>(Compute capabilities 6.x)  | Tegra X2                           | GeForce 1000 Series                      |                           | Quadro P Series             | Tesla P Series                |                       |

| Maxwell Architecture<br>(Compute capabilities 5.x) | Tegra X1                           | GeForce 900 Series                       |                           | Quadro M Series             | Tesla M Series                |                       |

| Kepler Architecture<br>(Compute capabilities 3.x)  | Tegra K1                           | GeForce 700 Series<br>GeForce 600 Series |                           | Quadro K Series             | Tesla K Series                |                       |

|                                                    | EMBEDDED                           | CONSUMER DESKTOP,<br>LAPTOP              |                           | PROFESSIONAL<br>WORKSTATION | DATA CENTER                   |                       |

Fonte: NVIDIA (2020).

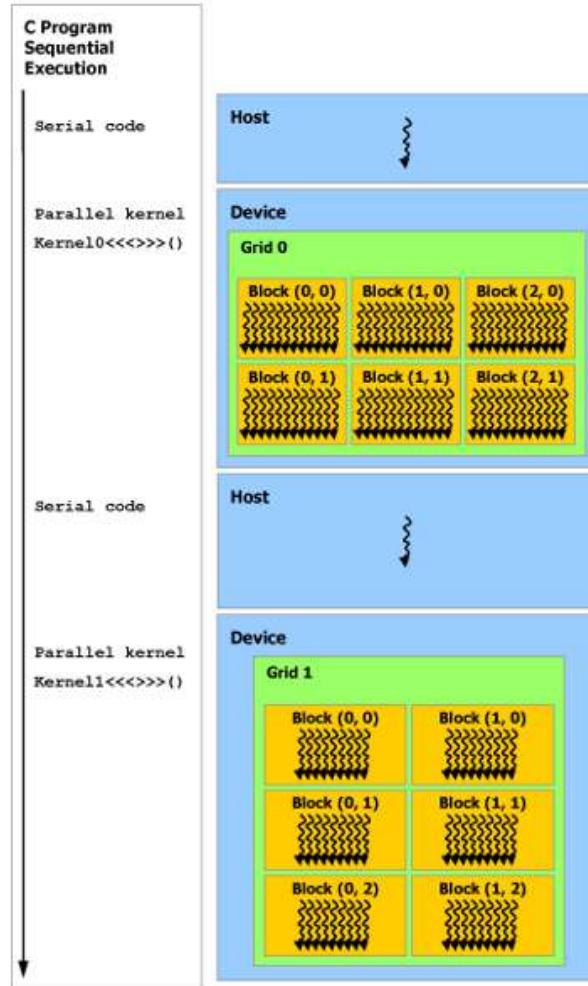

Programas desenvolvidos com CUDA usam o modelo de Programação Heterogênea, ou seja, uma parte deles roda sequencialmente na CPU enquanto a outra parte roda na GPU utilizando *threads* paralelas, conforme ilustrado na figura 8. A CPU é o *host*, responsável por coordenar todo o fluxo de execução em um programa que utiliza CUDA (NVIDIA, 2020). A parte sequencial desses programas opera como em qualquer linguagem serial, o diferencial aqui é a utilização da GPU, que será abordada utilizando linguagem C.

Figura 8: Fluxo de execução de um programa utilizando CUDA.

Fonte: NVIDIA (2020).

A CPU instancia os chamados *kernels*, que são funções descritas de forma serial no programa, mas que utilizam múltiplas *threads* ao ser executadas na GPU, referenciada daqui em diante como *device* (NVIDIA, 2020). Para chamar um *kernel* deve-se usar a seguinte sintaxe:

```

1 // Declaração do Kernel

2 __global__ void Nome ( definição das entradas) {

3     ...

4 }

5 void main() {

6     ...

7     // Chamada do Kernel

8     Nome <<< block , thread , shared , stream[ i ] >>> ( entradas );

9     ...

10 }

```

O especificador "`__global__`" é usado junto com a declaração do *kernel* para diferenciá-lo de uma função normal, significando que ele é visto por ambos dispositivos. Também existem os especificadores "`__host__`" e "`__device__`", o uso do primeiro ou de nenhum tem o mesmo significado, o de uma função exclusivamente do *host*, enquanto o segundo é uma função exclusiva do *device* e que deve ser chamada por um *kernel* (NVIDIA, 2020).

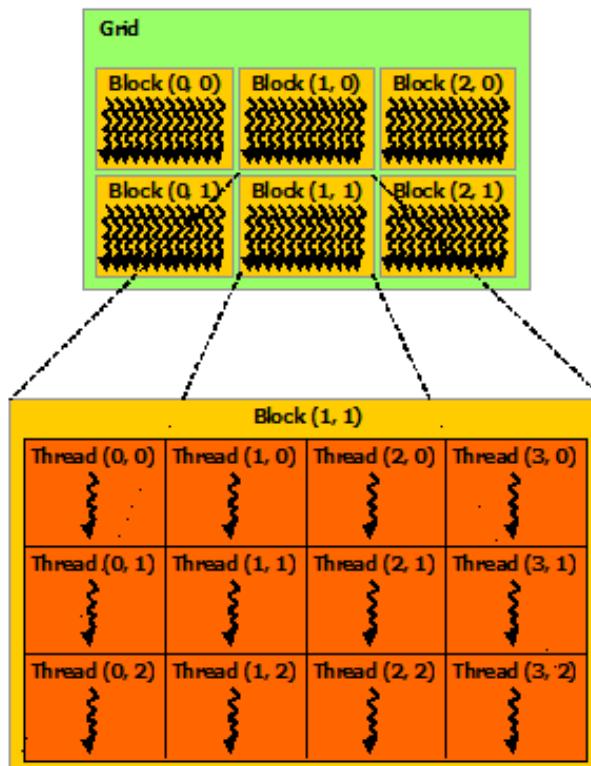

Já os argumentos entre `<<< ... >>>` definem como o *device* vai trabalhar com o *kernel*. Os dois últimos argumentos serão discutidos mais adiante, já os outros dois definem, respectivamente, a quantidade de *thread blocks* em uma *grid* e a quantidade de *threads* em um *thread block*. Como tanto a *grid* quanto os *thread blocks* podem ser unidimensionais, bidimensionais ou tridimensionais, os argumentos utilizados são do tipo "`dim3`", estruturas de dados compostas por 3 variáveis do tipo "`size_t`" que indicam respectivamente a quantidade de elementos nas dimensões x, y e z (NVIDIA, 2020).

A forma como as *threads* são organizadas para gerar *thread blocks* e *grids* pode ser vista na figura 9. Cada *thread* conhece sua posição em um *thread block*, assim como cada *thread block* conhece o número de *threads* que o compõem e sua posição na *grid*, informações essas acessíveis ao usuário também por meio de variáveis do tipo "`dim3`", "`threadIdx`", "`blockDim`" e "`blockIdx`", respectivamente (NVIDIA, 2020).

Figura 9: Formação de uma *grid* de *threads* paralelas.

Fonte: NVIDIA (2020).

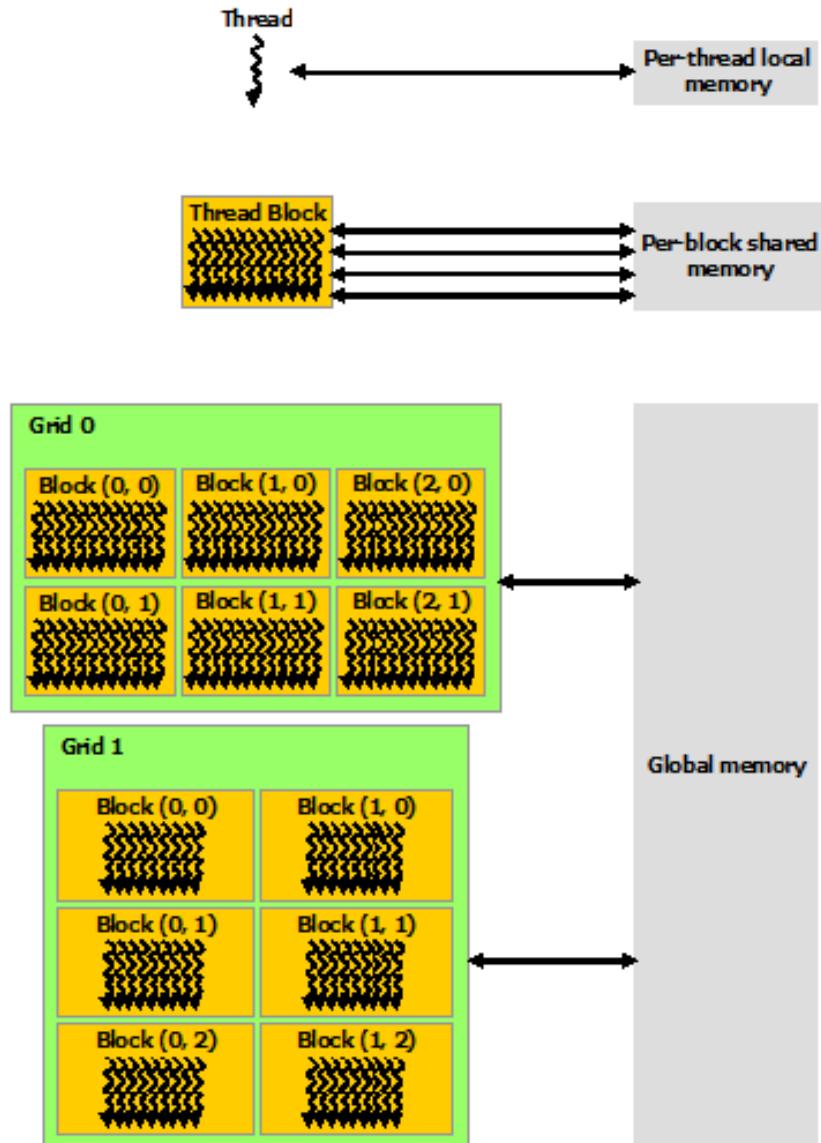

A forma como as diferentes *threads* usam recursos de memória do *device* é chamada de Hierarquia de Memória. Conforme demonstrado pela figura 10, memória local só pode ser acessada pela *thread* em que foi criada, *shared memory* só pode ser acessada por *threads* que pertençam a um mesmo *thread block* e *global memory* pode ser acessada por todas as *threads* (NVIDIA, 2020).

A função `cudaMalloc` é usada no *host* para alocar *global memory* dinamicamente na DRAM do *device*, enquanto a função `cudaMemcpy` copia dados do *host* para o *device* e vice versa. Por outro lado a memória local e a *shared memory* são declaradas nos *kernels* (NVIDIA, 2020), conforme se segue.

```

1  __global__ void kernel (definição das entradas){

2

3      ...

4

5      // Posição da thread nas dimensões x, y e z

6      int x = blockDim.x * blockIdx.x + threadIdx.x;    // memória local

7      int y = blockDim.y * blockIdx.y + threadIdx.y;    // memória local

8      int z = blockDim.z * blockIdx.z + threadIdx.z;    // memória local

9

10

11     ...

12 }

13

14 void main(){

15

16     ...

17

18     float* h_mem;                                // host memory

19

20     ...

21

22     float* d_mem;                                // global memory

23

24 }

```

É considerada uma boa prática diferenciar memória exclusiva do *host* (CPU) da *global memory* (GPU), pois elas só podem ser acessadas pelos dispositivos ao qual pertencem. Um padrão frequentemente adotado é utilizar o prefixo "d\_" no nome de variáveis que armazenam *global memory* e o prefixo "h\_" nas variáveis exclusivas do *host* (NVIDIA, 2020).

Figura 10: Hierarquia de memória.

Fonte: NVIDIA (2020).

A quantidade de bytes de *shared memory* a serem alocados é o terceiro argumento entre `<<< ... >>>` mencionado anteriormente. A vantagem em se utilizar *shared memory* e memória local em relação a *global memory* é que as primeiras são armazenadas em registradores que já se encontram nos SMs e por isso os dados percorrem um trajeto menor até as *threads*, aumentando a velocidade dos acessos (NVIDIA, 2020).

Existem também outras formas de se manejar acessos a memória, que são utilizando *constant memory*, *pinned memory* ou *texture memory*. A *constant memory* é armazenada diretamente no *device*, mas diferentemente da *shared memory* ela é acessível a todas as *threads*. Por outro lado ela possui uma série de desvantagens, dentre elas a impossibilidade de ser alocada dinamicamente e possuir uma capacidade de armazenamento significativamente baixa, 64KB apenas. Além disso o acesso a *constant memory* é limitado, se muitas *threads*

tentarem acessar endereços de *constant memory* diferentes ao mesmo tempo, sua utilização fica prejudicada e o processo pode ficar mais lento do que seria com a *global memory* (NVIDIA, 2020).

Figura 11: Localização dos diferentes tipos de memória.

Fonte: NVIDIA (2020).

De fato a *constant memory* é um recurso útil em situações bem específicas apenas. O comando para alocar esse tipo de memória é feito no *host* utilizando o especificador "`__constant__`" e os dados endereçados nesse espaço de memória colocados lá são copiados de algum endereço de memória da *host* por meio da função `cudaMemcpyToSymbol` (NVIDIA, 2020), conforme se segue.

```

1 ...

2 __constant__ float c_mem[512];           // constant memory

3 ...

4 void main() {

5 ...

6   float* h_mem;                  // host memory

7 ...

8   // copia n bytes de h_mem para c_mem

9   cudaMemcpyToSymbol(c_mem, h_mem, n);

10 ...

11 }

```

Os *Texture objects* são geralmente uma alternativa mais viável. Criados para referenciar e manejar o acesso a *texture memory*, eles são criados a partir de *cuda arrays* e estruturas de dados que contêm uma série de características a seu respeito. O *cuda arrays* por sua vez são vetores 1D, 2D ou 3D optimizados para o acesso a *texture memory* e também são criados com base em descritivos contidos em uma estrutura de dados (NVIDIA, 2020). Para maiores detalhes sobre ambas as estruturas é recomendável consultar a documentação

do *toolkit* no site da NVIDIA (2020), mas um breve exemplo de como utilizar *texture object* é apresentado abaixo:

```

1 __global__ void kernel (cudaTextureObject_t tex){ ... }

2

3 void main () {

4     ...

5     //Estrutura de dados que especifica o tipo de variável

6     // a ser armazenado pelo cuda array , float no caso

7     cudaChannelFormatDesc channelDesc =

8             cudaCreateChannelDesc<float>();

9     //Declaração e alocação de memória do cuda Array

10    cudaArray *d_cudaArray;

11    cudaMalloc3DArray(&d_cudaArray , &channelDesc ,

12                      make_cudaExtent(bytes) , 0);

13    //Estrutura de dados que Array

14    cudaMemcpy3DParms copyParams = { 0 };

15    cudaMemcpy3D(&copyParams);

16

17    //Estruturas de dados que descrevem o texture object

18    cudaResourceDesc     texRes;

19    cudaTextureDesc      texDescr;

20

21    // Efetivamente criando o texture object

22    cudaTextureObject_t tex;

23    cudaCreateTextureObject(&tex , &texRes , &texDescr , NULL);

24    ...

25 }

```

Armazenada diretamente no *device*, a *texture memory* não só é projetada para permitir múltiplos acessos simultâneos a um mesmo endereço de memória de forma eficiente, como também é organizada de forma a optimizar esses acessos a endereços adjacentes. Para acessar endereços de *texture memory* é necessário utilizar as funções tex1D, tex2D ou tex3D, a depender do número de dimensões do *texture object*. A forma como tais funções fazem os acessos pode ser configuradas para acessos a endereços precisos ou até mesmo aproximar e interpolar resultados (NVIDIA, 2020).

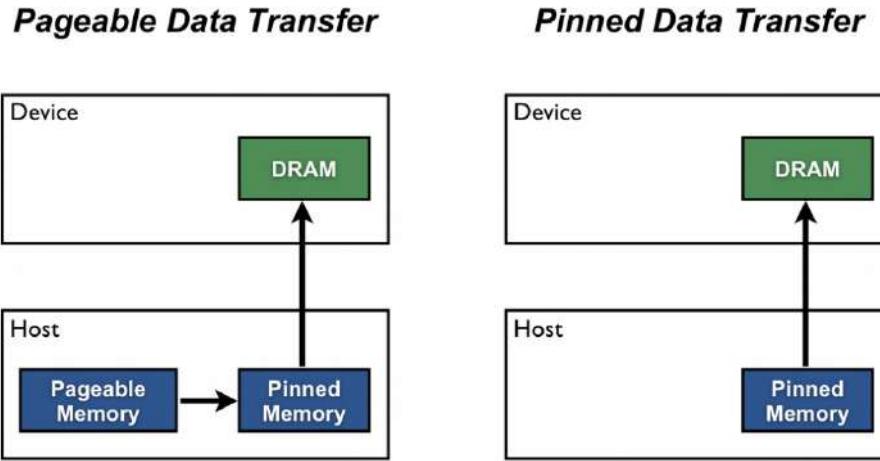

A *pinned memory* por sua vez é um tipo de memória pertencente ao *host*, mas que possui um diferencial importante em relação a *pageable memory*, que é o tipo de memória padrão. Como a figura 12 ilustra, o *device* não pode diretamente acessar *pageable memory*, por isso todas as transferências dados entre dispositivos são feitas por intermédio de *pinned memory* (NVIDIA, 2020).

Figura 12: Funcionamento da *pinned memory*.

Fonte: NVIDIA (2020).

```

1 void main() {

2     ...

3     // pinned memory

4     float *h_pinned;

5     ...

6

7     // aloca n bytes de pinned memory em h_pinned

8     cudaMallocHost((void**)&h_Pinned, n) ;

9

10    // copia n bytes de h_Pageable para h_Pinned

11    memcpy(h_Pinned, h_Pageable, n, cudaMemcpyHostToHost);

12    ...

13 }

```

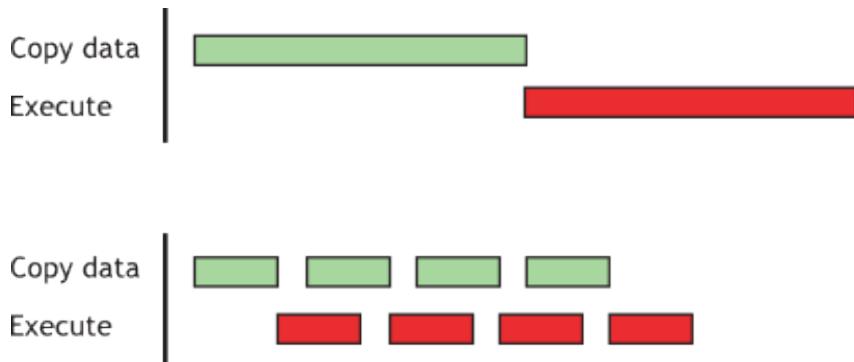

Dados armazenados em *pinned memory* tendem a permanecer lá apenas durante as transferências, mas gravar informação diretamente em *pinned memory* tem suas vantagens, mas para isso devem ser criados *streams* extras. *Streams* são como *devices* virtuais que partilham o trabalho de um *device* físico, mas cada *stream* tem seu próprio fluxo de trabalho e atua independentemente das demais, ou seja, um mesmo *device* pode não só sobrepor tarefas de um mesmo tipo, mas também executar atividades completamente distintas concomitantemente (NVIDIA, 2020).

Quando nada é especificado todas as operações são executadas na *stream* nula, que atua de modo síncrono, sempre esperando a última tarefa ser concluída antes de iniciar a próxima. As *streams* criadas por outro lado operam de forma assíncrona, isso significa que enquanto uma *stream* transfere dados do *host* para o *device*, outra pode executar um *kernel*, optimizando o processo, conforme representado na figura 13 (NVIDIA, 2020). O trecho de código abaixo exemplifica o uso de 8 *streams* para sobrepor tarefas.

```

1 int main()

2 {

3     ...

4     const int num_streams = 8;

5     cudaStream_t streams[nStreams]; // Declara 8 streams

6

7     for (int i = 0; i < nStreams; i++) {

8         cudaStreamCreate(&streams[i]); // Cria uma stream

9         int offset = i * n / nStreams;

10

11        // Transferência assíncrona de memória

12        cudaMemcpyAsync(&d_mem[offset], &h_pinned[offset],

13                        (n / nStreams + 1) * sizeof(float),

14                        cudaMemcpyHostToDevice, stream[i])

15

16        kernel<<<block, thread, shared, streams[i]>>>(entradas);

17

18        cudaStreamDestroy(stream[i]); // Destroi uma stream

19    }

20    ...

21 }

```

Figura 13: Sobreposição de tarefas com o uso de *streams*.

Fonte: NVIDIA (2020).

Devido a natureza caótica do uso de *streams* assíncronas existem as chamadas barreiras, que são primitivas de sincronização, para garantir que as *streams* tenham terminado suas tarefas quando necessário. Quando uma *stream* termina suas tarefas e atinge uma barreira, ela permanece ociosa até que as outras *streams* também atinjam a mesma barreira, sem poder continuar (NVIDIA, 2020).

Apesar de todas as *threads* serem independentes entre si nem todas são executadas exatamente ao mesmo tempo, sendo executadas de forma ligeiramente deslocadas no

tempo, o que em algumas situações pode ser um problema. Para contornar esse problema existem também barreiras de sincronização que atuam apenas em *threads* de um mesmo *kernel*, bem como as *atomic functions* (NVIDIA, 2020).

As barreiras costumam ser suficientes quando todas as *threads* escrevem em endereços de memória diferentes, mesmo que uma *thread* modifique um endereço lido por outra, isso porque todas as leituras de memória podem ser efetuadas antes da escrita (NVIDIA, 2020), conforme abaixo.

```

1 __global__ void kernel ( float* array )

2 {

3     int x = blockDim.x * blockIdx.x + threadIdx.x ;

4     float tmp = array [x] ;

5     __syncthreads () ;      // barreira

6     array [x+1] = tmp ;

7     ...

8 }

```

Por outro lado quando muitas *threads* modificam um mesmo endereço de memória pode-se usar *atomic functions*. Esse tipo especial de função é projetado especificamente para efetuar cálculos de um mesmo tipo envolvendo muitas variáveis, como num somatório por exemplo, conforme pode ser visto abaixo (NVIDIA, 2020).

```

1 __global__ void somatorio ( float* array , float sum )

2 {

3     int x = blockDim.x * blockIdx.x + threadIdx.x ;

4     atomicAdd(&sum , array [x]) ;

5 }

```

Apesar de serem muito úteis nas situações para as quais foram projetadas, as *atomic functions* possuem uma baixa variedade de operações que podem ser feitas, além de limitarem a velocidade dos *kernels* por terem que sincronizar acessos de memória e por esse motivo devem ser usadas apenas quando necessário (NVIDIA, 2020).

Existem ainda muitas outras ferramentas disponibilizadas pelo CUDA *toolkit* que não foram abordadas aqui pois não serão abordadas neste trabalho. Um maior detalhamento sobre as ferramentas apresentadas aqui, bem como outras funcionalidades, pode ser encontrado na documentação do CUDA *toolkit* através do url: <https://docs.nvidia.com/cuda/>.

## 2.4 Reconstrução de Imagens para Tomossíntese Digital Mamária

Câncer é a denominação dada a um conjunto de doenças cuja principal característica é o aumento descontrolado do número de células no tecido que a enfermidade ataca, podendo inclusive criar tumores e se espalhar para outras regiões do corpo. Dentre os diversos tipos existentes, o câncer de mama foi aquele com a maior taxa de mortalidade entre mulheres no ano de 2017 no Brasil e estima-se que até o final de 2020 serão diagnosticados mais de 66 mil casos da doença (INCA, 2020).

A detecção do câncer de mama em sua etapa inicial possibilita que sejam feitos tratamentos menos invasivos e aumenta a taxa de recuperação dos pacientes, por isso seu diagnóstico é tão importante e é recomendado que mulheres entre 50 e 69 anos façam exames de rastreamento a cada dois anos, mesmo na ausência de sintomas (INCA, 2020).

O exame mais conhecido que atende a essa finalidade é a mamografia, que consiste da obtenção de uma simples imagem radiográfica da mama, e como toda imagem radiográfica, possui limitações. Uma radiografia é a representação bidimensional de uma estrutura tridimensional, e isso por si só implica em perda de informação, tornando possível que estruturas se sobreponhamumas as outras e impossibilite um diagnóstico preciso (Vedantham S. and et al, 2015; ASC, 2020).

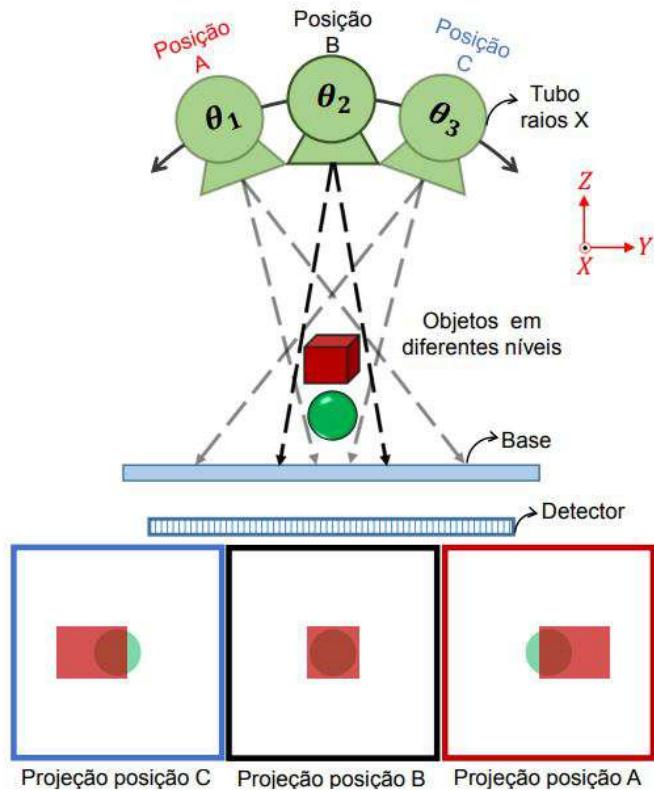

Figura 14: Aquisição das projeções por um equipamento de tomossíntese.

Fonte: Vimieiro, Rodrigo de Barros (2019).

Para contornar esse problema foi desenvolvida a tomossíntese digital mamária, uma técnica que visa reconstruir o volume 3D do objeto de análise a partir da captura de múltiplas imagens radiográficas (projeções). Para obter as imagens necessárias ao algoritmo de reconstrução o tubo emissor de raios X varia levemente sua posição em relação ao objeto seguindo a trajetória de um arco, capturando várias projeções 2D do objeto tridimensional em diferentes pontos dessa trajetória (Vimieiro R. B. et al., 2019).

Como pode-se observar na figura 14, o objeto verde foi completamente obstruído pelo objeto vermelho na projeção "B", mas é parcialmente visível nas projeções "A" e "C" devido a variação angular do emissor de raios X. Depois de adquiridas as projeções é possível aplicá-las em um algoritmo de reconstrução capaz de inferir a geometria dos objetos capturados (Vimieiro, Rodrigo de Barros, 2019).

O Laboratório de Visão Computacional (LAVI), da Escola de Engenharia de São Carlos, Universidade de São Paulo, desenvolveu uma *toolbox* de reconstrução de imagens para tomossíntese digital mamária utilizando a linguagem do MATLAB, *toolbox* essa que pode executar todas as etapas compreendidas por um exame de tomossíntese digital mamária, sendo capaz até mesmo de efetuar a aquisição de projeções ao utilizar um *phantom* virtual já composto por diversas fatias como objeto de estudo. Além disso a *toolbox* também permite alterar a geometria do sistema para corresponder a qualquer equipamento de tomossíntese no mercado, assim como selecionar o método a ser utilizado para a reconstrução.

A *toolbox* está disponível no GitHub do LAVI pelo url: <https://github.com/LAVI-USP/DBT-Reconstruction> e seu processo de desenvolvimento, bem como os testes efetuados para sua validação, podem ser encontrados em detalhes nos trabalhos de Vimieiro et al. (2019) e Vimieiro, Rodrigo de Barros (2019).

Como o presente trabalho se desenvolve a partir da aplicação de uma das funcionalidades da *toolbox*, mais especificamente o algoritmo que cria as projeções, é importante estudar algumas de suas características mais atentamente.

#### 2.4.1 Geometria do Equipamento

A *toolbox* consegue se adaptar a geometria de qualquer equipamento de tomossíntese mamária, sendo ele um equipamento já consolidado no mercado ou não, e isso se deve a uma simples estrutura de dados que contem todas as características de um equipamento de tomossíntese, inclusive características do processo de funcionamento, como por exemplo o número de projeções adquiridas e o número de fatias que o objeto reconstruído deve possuir.

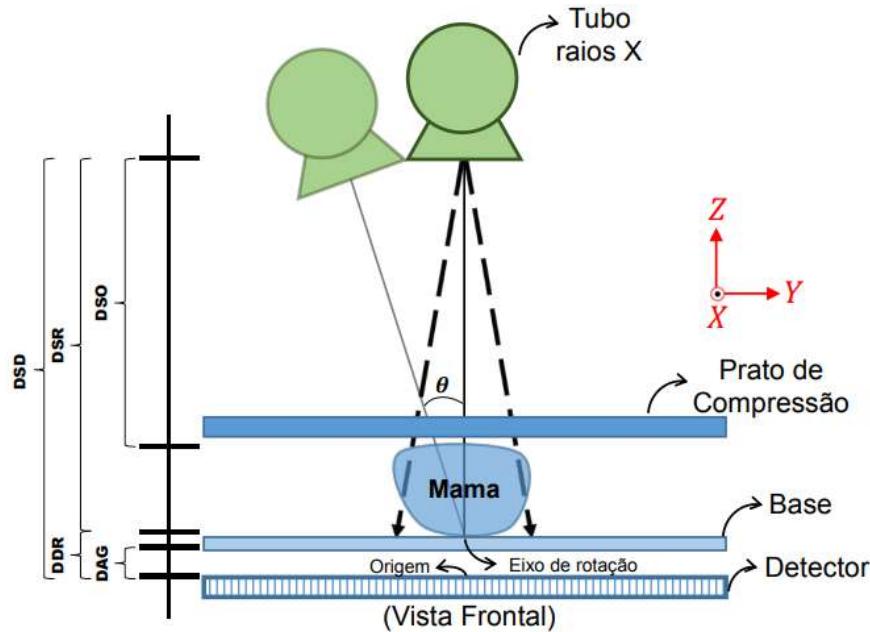

Figura 15: Geometria de um equipamento de tomossíntese digital mamária.

Fonte: Vimieiro R. B. et al. (2019).

A figura 15 ilustra simplificadamente como é a geometria de um equipamento utilizado em um exame de tomossíntese digital mamária, enquanto a tabela 1 comprehende os principais parâmetros contidos na estrutura de dados que descreve o sistema.

Tabela 1: Principais parâmetros que descrevem o sistema.

| Parâmetro                | Significado                                                            |

|--------------------------|------------------------------------------------------------------------|

| <code>nx</code>          | Número de voxels no eixo X (colunas)                                   |

| <code>ny</code>          | Número de voxels no eixo Y (linhas)                                    |

| <code>nz</code>          | Número de fatias                                                       |

| <code>nu</code>          | Número de detectores no eixo X (colunas)                               |

| <code>nv</code>          | Número de detectores no eixo Y (linhas)                                |

| <code>dx</code>          | Tamanho real de um único voxel no eixo X (mm)                          |

| <code>dy</code>          | Tamanho real de um único voxel no eixo Y (mm)                          |

| <code>dz</code>          | Tamanho real de um único voxel no eixo Z (mm)                          |

| <code>du</code>          | Tamanho real de um único detector no eixo X (mm)                       |

| <code>dv</code>          | Tamanho real de um único detector no eixo Y (mm)                       |

| <code>DSD</code>         | Distância do emissor de raios X até o plano do detector (mm)           |

| <code>DSO</code>         | Distância do emissor de raios X até o topo do objeto (mm)              |

| <code>DDR</code>         | Distância do detector até o eixo de rotação do emissor de raios X (mm) |

| <code>DSR</code>         | Distância do emissor de raios X até seu eixo de rotação (mm)           |

| <code>DAG</code>         | Espaço entre o detector e a mesa que apoia o objeto (mm)               |

| <code>nProj</code>       | Número de projeções                                                    |

| <code>tubeAngle</code>   | Variação angular total do emissor de raios X (graus)                   |

| <code>tubeDeg</code>     | Angulação do emissor de raios X em cada projeção (graus)               |

| <code>detAngle</code>    | Variação angular total do detector (graus)                             |

| <code>detectorDeg</code> | Angulação do detector em cada projeção (graus)                         |

Fonte: adaptada de Vimieiro, Rodrigo de Barros (2019).

### 2.4.2 Algoritmos

Outra característica importante da *toolbox* é o conjunto de algoritmos que o compõem, em especial os algoritmos de projeção e retroprojeção. Um operador de projeção geométrico, de maneira geral, é aquele que representa um objeto de N dimensões em um espaço de N - 1 dimensões, no caso o algoritmo utilizado projeta um objeto 3D no plano bidimensional de um detector, conforme a figura 14. A retroprojeção por sua vez faz o oposto da projeção, buscando reconstruir o objeto original, fatia por fatia, com base em suas projeções (Vimieiro, Rodrigo de Barros, 2019).

O método mais simples de reconstrução é aquele que simplesmente utiliza do algoritmo de projeção seguido do algoritmo de retroprojeção, sem se preocupar com o ruído gerado nesse processo, mas existem variantes desse método que buscam aprimorá-lo, gerando resultados mais precisos e confiáveis, alguns dos quais também estão disponíveis para uso na *toolbox*. Os métodos de reconstrução iterativos tem se mostrado promissores, mas demandam elevado custo computacional, pois executam projeção e retroprojeção repetidas vezes em busca da convergência dos resultados (Vimieiro, Rodrigo de Barros, 2019), o que os tornam perfeitos candidatos para optimizar com a utilização de CUDA.

O presente trabalho, porém, não aborda a retroprojeção, visto que seu objetivo é meramente investigativo e não almeja necessariamente resultados, mas sim estudar as ferramentas de que o *toolkit* da NVIDIA dispõe. Por esse motivo apenas o algoritmo de projeção será estudado mais a fundo, uma vez que é a mais simples das opções. Após fazer os devidos testes e descobrir quais abordagens funcionam e quais não funcionam, fica aqui, para quem interessar, a sugestão de aplicar esse aprendizado para acelerar a execução do método iterativo de reconstrução.

---

#### **Algoritmo 1:** Projeção

---

**Entrada:** Volume3D, Parâmetros

**Saída:** Projeções

**Início**

```

para cada Projeção ∈ Projeções faça

θ ← Ângulo da Projeção;

para cada Fatia ∈ Volume3D faça

Calcular  $Y_i$  e  $X_i \forall (y, x) \in$  Projeção ;

Calcular i e j  $\forall (Y_i, X_i)$ ;

Projeção ← Projeção + Interpolação( Fatia, (i, j) );

fim

fim

Fim

```

---

O pseudocódigo acima ilustra como é feito o processo de aquisição das projeções por parte da *toolbox*, para cada posição assumida pelo emissor de raios X, o algoritmo percorre todas as fatias do objeto tridimensional (Volume3D) aplicando o método *Pixel Driven* (Vimieiro, Rodrigo de Barros, 2019).

Esse método por sua vez calcula as coordenadas  $(Y_i, X_i)$  que as projeções 2D de cada fatia ocupam no detector e varre todos os *voxels* dessas fatias projetando seu centro no detector com o uso das equações 2.1 e 2.2 (Vimieiro R. B. et al., 2019). Ambos os equacionamentos podem ser deduzidos a partir de simples semelhança de triângulo com base no sistema apresentado na figura 15.

$$Y_i(\theta, Y, Z) = Y + \frac{Z(DSR.\text{sen}(\theta) + Y)}{DSR.\text{cos}(\theta) + DDR - Z} \quad (2.1)$$

$$X_i(\theta, X, Z) = \frac{X(DSR.\text{cos}(\theta) + DDR)}{DSR.\text{cos}(\theta) + DDR - Z} \quad (2.2)$$

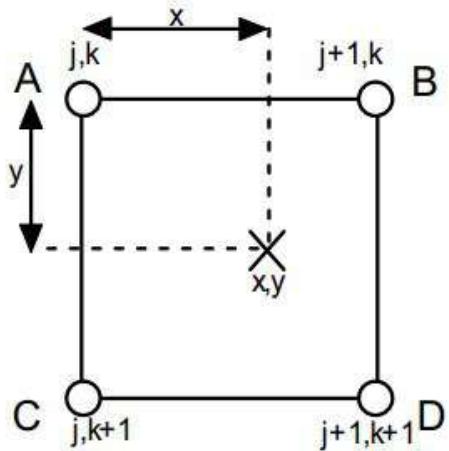

As equações 2.3 e 2.4 por sua vez convertem as coordenadas da imagem ( $y0, x0$ ) em *pixels* ( $i, j$ ) para que, por fim, o valor dos *voxels* projetados possam ser repartidos entre os *pixels* correspondentes por meio de interpolação linear.

$$i = \frac{Y_i}{dy} + y0 \quad (2.3)$$

$$j = -\frac{X_i}{dx} + x0 \quad (2.4)$$

### 3 MATERIAIS E MÉTODOS

Esta seção aborda o *software* MATLAB e as ferramentas de *phantoms 3D* utilizadas durante o desenvolvimento do presente trabalho, além de detalhar os procedimentos tomados para sua execução. De modo geral o *hardware* empregado na execução deste trabalho é descrito na tabela 2, bem como as versões de *software* utilizados.

Tabela 2: Componentes de *hardware* e versões de *software* utilizados.

|                     |                       |

|---------------------|-----------------------|

| Processador         | Intel Core i5 - 6600k |

| Placa de vídeo      | GeForce GTX 1060 6GB  |

| Memória RAM         | 16 GB                 |

| Sistema operacional | Windows 7             |

| MATLAB              | R2018a                |

| CUDA toolkit        | 9.0                   |

#### 3.1 *Phantoms 3D*

*Phantoms* são objetos de estudo desenvolvidos especialmente para simular uma estrutura tridimensional ou bidimensional composta por diferentes tecidos da anatomia humana, com o objetivo de permitir estudos consistentes a respeito de novas metodologias para exames sem a necessidade que testes sejam feitos diretamente em pacientes.

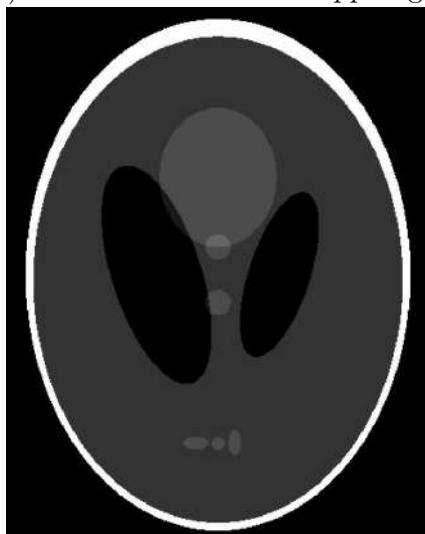

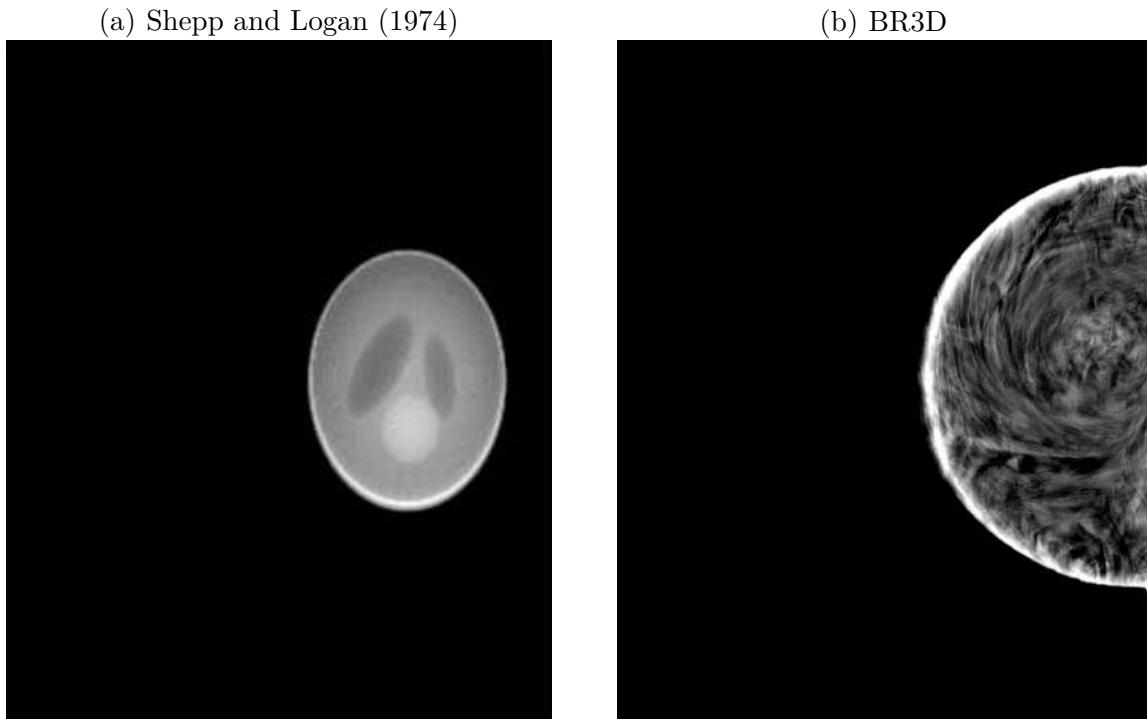

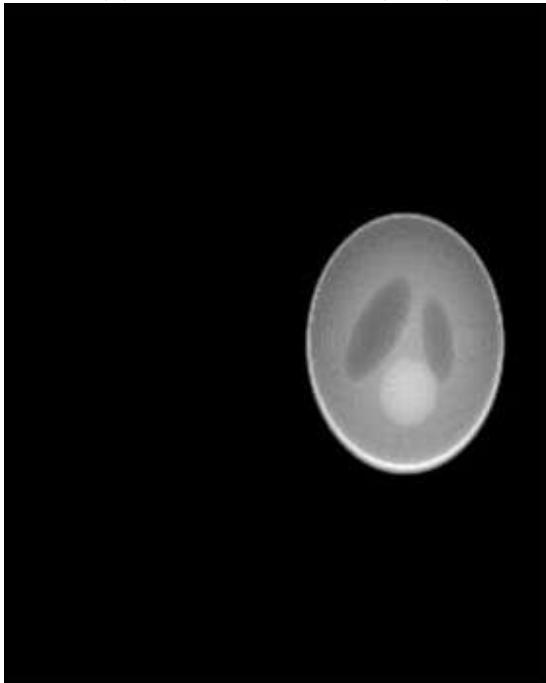

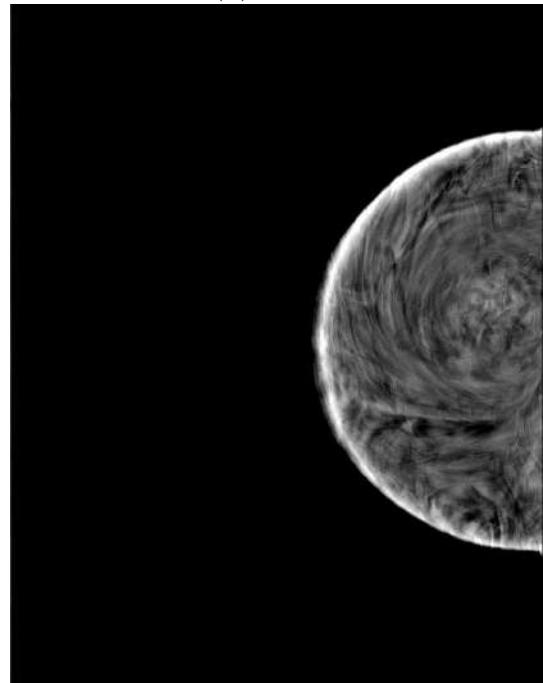

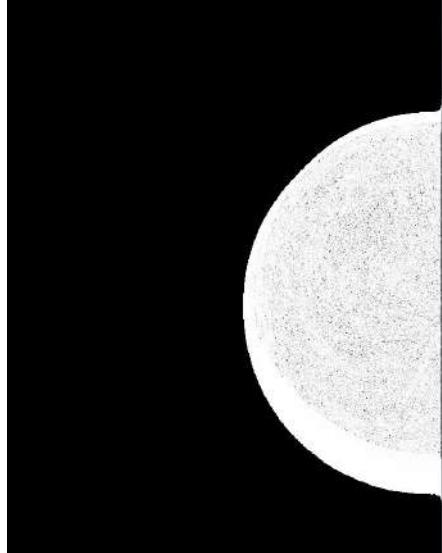

Figura 16: Representação dos *phantoms* utilizados.

(a) *Phantom* virtual de Shepp-Logan

Fonte: Shepp and Logan (1974).

(b) *Phantom* físico BR3D

Fonte: CIRS (2013).

O presente trabalho utilizou em seus testes os mesmos *phantoms 3D* empregados na validação da *toolbox* desenvolvida pelo LAVI. O primeiro é uma versão do *phantom* virtual de Shepp and Logan (1974) adaptada por SCHABEL (2006) para gerar um objeto virtual 3D com a quantidade de fatias que forem necessárias, enquanto o segundo é o *phantom 3D* físico modelo BR3D criado pela CIRS (2013). Por se tratar de um *phantom* físico, o uso do *phantom* BR3D se deu através de fatias já reconstruídas.

Como pode ser visto na tabela 3, que contém as especificações do sistema usado nos testes de cada *phantom*, o *phantom* Shepp-Logan é consideravelmente menor que o BR3D, isso é importante para comparar a eficiência do uso de CUDA em situações que exigem mais e menos processamento.

Tabela 3: Parâmetros que descrevem os sistemas de cada *phantom*.

| Parâmetro | Shepp-Logan | BR3D    |

|-----------|-------------|---------|

| nx        | 128         | 1058    |

| ny        | 128         | 1978    |

| nz        | 128         | 107     |

| nu        | 280         | 2394    |

| nv        | 350         | 3062    |

| dx        | 1mm         | 0,1mm   |

| dy        | 1mm         | 0,1mm   |

| dz        | 10mm        | 0,5mm   |

| du        | 1mm         | 0,1mm   |

| dv        | 1mm         | 0,1mm   |

| DSD       | 6600mm      | 660mm   |

| DSO       | 5100mm      | 580,5mm |

| DDR       | 400mm       | 40mm    |

| DSR       | 6200mm      | 620mm   |

| DAG       | 220mm       | 22mm    |

| nProj     | 9           | 9       |

| tubeAngle | 2, 5°       | 25°     |

| detAngle  | 0°          | 0°      |

Fonte: *toolbox* (Vimieiro, Rodrigo de Barros, 2019).

## 3.2 MATLAB

MATLAB é um *software* voltado a programação baseada em matrizes com uma vasta gama de funcionalidades. Como o desenvolvimento da *toolbox*, cujo algoritmo de projeção é o objeto de estudo aqui, foi feito em MATLAB, é esperado que o presente trabalho também faça uso de MATLAB.

Dentre todas as funcionalidades do MATLAB, as que devem ser destacadas são as que fazem uso do potencial de computação paralela das GPUs. Abaixo segue uma breve explicação sobre as funções usadas neste trabalho, mas uma descrição mais detalhada pode ser encontrada na documentação do MATLAB, no site da MathWorks (2020).

A função "gpuDevice" deve ser a primeira a ser utilizada, pois é responsável por informar ao usuário se o MATLAB reconhece alguma placa de vídeo e, se sim, também disponibiliza suas características, informações essenciais para este trabalho. A tabela 4 contém o resultado gerado por essa função no computador usado no desenvolvimento deste trabalho.

Tabela 4: Resultado da função "gpuDevice".

| Parâmetro              | Descrição                |

|------------------------|--------------------------|

| Name                   | 'GeForce GTX 1060 6GB'   |

| Index                  | 1                        |

| ComputeCapability      | '6.1'                    |

| SupportsDouble         | 1                        |

| DriverVersion          | 11                       |

| ToolkitVersion         | 9                        |

| MaxThreadsPerBlock     | 1024                     |

| MaxShmemPerBlock       | 49152                    |

| MaxThreadBlockSize     | [1024 1024 64]           |

| MaxGridSize            | [2.1475e+09 65535 65535] |

| SIMDWidth              | 32                       |

| TotalMemory            | 6.4425e+09               |

| AvailableMemory        | 5.4431e+09               |

| MultiprocessorCount    | 10                       |

| ClockRateKHz           | 1809500                  |

| ComputeMode            | 'Default'                |

| GPUOverlapsTransfers   | 1                        |

| KernelExecutionTimeout | 1                        |

| CanMapHostMemory       | 1                        |

| DeviceSupported        | 1                        |

| DeviceSelected         | 1                        |

A função "gpuArray" por sua vez cria objetos chamados de *gpuArray*, que são armazenados na memória da GPU em vez da CPU, enquanto a função "gather" faz o processo inverso. Quando o MATLAB usa esse tipo de variável para efetuar certas operações, ele naturalmente as executa na GPU, contanto que tais operações tenham suporte para isso. Porém outra forma de se usar esses objetos é como entrada da função "arrayfun", conforme se segue:

```

1 ...

2 d_input = gpuArray( h_input ); % salva h_input na GPU

3 % executa o arquivo projection.m e salva o resultado em d_output

4 d_output = arrayfun(@projection, d_input);

5 h_output = gather( d_output ); % salva d_output na CPU

6 ...

```

Essa função interpreta um algoritmo escrito em MATLAB, no caso o arquivo "projection.m", e o executa em múltiplas *threads*, uma para cada conjunto de elementos dos vetores de entrada instanciados pelas mesmas coordenadas. Se por exemplo um "arrayfun" receber como entrada a função F e os vetores A e B, então ela executará F(A(1),B(1)) em uma *thread*, F(A(2),B(2)) em outra e assim sucessivamente. Se o número de elementos de A e B forem diferentes a operação não irá funcionar adequadamente. Vale ressaltar que as variáveis de entrada e de saídas dessa função devem ser do tipo *gpuArray*.

Outra funcionalidade do MATLAB é função "mex", cuja finalidade é chamar funções em C, C++ ou Fortran como se fossem funções do próprio MATLAB, contanto que esses arquivos estejam escritos com a sintaxe adequada.

```

1 ...

2 % compila o código projection.cpp

3 mex projection.cpp

4

5 % executa o código projection.cpp

6 output = projection(input);

7 ...

```

A função "mex" compila o arquivo de entrada, no caso "projection.cpp", e cria um arquivo *MEX* de extensão ".mexw64" no diretório de trabalho, o qual é interpretado e executado pelo MATLAB como qualquer outra função. Os arquivos C e C++ destinados a serem usados desta forma devem substituir sua função "main" pela "mexFunction", cuja sintaxe é apresentada abaixo.

```

1 #include "mex.h"

2 void mexFunction(int nlhs , mxArray *plhs [] , int nrhs ,

3                   const mxArray *prhs [])

4 {

5 ...

6 }

```

A função "mexFunction" é inserida pela biblioteca "mex.h" e faz o trabalho de interfacear os argumentos de entrada e saída do arquivo com os providenciados pelo MATLAB. A tabela 5 descreve o significado de cada um de seus argumentos.

Tabela 5: Argumentos de uma "mexFunction".

| Parâmetro | Descrição                                                |

|-----------|----------------------------------------------------------|

| prhs      | Vetor de argumentos de entrada                           |

| plhs      | Vetor de argumentos de saída                             |

| nrhs      | Número de argumentos ou de elementos do vetor de entrada |

| nlhs      | Número de argumentos ou de elementos do vetor de saída   |

Fonte: adaptada de MathWorks (2020).

A função "mex" de fato funciona muito bem nos tipos de arquivos para os quais foi projetada, mas a extensão utilizada pelo *CUDA toolkit* é ".cu", mesmo que a linguagem de programação empregada seja C ou C++. Para contornar esse problema foi desenvolvida a função "mexcuda", que tem suporte para CUDA. A sintaxe da função "mexcuda" no MATLAB é a mesma que da "mex", mas difere no arquivo a ser compilado, como se segue:

```

1 ...

2 #include "mex.h"

3 #include "gpu/mxGPUArray.h"

4 void mexFunction( int nlhs , mxArray *plhs [] , int nrhs ,

5                   const mxArray *prhs [] )

6 {

7     // Inicializa a API de GPU do MATLAB

8     mxInitGPU();

9 ...

10 }

```

Para usar a função "mexcuda", contudo, é necessário garantir que o MATLAB tenha acesso às bibliotecas do *CUDA toolkit*, cuja versão deve ser compatível com a do MATLAB, de acordo com a tabela fornecida em sua documentação (MathWorks, 2020), mas que também pode ser acessada diretamente pelo url: <https://www.mathworks.com/help/parallel-computing/gpu-support-by-release.html>.

A linha de código abaixo atribui à variável "MW\_NVCC\_PATH" o diretório do compilador NVCC, garantindo que o MATLAB o reconheça e possa fazer uso do *CUDA toolkit* corretamente.

```

1 ...

2 setenv( 'MW_NVCC_PATH' , 'CUDA_dir\CUDA\v9.0\bin' );

3 ...

```

### 3.3 Metodologia

Este trabalho visa investigar o potencial computacional das GPUs utilizando como objeto de estudo uma *toolbox* desenvolvida em MATLAB, então é natural seguir uma metodologia que também aborde as funcionalidades do MATLAB. A metodologia empregada aqui foi a mesma apresentada na página "Illustrating Three Approaches to GPU Computing: The Mandelbrot Set" da documentação do MATLAB, acessível pelo url: <https://www.mathworks.com/help/parallel-computing/examples/illustrating-three-approaches-to-gpu-computing-the-mandelbrot-set.html>.