THOMAS CEGAL GOUTHIER DE VILHENA

ROGÉRIO HONG HUI CHUNG

SISTEMA RTOOL

FERRAMENTA DE PROTOTIPAGEM RÁPIDA DE DESCRIÇÕES RTL

PARA FINS DE DEPURAÇÃO

São Paulo

2011

THOMAS CEGAL GOUTHIER DE VILHENA

ROGÉRIO HONG HUI CHUNG

SISTEMA RTOOL

FERRAMENTA DE PROTOTIPAGEM RÁPIDA DE DESCRIÇÕES RTL

PARA FINS DE DEPURAÇÃO

Trabalho de formatura apresentado ao

Departamento de Engenharia de

Sistemas Eletrônicos da Escola

Politécnica da USP como parte dos

requisitos necessários à obtenção do

título de Engenheiro.

Área de concentração: Engenharia de

Sistemas Eletrônicos

Orientador: Prof. Wang Jiang Chau

São Paulo

2011

## AGRADECIMENTOS

Ao professor Wang Jiang Chau, pela sugestão do tema do projeto de formatura e pelo seu empenho no auxílio aos autores durante a etapa de desenvolvimento.

Aos familiares, que deram todo o suporte necessário aos autores durante suas trajetórias no curso de graduação, e à todos que colaboraram, direta ou indiretamente, na execução deste projeto.

*Everyone knows that debugging is twice as hard as writing a program in the first place. So if you're as clever as you can be when you write it, how will you ever debug it?*

(Brian Kernighan)

## RESUMO

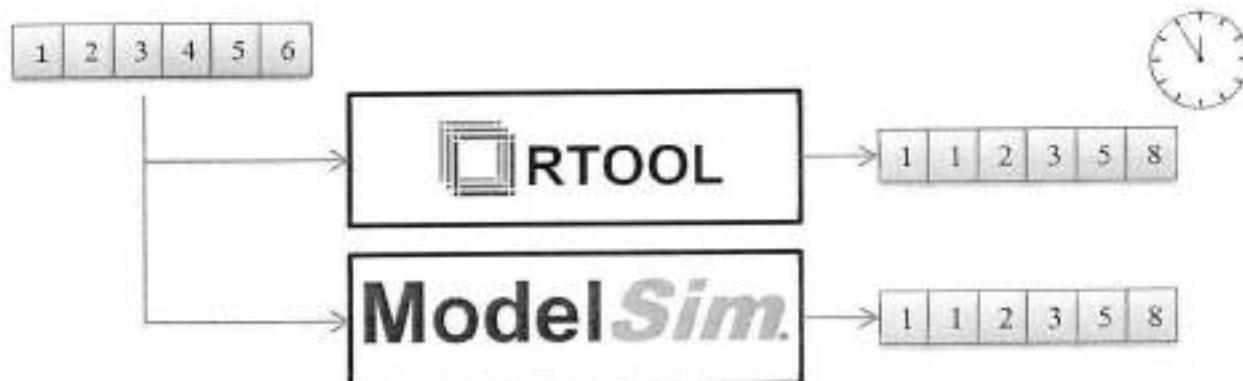

Os autores desenvolveram como projeto de formatura do curso de Engenharia de Sistemas Eletrônicos uma ferramenta de prototipagem rápida de descrições RTL para fins de depuração. Enquanto o desempenho de ferramentas comerciais disponíveis no mercado (ex: ModelSim), baseadas em softwares que rodam em processadores de propósito geral, mostra-se satisfatório para projetos de pequeno porte, sistemas integrados complexos sofrem com seu baixo desempenho. A prototipagem em FPGA para conseguinte emulação de uma descrição RTL, com o objetivo de se efetuar sua verificação funcional, vem sendo utilizada como uma alternativa de melhor desempenho às ferramentas tradicionais. Contudo, observou-se na literatura a maciça utilização de soluções específicas (não reutilizáveis) para a prototipagem de projetos de sistemas integrados, de modo que os autores e o orientador vislumbram um espaço para a solução abrangente desenvolvida, a qual pode vir a ter um caráter comercial.

Palavras-chave: Verificação funcional, Prototipagem, FPGA.

## ABSTRACT

The authors have developed a RTL description prototyping tool for functional verification purposes as their final graduation project in the course of Electronic Systems Engineering. Although the performance of commercially available tools (ex: ModelSim) is satisfactory for small projects, more complex digital systems requirements for performance can't be delivered by these same tools due to the fact that they are software based tools. The FPGA based prototyping and emulation of RTL descriptions for functional verification purposes is a well-known alternative method for designers pursuing higher performance during the verification stage of a digital system project. However, designers usually develop their prototyping environment from scratch in such a way that it becomes a specific solution, i.e., it is only compatible with one project and can't be reused in future projects. So, the authors perceived an opportunity for the development of a wider, non-specific, prototyping tool solution that could be used by several designers in their respective projects.

Key-words: Functional Verification, Prototyping, FPGA.

## LISTA DE FIGURAS

|                                                                                                                                    |    |

|------------------------------------------------------------------------------------------------------------------------------------|----|

| Figura 1. A sintetização do circuito digital a partir da descrição HDL é de responsabilidade do compilador.....                    | 1  |

| Figura 2. Difusão de uma inovação (Rogers, 2003). A: Introdução.<br>B: Crescimento. C: Saturação. D: Declínio.....                 | 3  |

| Figura 3. Modelo geral de testbench proposto por Bergeron, 2003.....                                                               | 5  |

| Figura 4. Camadas do sistema proposto .....                                                                                        | 6  |

| Figura 5. Solução específica proposta por Serrestou, Beroule, Robach, 2007 .                                                       | 7  |

| Figura 6. Foto da placa DE-2 usada no projeto RTOOL.....                                                                           | 9  |

| Figura 7. Diagrama de blocos do sistema de verificação .....                                                                       | 10 |

| Figura 8. EAP do projeto RTOOL.....                                                                                                | 12 |

| Figura 9. Diagrama de blocos do sistema RTOOL. Os blocos em vermelho<br>são responsabilidade do usuário.....                       | 16 |

| Figura 10. Sistema Nios II construído para o projeto RTOOL (Modificado<br>de: Nios II Processor Reference Handbook, pág. 11) ..... | 18 |

| Figura 11. Controlador de memória SDRAM (Fonte: Embedded Peripherals<br>IP User Guide, pág. 24).....                               | 19 |

| Figura 12. Divisão da Memória SDRAM.....                                                                                           | 20 |

| Figura 13. Diagrama de blocos (Fonte: Manual JTAG UART core, pág. 3).....                                                          | 22 |

| Figura 14. Diagrama do contexto no qual o adaptador RTL está inserido.....                                                         | 25 |

| Figura 15. Diagrama de interligação entre o Adaptador RTL e o barramento<br>AVALON.....                                            | 26 |

| Figura 16. Carta de tempos do barramento Avalon (Fonte: Avalon<br>Interface Specification, pág. 22) .....                          | 27 |

| Figura 17. Implementação da AVALON Conduit Interface para o                                                                        |    |

|                                                                                                    |    |

|----------------------------------------------------------------------------------------------------|----|

| Adaptador RTL .....                                                                                | 29 |

| Figura 18. Detalhamento da interligação entre o Adaptador RTL e o dispositivo RTL do usuário ..... | 30 |

| Figura 19. Carta de tempos de uma requisição do DRIVER .....                                       | 31 |

| Figura 20. Carta de tempos de uma requisição do MONITOR .....                                      | 31 |

| Figura 21. Interações entre os processos e a memória SDRAM.....                                    | 32 |

| Figura 22. Diagrama da MEF do software embarcado do sistema RTOOL.....                             | 35 |

| Figura 23. Esquematização do algoritmo de automatização da prototipagem .....                      | 39 |

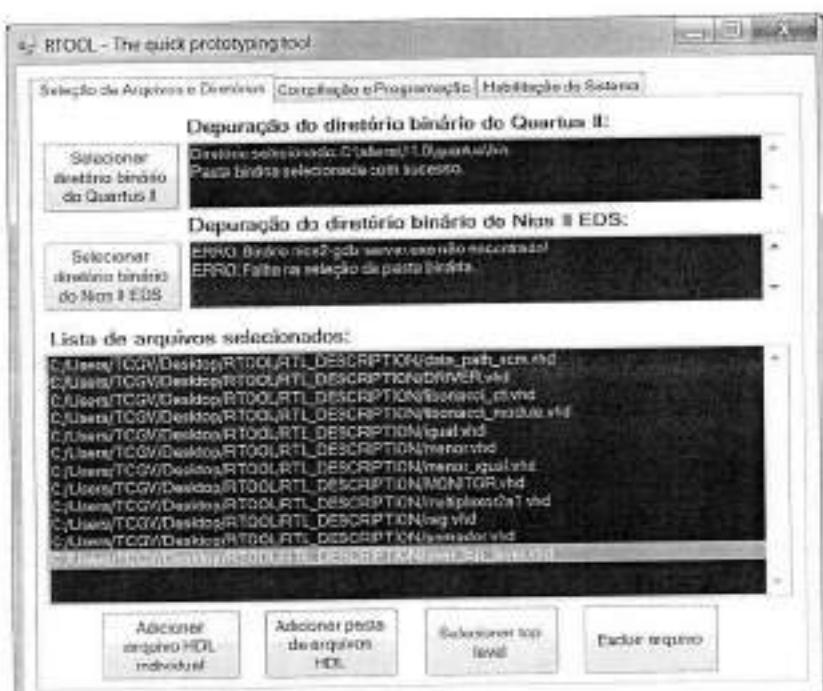

| Figura 24. Primeira aba da GUI com exemplo de mensagem de erro.....                                | 40 |

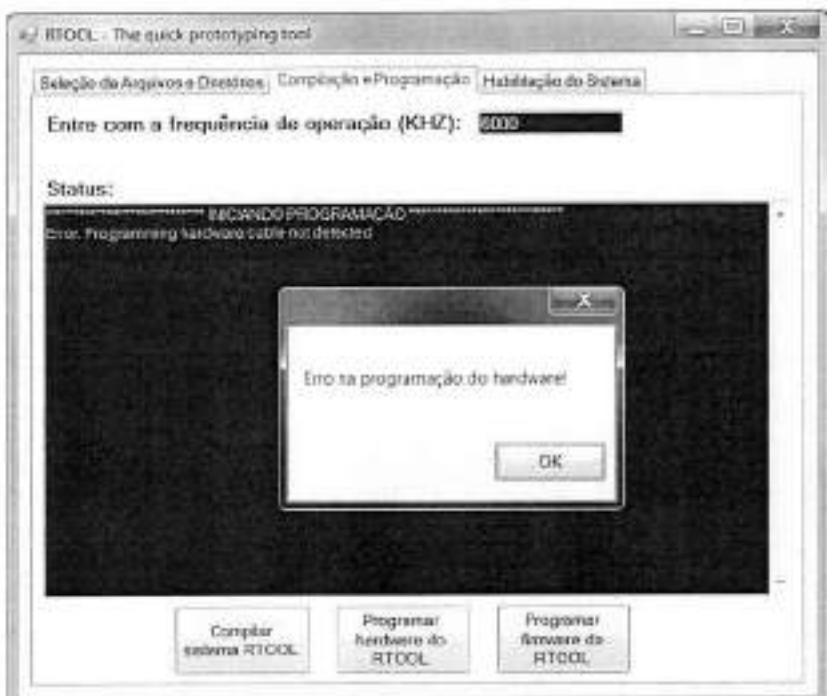

| Figura 25. Segunda aba da GUI com exemplo de mensagem de erro.....                                 | 41 |

| Figura 26. Terceira aba da GUI com exemplo de mensagem de erro.....                                | 41 |

| Figura 27. Camadas da API do sistema RTOOL.....                                                    | 42 |

| Figura 28. Fluxo de utilização da API do sistema RTOOL .....                                       | 45 |

| Figura 29. Diagrama de blocos do Driver USB e suas interações.....                                 | 46 |

| Figura 30. Estrutura do pacote de comunicação .....                                                | 47 |

| Figura 31. Sequência de pacotes para a operação de leitura .....                                   | 50 |

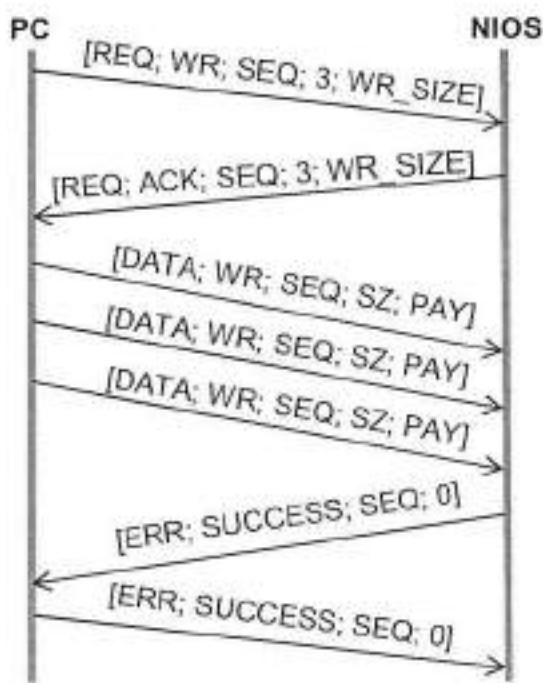

| Figura 32. Sequência de pacotes para a operação de escrita .....                                   | 51 |

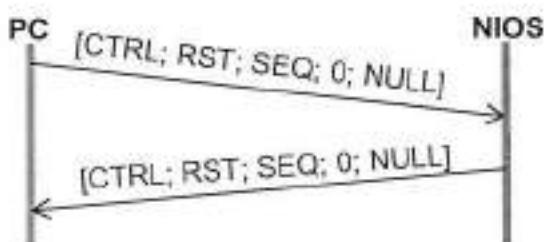

| Figura 33. Sequência de pacotes para a operação de reset .....                                     | 52 |

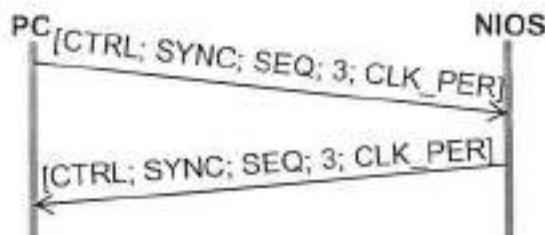

| Figura 34. Sequência de pacotes para a operação de sincronização .....                             | 52 |

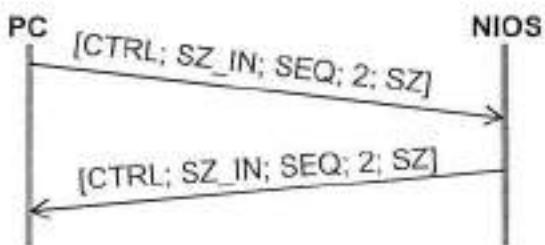

| Figura 35. Sequência de pacotes para a configuração do tamanho da interface de entrada.....        | 53 |

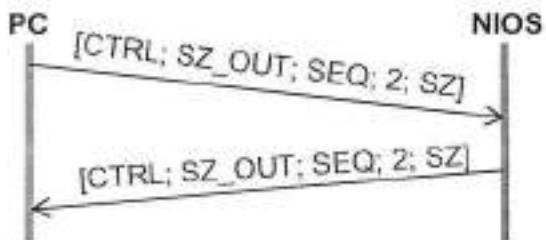

| Figura 36. Sequência de pacotes para a configuração do tamanho da interface de saída .....         | 53 |

|                                                                                                                                                                              |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

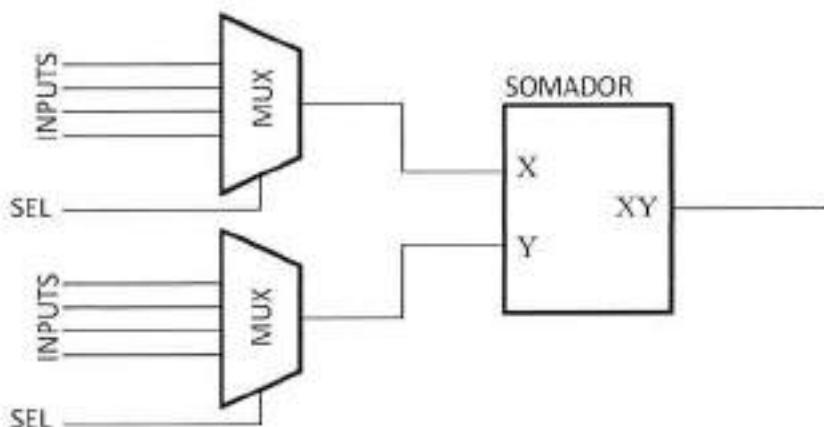

| Figura 37. Diagrama do circuito digital .....                                                                                                                                | 57 |

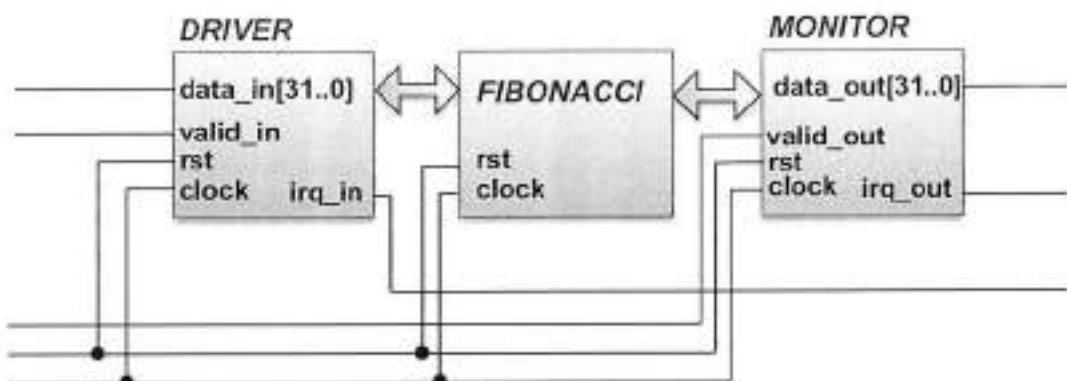

| Figura 38. Módulo Fibonacci acrescido de DRIVER e MONITOR. As interfaces específicas do módulo Fibonacci foram omitidas por não serem relevantes nesta figura .....          | 57 |

| Figura 39. Processo de geração de vetores de entrada e saída .....                                                                                                           | 61 |

| Figura 40. Comparaçāo de desempenho .....                                                                                                                                    | 62 |

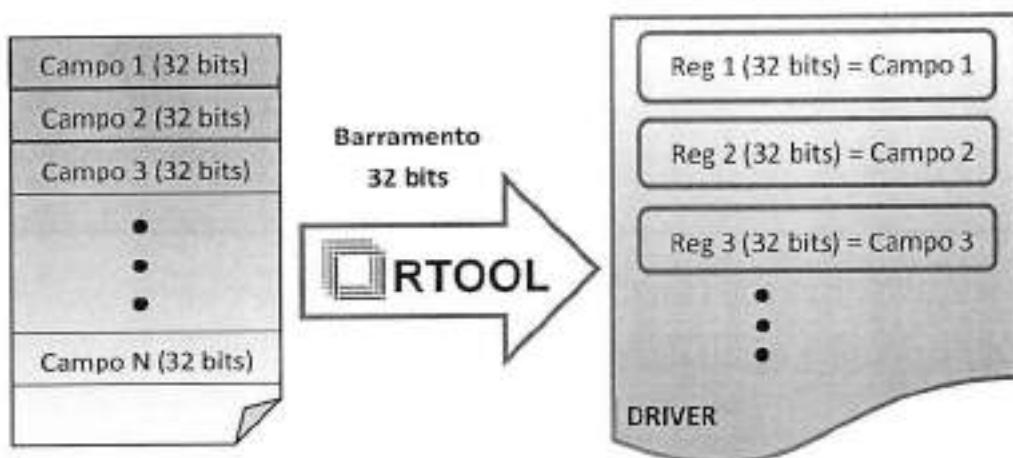

| Figura 41. Esquema que mostra a equivalência entre os campos que compõem as estruturas de alto nível e os registradores presentes no DRIVER .....                            | 65 |

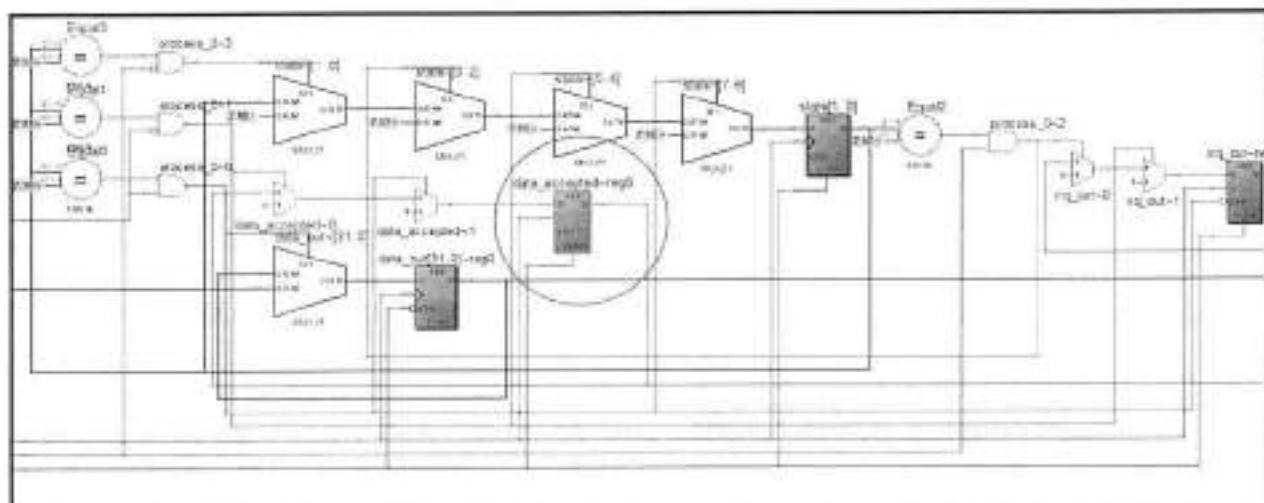

| Figura 42. Através da simulação convencional pode-se analisar todos os sinais e processos internos do hardware, com o intuito de se mapear precisamente a fonte de erro..... | 67 |

## LISTA DE TABELAS

|                                                                                                                               |    |

|-------------------------------------------------------------------------------------------------------------------------------|----|

| Tabela 1. Mapa de registradores (Fonte: Manual JTAG UART core, pág. 12) ...                                                   | 24 |

| Tabela 2. Descrição das interfaces selecionadas para o Adaptador RTL<br>(Fonte: Avalon Interface Specification, pág. 5) ..... | 26 |

| Tabela 3. Tipos de pacotes definidos pelo protocolo.....                                                                      | 47 |

| Tabela 4. Subtipos permitidos para o pacote REQ.....                                                                          | 48 |

| Tabela 5. Subtipos permitidos para o pacote DATA.....                                                                         | 49 |

| Tabela 6. Subtipos permitidos para o pacote CTRL.....                                                                         | 51 |

| Tabela 7. Subtipos permitidos para o pacote ERR.....                                                                          | 54 |

| Tabela 8. Mapeamento com a interface do Adaptador RTL .....                                                                   | 60 |

| Tabela 9. Teste de confiabilidade.....                                                                                        | 61 |

| Tabela 10. Características do PC usado na simulação .....                                                                     | 62 |

| Tabela 11. Comparação de desempenho entre PC e sistema RTOOL.....                                                             | 63 |

## LISTA DE ABREVIATURAS E SIGLAS

|            |                                                                                  |

|------------|----------------------------------------------------------------------------------|

| API .....  | <i>Application Programming Interface</i>                                         |

| CI.....    | Circuito Integrado                                                               |

| DUV.....   | <i>Device Under Verification</i>                                                 |

| EAP.....   | Estrutura Analitica de Projeto                                                   |

| FIFO.....  | <i>First In First Out</i>                                                        |

| FPGA ..... | Field Programmable Gate Array                                                    |

| GPP.....   | <i>General Purpose Processor</i>                                                 |

| GUI.....   | <i>Graphical User Interface</i>                                                  |

| HDL.....   | <i>Hardware Description Language</i>                                             |

| JTAG.....  | <i>Joint Test Action Group</i>                                                   |

| MEF.....   | Máquina de Estados Finitos                                                       |

| RTL .....  | <i>Register Transfer Logic</i>                                                   |

| RTOOL..... | Codinome escolhido para o projeto de formatura                                   |

| SOPC.....  | <i>System On Programmable Chip</i>                                               |

| UART ..... | <i>Universal Asynchronous Receiver/Transmitter</i>                               |

| USB.....   | <i>Universal Serial Bus</i>                                                      |

| UT .....   | <i>Under Test</i>                                                                |

| VHDL.....  | <i>VHSIC (Very High Speed Integrated Circuits) Hardware Description Language</i> |

## SUMÁRIO

|           |                                                         |          |

|-----------|---------------------------------------------------------|----------|

| <b>1.</b> | <b>INTRODUÇÃO .....</b>                                 | <b>1</b> |

| 1.1       | Justificativa.....                                      | 1        |

| 1.2       | Objetivos do projeto .....                              | 3        |

| <b>2.</b> | <b>REVISÃO DA LITERATURA.....</b>                       | <b>5</b> |

| <b>3.</b> | <b>MATERIAIS E MÉTODOS.....</b>                         | <b>9</b> |

| 3.1       | Estrutura analítica de projeto .....                    | 11       |

| 3.1.1     | Detalhamento da EAP.....                                | 12       |

| 3.2       | Implementação do sistema RTOOL.....                     | 15       |

| 3.2.1     | Hardware do SOPC .....                                  | 16       |

| 3.2.1.1   | Subsistema Nios II e memória SDRAM externa.....         | 16       |

| 3.2.1.1.1 | Software de gerenciamento da memória SDRAM.....         | 19       |

| 3.2.1.2   | Módulo de comunicação USB .....                         | 22       |

| 3.2.1.3   | Adaptador RTL.....                                      | 25       |

| 3.2.1.3.1 | Barramento AVALON.....                                  | 25       |

| 3.2.1.3.2 | Funcionalidades do Adaptador RTL.....                   | 28       |

| 3.2.2     | Software do SOPC .....                                  | 32       |

| 3.2.2.1   | Descrição conceitual dos processos.....                 | 32       |

| 3.2.2.2   | Máquina de Estados Finitos.....                         | 33       |

| 3.2.3     | Ferramenta de prototipagem rápida.....                  | 38       |

| 3.2.3.1   | Algoritmo de integração, compilação e programação ..... | 38       |

|                                                            |                                                           |           |

|------------------------------------------------------------|-----------------------------------------------------------|-----------|

| 3.2.3.2                                                    | Interface gráfica de usuário da ferramenta .....          | 40        |

| 3.2.4                                                      | Interface de Programação de Aplicativo .....              | 42        |

| 3.2.4.1                                                    | Biblioteca em linguagem C.....                            | 43        |

| 3.2.4.2                                                    | Driver USB com interface de rede.....                     | 46        |

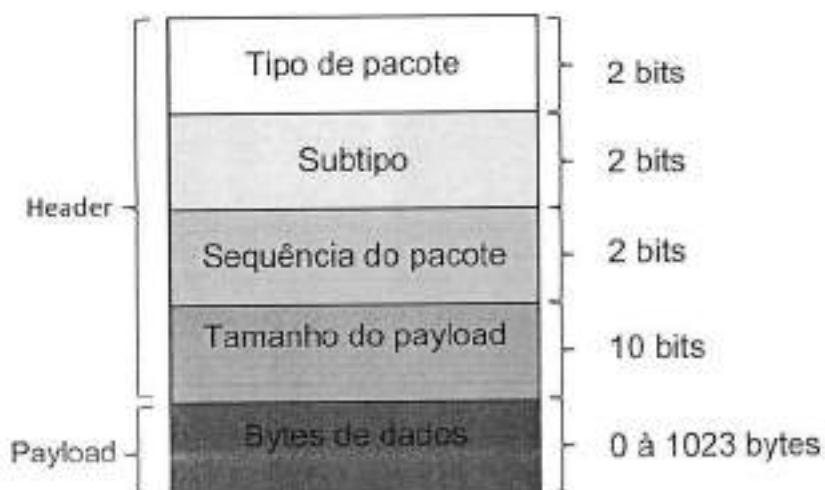

| 3.2.4.3                                                    | Protocolo de comunicação com a placa de prototipagem..... | 47        |

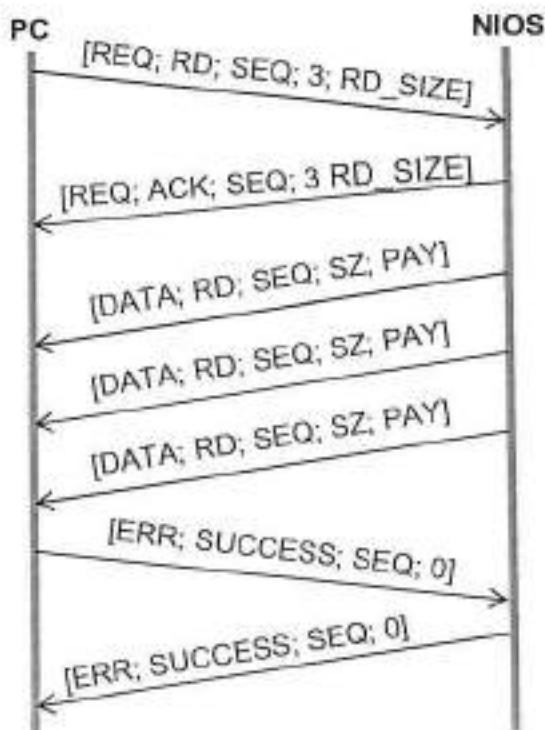

| 3.2.4.3.1                                                  | Transmissão de dados .....                                | 48        |

| 3.2.4.3.2                                                  | Operações de controle.....                                | 51        |

| 3.2.4.3.3                                                  | Detecção e tratamento de erro.....                        | 53        |

| <b>4.</b>                                                  | <b>RESULTADOS.....</b>                                    | <b>55</b> |

| 4.1                                                        | Dispositivo RTL usado nos testes.....                     | 55        |

| 4.2                                                        | Teste de confiabilidade do sistema .....                  | 60        |

| 4.3                                                        | Teste de desempenho da emulação .....                     | 62        |

| <b>5.</b>                                                  | <b>DISCUSSÃO .....</b>                                    | <b>64</b> |

| <b>6.</b>                                                  | <b>CONCLUSÃO .....</b>                                    | <b>67</b> |

| <b>7.</b>                                                  | <b>REFERÊNCIAS.....</b>                                   | <b>70</b> |

| <b>8.</b>                                                  | <b>BIBLIOGRAFIA.....</b>                                  | <b>71</b> |

| <b>APÊNDICE A – CÓDIGO DE TESTE DE CONFIABILIDADE.....</b> |                                                           | <b>72</b> |

| <b>APÊNDICE B – CÓDIGO DE TESTE DE DESEMPENHOS.....</b>    |                                                           | <b>75</b> |

| <b>APÊNDICE C – CÓDIGO DO TESTBENCH DO MODELSIM.....</b>   |                                                           | <b>78</b> |

| <b>APÊNDICE D – MODELO DE DRIVER E MONITOR.....</b>        |                                                           | <b>80</b> |

## 1. INTRODUÇÃO

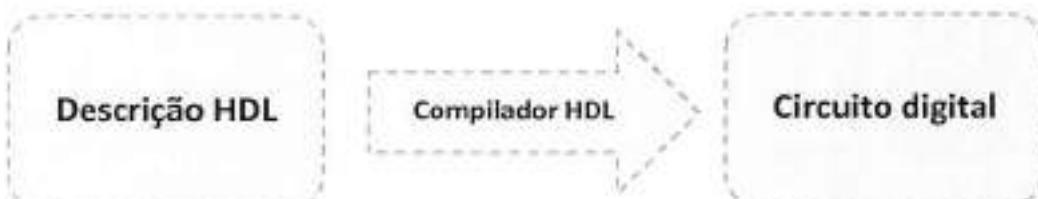

As linguagens de descrição de hardware (VHDL, Verilog, etc) se estabeleceram na indústria de semicondutores como um padrão para o desenvolvimento de circuitos integrados digitais. Sua utilização permite que o projetista descreva de forma relativamente simples e rápida o funcionamento de um circuito digital, deixando a laboriosa tarefa de síntese do circuito digital para o compilador da linguagem utilizada. O processo de síntese é ilustrado na figura 1.

Figura 1. A sintetização do circuito digital a partir da descrição HDL é de responsabilidade do compilador

A facilidade proporcionada pelas linguagens de descrição de hardware (HDL) para o projeto de circuitos digitais permitiu um significativo aumento na complexidade dos projetos a serem desenvolvidos. A etapa de verificação da corretude funcional de uma descrição HDL torna-se, então, fundamental para garantir o sucesso do projeto.

Dado que maioria das soluções existentes para a simulação funcional de uma descrição RTL (*Register Transfer Logic*) em uma certa HDL são baseadas em aplicativos rodando em estações de trabalho, o tempo de simulação torna-se extremamente elevado (Serrestou, Beroullie, Robach, 2007). Em decorrência disso, este projeto propõe o desenvolvimento de um sistema de verificação de descrição RTL mais veloz que seja baseado na prototipagem da descrição RTL em um FPGA (*Field Programmable Gate Array*).

O codinome escolhido para este projeto foi **RTOOL**, uma referência à sigla RTL e à palavra do idioma inglês *tool*, que significa ferramenta.

### 1.1 Justificativa

Os circuitos digitais, por natureza, exibem elevado grau de paralelismo, ou seja, em um dado instante de sua operação diversas tarefas independentes estão ativas. Consequentemente, as HDLs exibem um paralelismo intrínseco em suas sintaxes, tornando-as bastante distintas das linguagens de programação convencionais.

Esta distinção entre as HDLs e as linguagens de programação convencionais resulta no fato de que a simulação de uma descrição RTL em um software simulador é extremamente lenta, justamente pelo fato de que todo o paralelismo inherente às HDLs é incompatível com um processador de propósito geral. Enquanto as HDLs permitem que o programador defina múltiplas operações a serem realizadas simultaneamente, a simulação deste mesmo comportamento em software requer que um GPP execute diversas instruções sequenciais (Tocci, Widmer, 2007).

Mais do que uma questão de compatibilidade, a simulação de descrições RTL é uma importante etapa do ciclo de projeto de um CI (circuito integrado) digital. É nesta etapa que erros desconhecidos são descobertos e corrigidos.

Na dinâmica da economia atual, o tempo tornou-se um recurso extremamente valioso, principalmente nos mercados de tecnologia. Um pequeno atraso de alguns dias, semanas ou meses pode determinar o fracasso de um novo produto, resultando em grandes perdas financeiras para uma empresa.

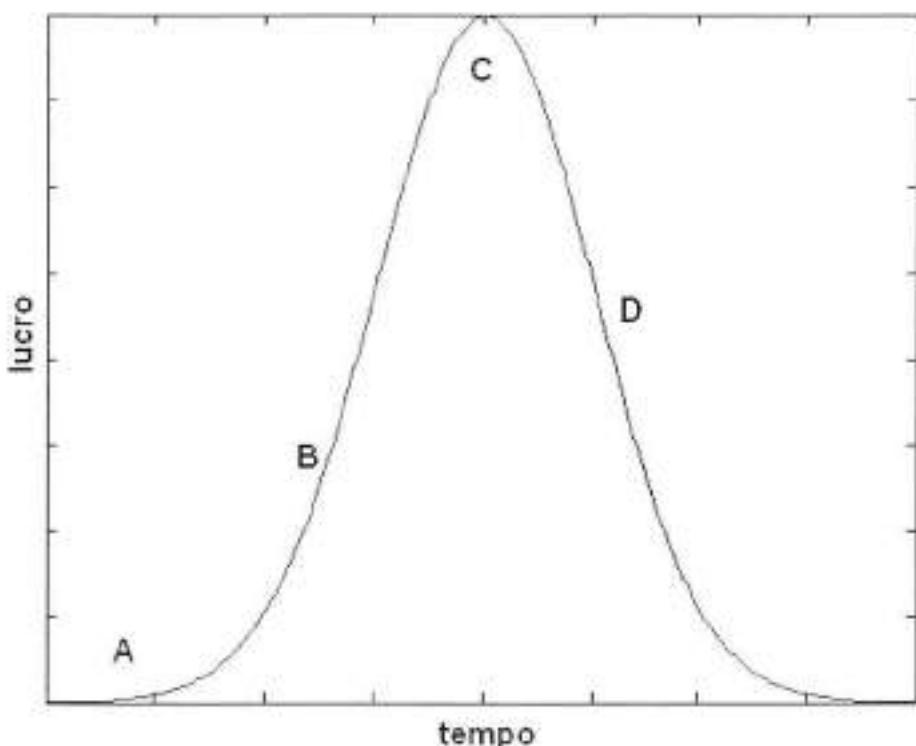

Rogers (Rogers, 2003), em seu estudo sobre a difusão de inovações tecnológicas em seus respectivos mercados, mostra que um produto inovador é inserido no mercado através de uma curva normal, como apresentado na figura 2. Inicialmente poucos consumidores adotam a inovação (A: Introdução). Conforme estes consumidores, através de suas redes de contato, demonstram sua satisfação com o novo produto, mais consumidores passam a adotar e difundir a inovação (B: Crescimento). Eventualmente, a difusão da tecnologia chegará a um patamar no qual cerca da metade dos consumidores já adotou a tecnologia, de modo que o ritmo de difusão irá desacelerar (C: Saturação). Finalmente, com a aproximação da plena adoção da inovação, o ritmo da difusão se aproximará de zero (D: Declínio), já que, no caso de bens duráveis, não ocorre substituição, e praticamente todos os consumidores já adotaram a inovação.

Figura 2. Difusão de uma inovação (Rogers, 2003). A: Introdução. B: Crescimento. C: Saturação. D: Declínio

O caráter inovador deste projeto está na proposição da utilização de um FPGA como o núcleo do sistema de verificação da descrição RTL. A partir da síntese da descrição RTL, sua gravação em um FPGA (juntamente com um sistema digital de suporte e comunicação) e posterior execução controlada, espera-se reduzir drasticamente o tempo gasto na etapa de depuração do projeto de um CI digital, o que significa um menor *time to market* para o produto sendo desenvolvido.

## 1.2 Objetivos do Projeto

Em média, 32% do tempo de projeto de um SOC é gasto em simulação top-level (Wilson research group, 2010). Portanto, espera-se com a ferramenta RTOOL uma considerável redução desta fatia de tempo gasta com a validação do sistema digital integrado.

A meta deste projeto, estimada a partir de resultados observados em Serrestou, Beroulli, Robach, 2007, será uma melhora de desempenho no tempo de verificação da descrição RTL de dez vezes. A metodologia a ser usada para a análise dos resultados será a comparação do desempenho do RTOOL com o software ModelSim, da Mentor Graphics, utilizando-se descrições RTL em linguagem VHDL sintetizável como *benchmarks* (Squillero, Reorda, Corno, 2000).

Dado que o tempo de execução da simulação de uma descrição RTL em uma ferramenta comercial torna-se um empecilho apenas para circuitos complexos, ou seja, circuitos de grande porte com números elevados de portas lógicas e de registradores, a avaliação de desempenho do sistema RTOOL será realizada a partir de *benchmarks* extensas.

Considerando-se o possível viés comercial deste projeto, mais um objetivo pode ser proposto. O sistema RTOOL deve ser de fácil implantação e de fácil utilização, ou seja, o esforço do usuário nas tarefas de integração da sua descrição RTL ao hardware do sistema RTOOL, de compilação do hardware integrado, de programação do FPGA núcleo do sistema e de utilização da API do sistema RTOOL deve ser mínimo.

## 2. REVISÃO DA LITERATURA

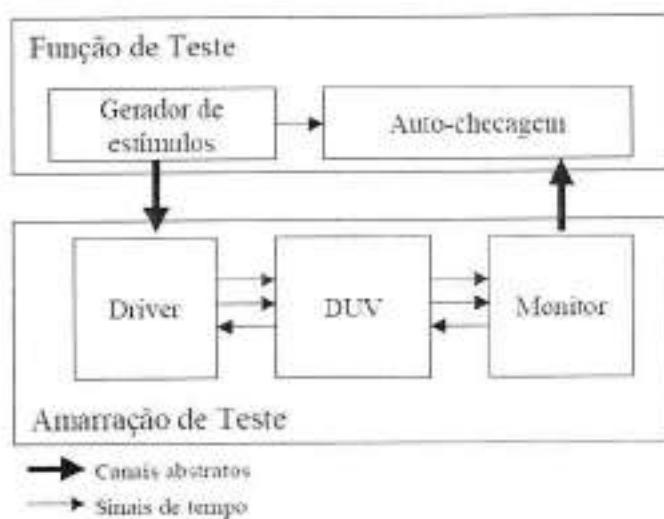

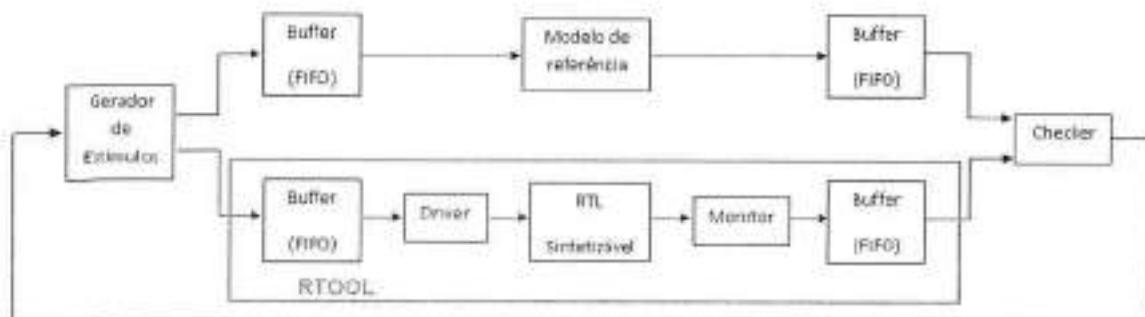

A verificação funcional de uma descrição RTL segue o modelo proposto por Bergeron, 2003, o qual é apresentado na figura 3. Neste modelo, um gerador de estímulos excita as entradas de uma descrição RTL em processo de simulação funcional. Em seguida, os sinais de saída da descrição RTL em simulação são comparados com valores admitidos corretos (calculados previamente). A descrição RTL em análise estará correta se não for detectada nenhuma diferença entre as saídas simuladas e as saídas esperadas para um conjunto abrangente de vetores de entrada.

Figura 3. Modelo geral de testbench proposto por Bergeron, 2003

Note que o termo "simulação" torna-se incorreto no contexto deste projeto, porque a descrição RTL cuja funcionalidade se deseja depurar será sintetizada e em seguida prototipada sobre um FPGA. Módulos operacionais adicionais também serão introduzidos no FPGA juntamente com a sintetização da descrição RTL, de modo a permitir a interação do usuário com o protótipo em operação.

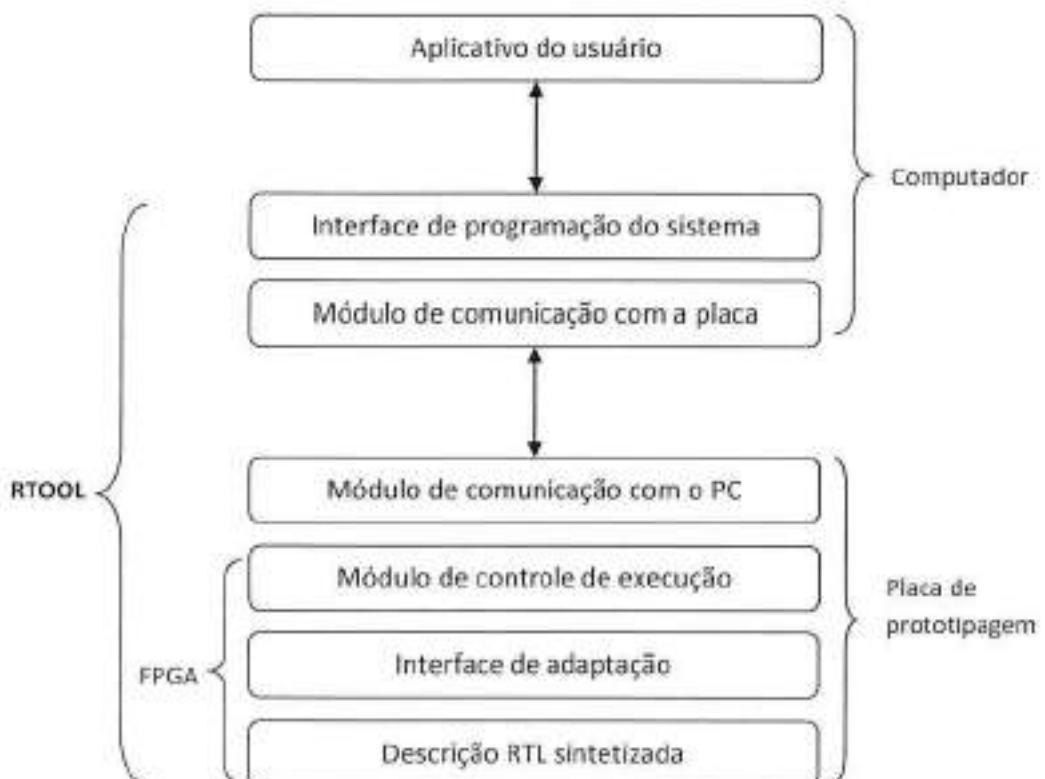

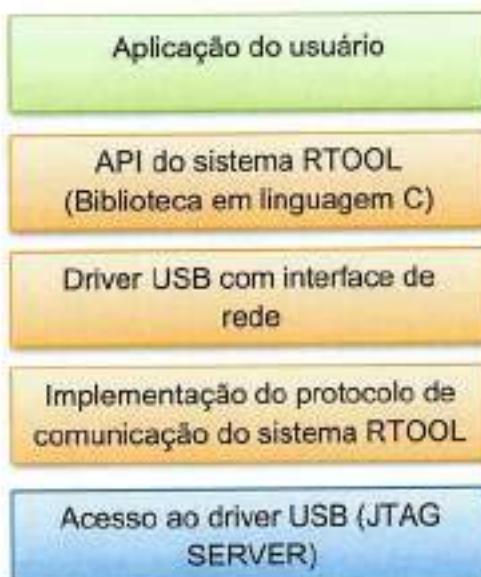

Uma visão do sistema RTOOL em camadas é apresentada na figura 4. Cada camada utiliza funcionalidades da camada imediatamente inferior, e provê funcionalidades à camada imediatamente superior. A interface de programação do sistema (camada superior do sistema RTOOL) fornecerá ao usuário todas as funcionalidades necessárias à depuração da descrição RTL sintetizada.

Figura 4. Camadas do sistema proposto.

Não foram encontradas soluções estruturadas no mercado de sistemas de depuração que utilizam a metodologia proposta acima, ou seja, a utilização de um FPGA como núcleo do sistema. Contudo, observou-se que tal metodologia é aplicada em casos específicos para se obter maior desempenho (Serrestou, Beroullie, Robach, 2007).

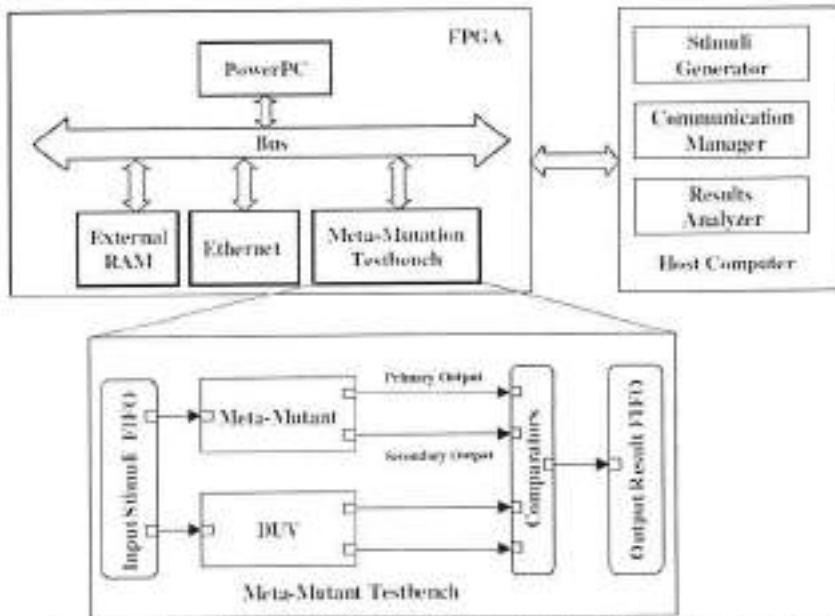

Uma arquitetura específica para a prototipagem de uma descrição RTL em um FPGA pode ser vislumbrada na figura 5. Esta arquitetura foi proposta dentro de um contexto de quantificação da qualidade de métodos de verificação funcional, ou seja, da avaliação se estes métodos são realmente eficazes na detecção de erros de hardware.

A abordagem usada para se avaliar a eficácia de métodos de verificação funcional adotada por Serrestou, Beroullie e Robach consiste, inicialmente, na introdução de erros propositais numa descrição RTL, gerando-se descrições “mutantes” (*metamutante*). Em seguida, é verificado se a metodologia de depuração de interesse é capaz de acusar o erro introduzido propositalmente. Idealmente, uma metodologia de depuração eficaz não deixará passar branco nenhum erro.

Figura 5. Solução específica proposta por Serrestou, Beroulli, Robach, 2007

A arquitetura intra-FPGA da figura 5 contém, além da sintetização da descrição RTL do usuário (com o nome de *Meta-Mutation Testbench*), um módulo de comunicação ethernet, uma memória RAM externa e um processador para gerenciamento da emulação. Todos estes elementos estão interligados por um barramento interno de comunicação (*Bus*).

Apesar da solução específica da figura 5 conter todos os elementos de hardware necessários à prototipagem de uma descrição RTL, alguns pontos dificultam sua reutilização em outros projetos:

- A integração de uma nova descrição RTL com entradas/saídas distintas da original requer o desenvolvimento manual de um hardware de adaptação desta nova descrição RTL ao resto do sistema.

- O software embarcado do processador intra-FPGA necessitaria ser modificado para fornecer suporte à nova descrição RTL, a qual possui portos de entrada/saída distintos daqueles do projeto original.

- Uma modificação deveria ser feita no driver gerenciador da comunicação, o qual é executado no computador, para torná-lo compatível com o novo software embarcado.

Vale lembrar que, para se efetuar todas estas modificações, é necessário estudar a fundo a arquitetura específica em questão. Todos estes empecilhos tornam o reuso de uma solução específica inviável, dado o tamanho do esforço que seria empregado na adaptação da solução específica a um novo projeto.

Algumas propostas de sistemas de depuração com hardware dedicado encontradas na literatura (Tsai, 1994) propõem o desenvolvimento de placas multiprocessadoras para acelerar a simulação HDL. Contudo, tais soluções demandam o desenvolvimento de complicados softwares de interpretação e execução HDL que busquem tirar proveito de sistemas multiprocessados, e, mesmo assim, conclui-se que não há garantias sólidas de maior desempenho.

### 3. MATERIAIS E MÉTODOS

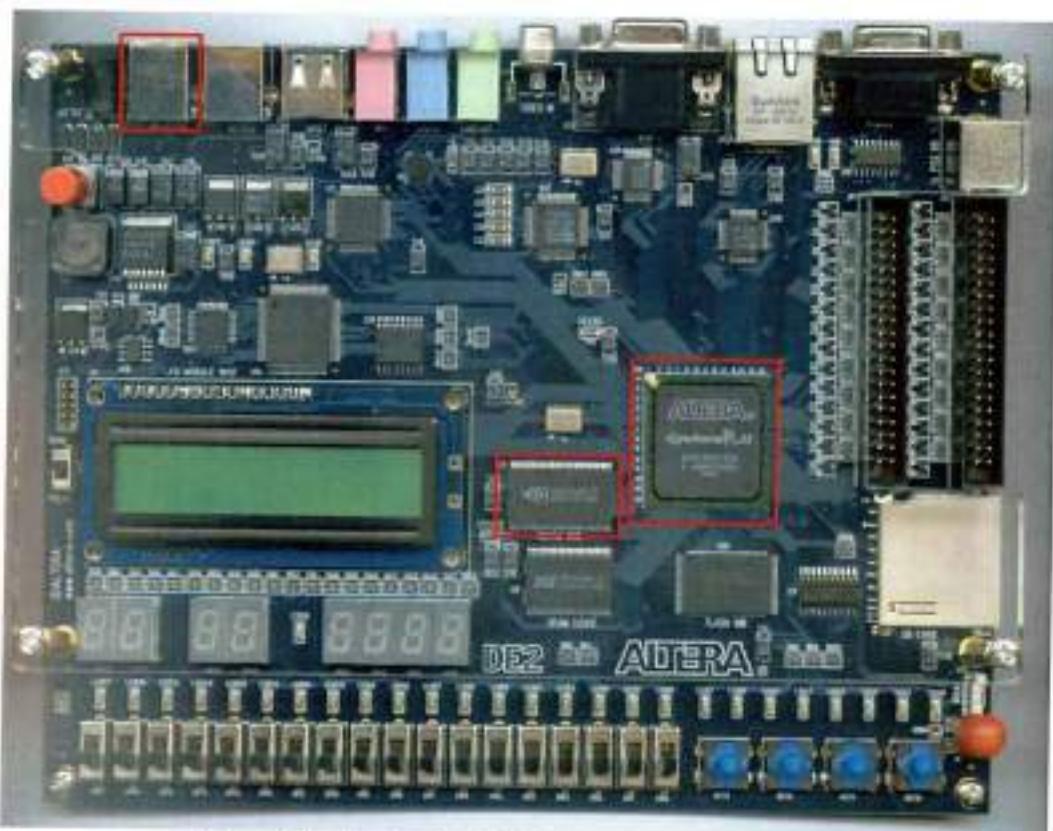

A implementação do hardware do sistema RTOOL foi feita a partir da utilização de um kit de desenvolvimento DE-2 da ALTERA, o qual possui os seguintes recursos de interesse para este projeto:

- FPGA Cyclone II EP2C35F672C6 com 35 mil elementos lógicos

- Memórias externas SDRAM com capacidade de 8 MB de dados

- USB-Blaster embutido para Entrada/Saída de dados do FPGA

A figura 6 mostra uma foto do kit de desenvolvimento DE-2 da ALTERA, destacando o conector USB no canto superior esquerdo, a memória SDRAM com capacidade de 8 MB ao centro e o FPGA Cyclone II mais à direita.

Figura 6. Foto da placa DE-2 usada no projeto RTOOL

A implementação do software do sistema RTOOL será feita em estações de trabalho compatíveis com a tecnologia atual, i.e., estações de trabalho com processadores de frequência de operação em torno de 2 GHz e utilizando-se o sistema operacional Microsoft Windows XP ou Microsoft Windows 7. Sobre estas estações de trabalho serão instalados os seguintes softwares:

- Quartus II, da Altera, para o desenvolvimento de projetos em VHDL

- Nios II Software Build Tools for Eclipse, para o desenvolvimento de software embarcado

- Compilador GNU GCC, para o desenvolvimento das ferramentas de usuário

- Microsoft Visual Studio, para o desenvolvimento de interfaces gráficas para as ferramentas de usuário

Quando finalizado, a forma de utilização do sistema RTOOL pelo usuário ocorrerá como apresentado na figura 7. Inicialmente tem-se um gerador de estímulos responsável por estimular as entradas do sistema RTOOL e as entradas do modelo de referência (tido como livre de erros). Após o processamento dos dados, as saídas do sistema RTOOL e as saídas do modelo de referência são comparadas em um bloco intitulado *Checker*. Após comparar ambas as saídas, o bloco *Checker* realimentará o gerador de estímulos com os resultados, de modo a se efetuar uma verificação abrangente.

Figura 7. Diagrama de blocos do sistema de verificação

A seguir tem-se um maior detalhamento da função de cada componente do diagrama:

**Gerador de estímulos:** O gerador de estímulos gera inicialmente entradas aleatórias utilizadas na verificação da correção do RTL. Entretanto, devido à realimentação do *Checker*, o gerador de estímulos poderá gerar sinais de entrada para determinadas condições de teste que ainda não foram verificadas. Apenas dados ou sinais relevantes representativos do comportamento do sistema são gerados, sendo sinais mais específicos de protocolo, como clock, enable, request, etc, desconsiderados.

**Buffer (FIFO):** O buffer será do tipo FIFO (*First In First Out*) e será implementado tanto na entrada dos blocos do modelo de referência e do RTL, quanto na saída destes. A principal função destes blocos é de casar os sinais síncronos, provenientes do RTL, com os assíncronos provenientes do modelo de referência.

Modelo de referência: O modelo de referência é um programa previamente compilado e testado que executa as mesmas tarefas das que são pretendidas pelo projeto do RTL, servindo, portanto, como base de comparação para a realização de testes. Assume-se que o modelo de referência é uma descrição sem erros do comportamento do circuito. Um fato importante é que o modelo de referência, por ser uma descrição funcional em linguagens de programação de alto nível (C, C++, Java, por exemplo), utiliza-se de algoritmos e modelos matemáticos altamente eficientes para calcular suas saídas, de modo a requerer poucos recursos de processamento.

Driver: O driver é o componente responsável pela conversão do sinal de entrada em vetores de teste que serão utilizados pelo RTL. Além disso, é responsável pela geração dos sinais de controle da interface de entrada do RTL, sendo, por isso, bastante específico e variando de acordo com cada RTL que seja testado.

Monitor: Faz o papel inverso do driver, convertendo os vetores de teste da saída do RTL em sinais compatíveis com a entrada do *Checker*.

Checker: É o bloco que fará a comparação dos sinais de saída gerados pelo modelo de referência com o RTL e que fornece uma realimentação ao gerador de estímulos para que este possa excitar o sistema de uma forma abrangente.

Para que um projetista digital não tenha de se adequar a uma nova metodologia de depuração, o sistema RTOOL será desenvolvido de modo a atender aos requisitos impostos pelo ambiente de verificação de corretude funcional de uma descrição RTL apresentado acima.

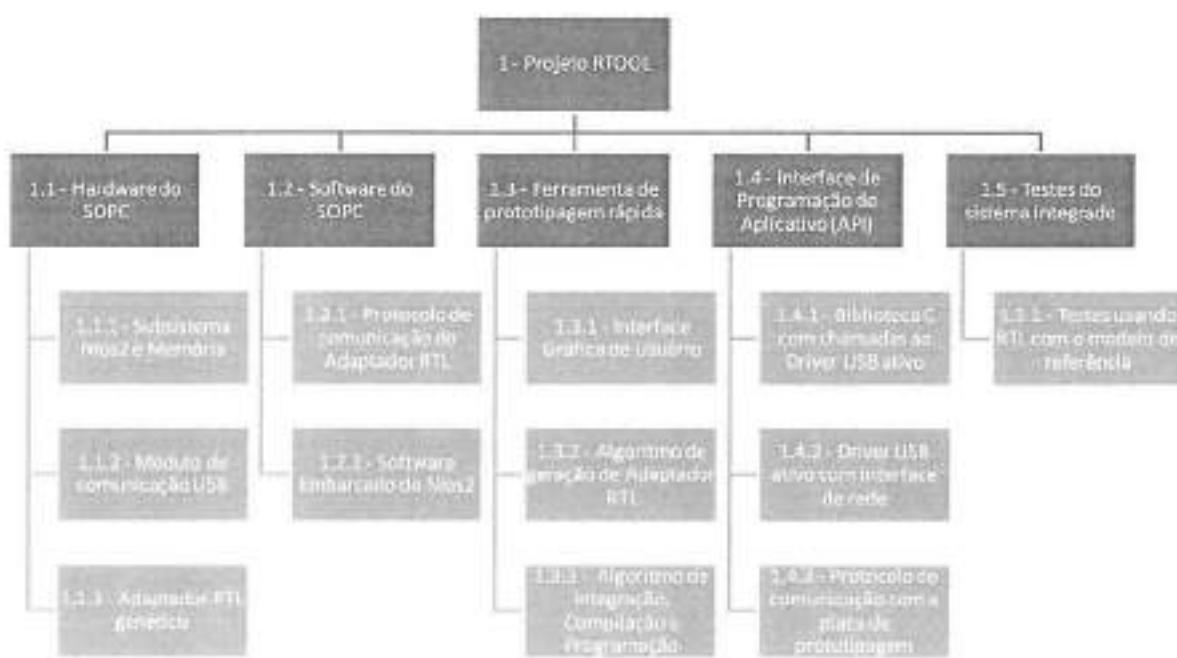

### 3.1 Estrutura analítica de projeto

O projeto RTOOL, no que diz respeito à sua implementação, foi dividido em cinco grupos principais de tarefas, como é apresentado na EAP (Estrutura Analítica de Projeto) da figura 8.

Figura 8. EAP do projeto RTOOL

É possível observar que, dentre as tarefas listadas na EAP, cerca de 25%, apenas, correspondem ao desenvolvimento de hardware, e o restante ao desenvolvimento de software. Contudo, a maior complexidade observada no desenvolvimento de hardware acarreta em um maior gasto de tempo nestas tarefas. Logo, é justo considerar uma divisão de trabalho no grupo de dois integrantes do projeto RTOOL na qual um focará mais atentamente no hardware do sistema, enquanto o outro focará mais atentamente no software do sistema.

### 3.1.1 Detalhamento da EAP

Para que o leitor tenha um melhor aproveitamento em sua leitura da seção "3.2 – Implementação do sistema RTOOL", a seguir é fornecido um detalhamento das tarefas da EAP da figura 8.

#### ➤ Hardware do SOPC:

Este grupo de tarefas corresponde ao desenvolvimento da arquitetura de hardware interna do FPGA. Nela, haverá um processador NIOS II responsável pelo gerenciamento dos demais periféricos, um módulo de comunicação USB, uma memória SRAM interna, uma memória SDRAM externa e um Adaptador RTL (descrito abaixo). Todas estas entidades estarão conectadas entre si pelo barramento AVALON.

- Subsistema NIOS II e memória: O processador NIOS II da ALTERA deverá estar conectado a uma memória SDRAM para que seja possível armazenar localmente os vetores de dados provenientes do circuito RTL do usuário em processo de emulação. A memória SRAM interna será usada apenas para guardar o software embarcado.

- Módulo de comunicação USB: A comunicação entre o computador, no qual é fornecida a API do sistema RTOOL, e a placa de prototipagem será feita através da interface USB, já que a interface serial RS-232 vem se tornando cada vez mais obsoleta.

- Adaptador RTL: Esta entidade tem por objetivo interligar a descrição RTL do usuário ao sistema RTOOL, funcionando como um "soquete" no qual o hardware do usuário é "encaixado". O Adaptador RTL fornece uma interface de comunicação assíncrona padronizada de modo a permitir uma diferenciação entre o hardware do RTOOL e o hardware do usuário no que diz respeito à domínios de *clock*.

#### ➤ Software do SOPC:

Este grupo de tarefas corresponde à todos os aspectos do software interno ao FPGA, desde a definição de protocolos de comunicação até o desenvolvimento do firmware do processador NIOS II.

- Protocolo de comunicação do Adaptador RTL: A estrutura de hardware do Adaptador RTL foi desenvolvida de modo a fornecer ao processador NIOS II (mestre do barramento AVALON) funcionalidades de leitura/escrita de dados, gerenciamento de interrupções e configuração da frequência do sinal de *clock* que alimenta o dispositivo RTL do usuário. A comunicação entre estas duas entidades é feita através de um mapa de registradores que controlam a operação do Adaptador RTL.

- Software Embarcado do NIOS II: O software embarcado do processador NIOS II tem por objetivo gerenciar os diversos processos que ocorrem na placa. São eles: processo de leitura/escrita do PC, processo de leitura do DRIVER e processo de escrita do MONITOR.

#### ➤ Ferramenta de prototipagem rápida:

Um dos aspectos mais importantes no desenvolvimento de um software é o nível de dificuldade que o usuário irá enfrentar ao usar o mesmo. Quanto mais fácil e intuitiva for a utilização de um software, maiores serão suas chances de ter sucesso no mercado. A ferramenta de prototipagem rápida visa facilitar ao

máximo a tarefa de implantação do sistema RTOOL para sua posterior utilização. Tarefas repetitivas como a integração da descrição RTL do usuário ao sistema, compilação do sistema e programação do FPGA foram automatizadas por esta ferramenta, a qual possui uma interface gráfica de usuário amigável.

- Interface Gráfica de Usuário: Consiste de uma interface gráfica de usuário amigável para conduzir o usuário durante o processo de implantação do sistema RTOOL.

- Algoritmo de geração de Adaptador RTL: A versão corrente do sistema RTOOL possui uma estrutura fixa para o Adaptador RTL, a qual fornece uma interface de comunicação assíncrona para o hardware do usuário. Logo, esta tarefa prevista no cronograma do projeto tornou-se desnecessária de acordo com a nova metodologia adotada.

- Algoritmo de Integração, Compilação e Programação: Tarefas repetitivas como a integração da descrição RTL do usuário ao sistema, compilação do sistema e programação do FPGA e do software embarcado foram automatizadas a partir deste algoritmo.

#### ➤ **Interface de Programação de Aplicativo:**

Após a implantação do sistema RTOOL pelo usuário, i.e., após a prototipagem de uma descrição RTL cuja corretude se deseja verificar, a interação do usuário com o sistema RTOOL será feita a partir de uma biblioteca de linguagem C que fornecerá todas as funcionalidades necessárias à depuração do circuito digital do usuário. Além disso, as funções da biblioteca em linguagem C podem ser facilmente integradas a uma descrição de hardware em linguagem SystemC, permitindo a co-simulação de um modelo de referência em linguagem SystemC e do código RTL sintetizável em processo de emulação no FPGA.

- Biblioteca C com chamadas ao Driver USB ativo: Definição das funções que serão disponibilizadas para o usuário do sistema RTOOL e implementação destas funções através da comunicação com o Driver USB Ativo (o qual se comunica diretamente com a placa de prototipagem).

- Driver USB ativo com interface de rede: Optou-se pelo desenvolvimento de um Driver USB ativo em modo usuário, em detrimento ao modo *kernel*, pela maior facilidade de implementação. Este Driver USB Ativo irá possuir a forma de um processo num sistema operacional, e a sua comunicação com a biblioteca C que será integrada a um aplicativo do usuário será feita via interface de rede TCP/IP. A comunicação entre processos via interface

de rede é uma alternativa de mais fácil implementação à forma tradicional que usa "pipes" do sistema operacional.

- Protocolo de comunicação com a placa de prototipagem: Este protocolo de comunicação foi definido na tarefa "1.2", e sua implementação é compatível com as especificações ali determinadas. Em resumo, este protocolo estabelece quais serviços são oferecidos ao usuário pela placa de prototipagem e como estes serviços devem ser requisitados através da comunicação via interface USB.

#### ➤ **Testes do Sistema Integrado:**

Esta é a etapa final e uma das mais importantes do projeto. Requer controle de tempo rigoroso e exaustivos testes para se ter certeza da corretude do sistema. Será utilizado como modelo de teste um modelo de referência seguido do seu RTL equivalente.

- Testes utilizando o RTL com o modelo de referência: Os testes realizados nessa etapa serão feitos utilizando-se como base um modelo de referência, supostamente correto, que será comparada ao RTL equivalente que também será admitido como correto. Para isso a equipe pretende elaborar modelos e RTL simples para efetuar os testes iniciais. Após validado o sistema RTOOL, será feita a medida de seu desempenho para uma comparação com as ferramentas de simulação mais usadas na indústria.

### **3.2 Implementação do sistema RTOOL**

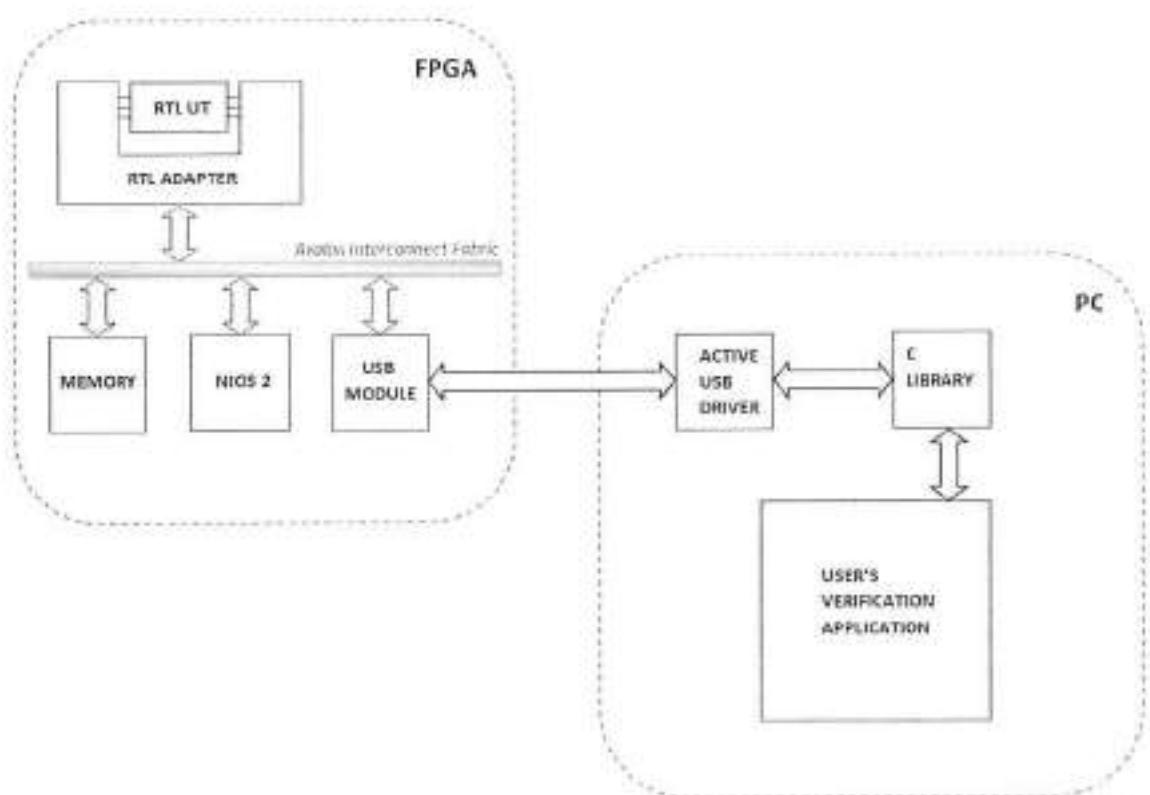

A figura 9 mostra um diagrama de blocos detalhado do objetivo, do ponto de vista da implementação, do sistema RTOOL, com todas as entidades previamente apresentadas.

Figura 9. Diagrama de blocos do sistema RTOOL. Os blocos em vermelho são responsabilidade do usuário

Os detalhes pertinentes à forma pela qual cada submódulo do sistema RTOOL foi implementado são fornecidos nas subseções que seguem.

### 3.2.1 Hardware do SOPC

Este capítulo descreve a implementação dos três módulos de hardware constituintes do SOPC do sistema RTOOL. Serão abordados: O subsistema Nios II e memória SDRAM externa; O módulo de comunicação USB; O adaptador RTL.

#### 3.2.1.1 Subsistema Nios II e memória SDRAM externa

Para se implementar o subsistema Nios II e memória SDRAM externa utilizou-se o software QUARTUS II da ALTERA com o auxílio de seu módulo interno QSYS, o qual permite a construção de um SOPC através da interligação de componentes de hardware sobre um barramento de dados.

Os principais componentes deste subsistema são:

- Processador NIOS II Standard com 20 KB de Onchip Memory

- Controlador de memória SDRAM compatível com o barramento AVALON

- Memória SDRAM externa ao FPGA com 8 MB de dados

- PLL (*Phase Locked Loop*)

O processador NIOS II, categorizado como “softcore” pelo fato de ter sido desenvolvido completamente numa HDL, corresponde a uma arquitetura de segunda geração de processadores embarcados de 32 bits voltados especificamente à família de FPGAs da ALTERA.

Segundo a Gartner Research, o processador NIOS II é o *soft processor* mais amplamente usado na indústria de FPGAs. Ele também é um processador muito versátil, podendo ser configurado minunciosamente para atender aos requisitos de cada aplicação, sejam eles requisitos de desempenho (Nios II *fast core*), de confiabilidade (Nios II *safe critical core*), de uso de recursos (Nios II *economy core*), entre outros.

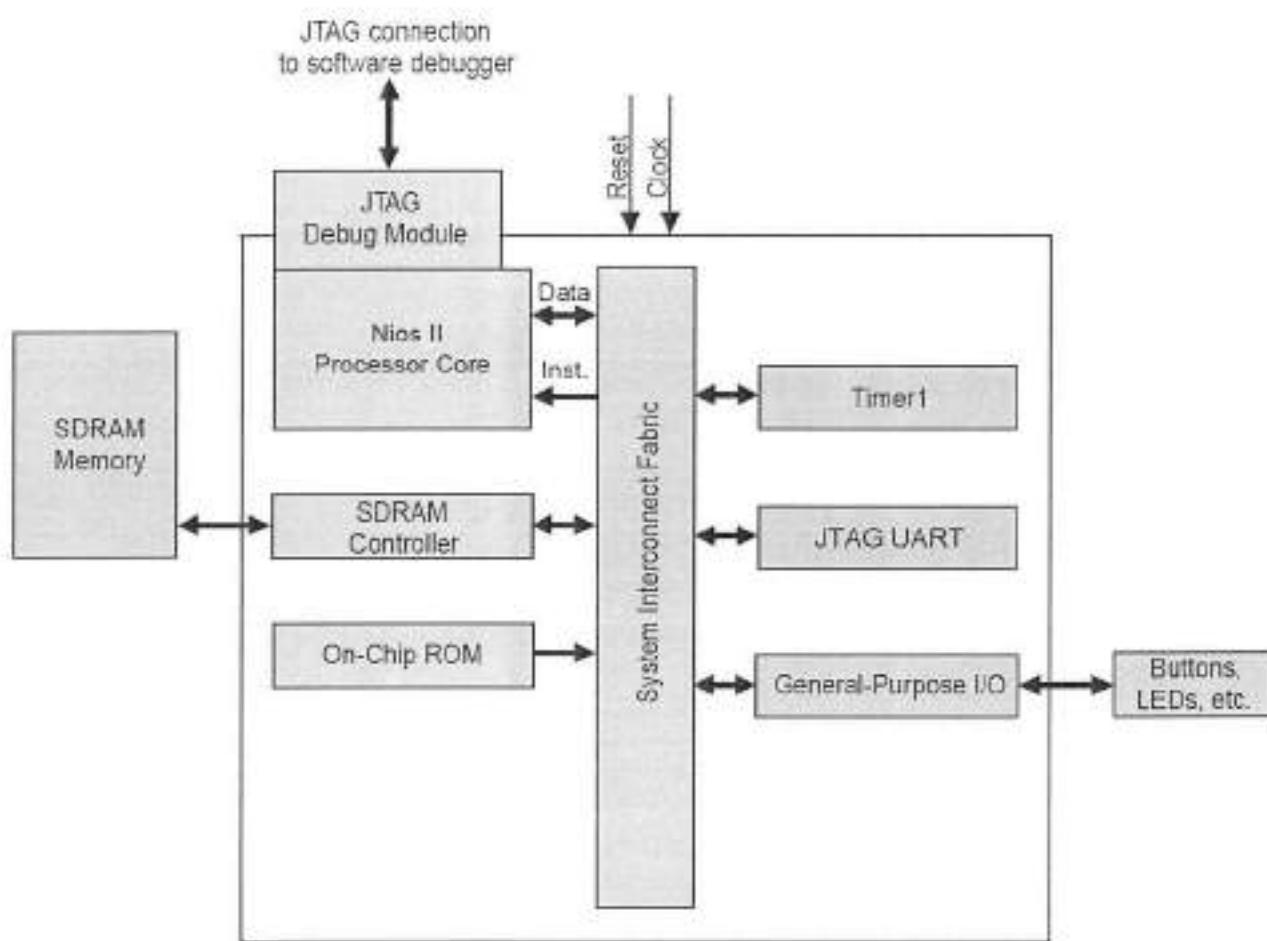

A configuração adotada para o sistema RTOOL foi a “*standard core*”, a qual busca otimizar tanto o desempenho do processador quanto a sua utilização de recursos do FPGA. A figura 10 mostra um diagrama simplificado do subsistema construído e os periféricos selecionados.

Figura 10. Sistema Nios II construído para o projeto RTOOL (Modificado de: *Nios II Processor Reference Handbook*, pág. 11)

Pode-se observar que a comunicação entre o processador NIOS II e seus periféricos é feita através de um barramento de dados entitulado “*System Interconnect Fabric*”. Este barramento, de 32 bits de comprimento, também chamado de barramento AVALON, é especificado pela ALTERA para que projetistas de hardware possam desenvolver dispositivos compatíveis com o processador NIOS II.

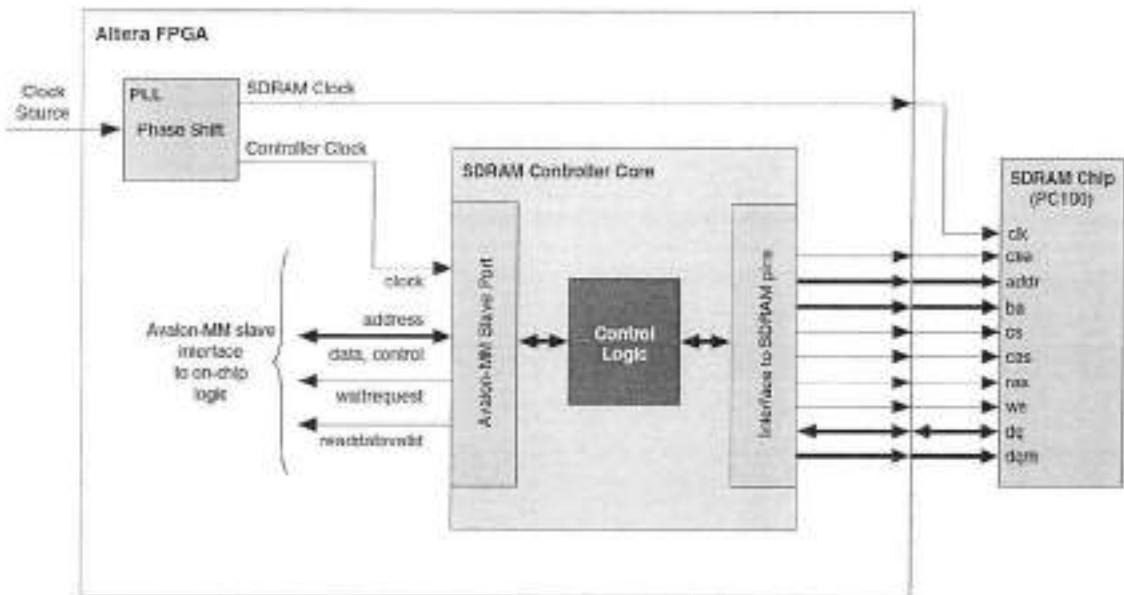

O controlador de memória SDRAM usado tem duas funcionalidades principais. Primeiro, como todos os controladores de memória SDRAM disponíveis no mercado, ele executa ciclos periódicos de atualização (*refresh*) da memória SDRAM para que os dados guardados na mesma sejam preservados. Segundo, ele compatibiliza a interface de leitura/escrita da memória SDRAM à interface de leitura/escrita do barramento AVALON. A figura 11 mostra os detalhes do controlador.

Figura 11. Controlador de memória SDRAM (Fonte: *Embedded Peripherals IP User Guide*, pág. 24)

Na figura 11 também está presente o PLL, que tem o intuito de ajustar a defasagem entre o sinal de clock que alimenta o controlador de memória SDRAM e o sinal de clock que alimenta a própria memória SDRAM. Este ajuste depende do layout da placa de circuito impressa na qual estão soldados o FPGA e a memória SDRAM, e ele visa compensar o atraso imposto pelo comprimento das trilhas que interligam estes dois componentes.

Optou-se pelo uso da memória SDRAM como meio de armazenamento maciço de dados levando-se em conta a sua capacidade de memória (8 MB). Isto permitiu reduzir a utilização de recursos do FPGA, tornando o hardware do RTOOL mais enxuto.

Para projetos mais simples, seria possível utilizar também a memória interna do FPGA para o propósito de armazenagem em detrimento de uma maior utilização de área do FPGA. No caso deste projeto a memória interna será utilizada somente com o propósito de armazenar o software embarcado do NIOS II.

LEDs de indicação de status também foram adicionados ao hardware do sistema para facilitar o processo de depuração do software embarcado.

### 3.2.1.1 Software de gerenciamento da memória SDRAM

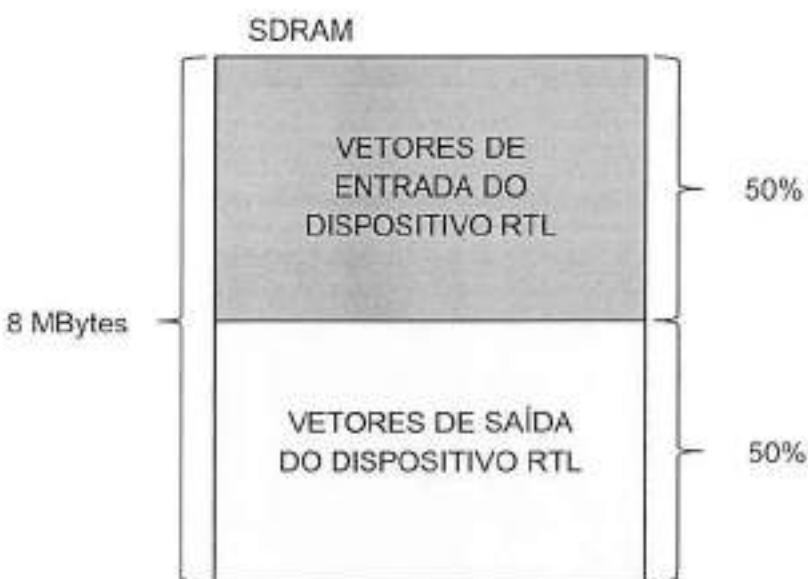

O projeto RTOOL prevê que a memória SDRAM externa será utilizada para armazenar vetores de dados de entrada/saída do dispositivo RTL que será emulado. Logo, o software de gerenciamento da memória divide a mesma em duas regiões, de acordo com a figura 12.

Figura 12. Divisão da Memória SDRAM

Cerca de 4 MB de dados foram reservados para o armazenamento de vetores de entrada do dispositivo RTL (enviados pelo PC e requisitados pelo DRIVER), e cerca de outros 4 MB foram reservados para o armazenamento de vetores de saída do dispositivo RTL (enviados pelo MONITOR e requisitados pelo PC).

Cada uma das regiões de memória é tratada independentemente da outra como um *buffer FIFO* circular, ou seja, sempre que, em uma operação de escrita/leitura, se atingir a última posição de uma região de memória, o endereço de escrita/leitura seguinte irá retornar à posição inicial desta região de memória.

Este tipo de tratamento da memória é adequado para o sistema RTOOL porque os vetores de dados são acessados sequencialmente.

Em pseudo-código, as funções de escrita/leitura de uma região memória tratada como um *buffer FIFO* circular seriam:

```

/* Definição das dimensões do buffer */

#define TOPO_DA_REGIAO    0x00600000

#define FUNDO_DA_REGIAO   0x00000000

#define TAMANHO_DA_REGIAO 0x00600000

/* Indica o número de dados que podem ser lidos do buffer */

int DadosDisponiveis()

{

int dif;

dif = ponteiro_de_escrita - ponteiro_de_leitura;

if( ponteiro_de_escrita > ponteiro_de_leitura )

return dif;

else

return TAMANHO_DA_REGIAO + dif;

```

```

}

/* Indica o número de dados que podem ser escritos no buffer */

int EspacosDisponiveis()

{

return TAMANHO_DA_REGIAO - DadosDisponiveis();

}

/* Insere um dado no buffer */

void EscreveDado( unsigned int dado )

{

*ponteiro_de_escrita = dado;

*ponteiro_de_escrita = *ponteiro_de_escrita + 1;

if( ponteiro_de_escrita > TOPO_DA_REGIAO )

ponteiro_de_escrita = FUNDO_DA_REGIAO;

}

/* Lê um dado do buffer */

unsigned int LeDados()

{

unsigned int dado;

dado = *ponteiro_de_leitura;

*ponteiro_de_leitura = *ponteiro_de_leitura + 1;

if( ponteiro_de_leitura > TOPO_DA_REGIAO )

ponteiro_de_leitura = FUNDO_DA_REGIAO;

return dado;

}

```

A partir destas funções é possível implementar-se um *buffer* FIFO circular independente em cada uma das regiões de memória. Contudo, no pseudo-código apresentado faz-se necessária uma verificação de memória cheia ou memória vazia antes de se efetuar operações de escrita ou leitura, respectivamente, para que não haja *overflow* ou *underflow*.

Apesar da memória SDRAM externa ter comprimento de palavra de apenas 16 bits, o controlador da memória SDRAM, por causa de sua arquitetura de hardware, permite que operações de escrita/leitura com palavras de 32 bits de comprimento sejam efetuadas pelo processador NIOS II. Desta forma, o processador NIOS II consegue, em média, reduzir pela metade o uso do barramento AVALON para o acesso à memória.

O uso da memória SDRAM pelo sistema RTOOL será retomado mais adiante quando for tratado o software do SOPC e sua máquina de estados.

### 3.2.1.2 MÓDULO DE COMUNICAÇÃO USB

A solução adotada para a comunicação USB entre a placa de prototipagem e o computador (PC) foi a utilização de um núcleo JTAG UART compatível com o barramento AVALON.

Assim como em uma linguagem convencional de programação de software existem bibliotecas com funções pré-definidas que podem ser aproveitadas por um programador durante o desenvolvimento de sua aplicação, em linguagens de programação de hardware também existem núcleos funcionais pré-definidos que podem ser integrados ao projeto de um hardware qualquer. O núcleo JTAG UART, desenvolvido pela Altera, foi escolhido pelo grupo para ser integrado ao projeto do RTOOL devido à sua praticidade.

A figura 13, extraída do manual do fabricante, apresenta uma visão geral das funcionalidades que a utilização do núcleo JTAG UART permite introduzir ao sistema:

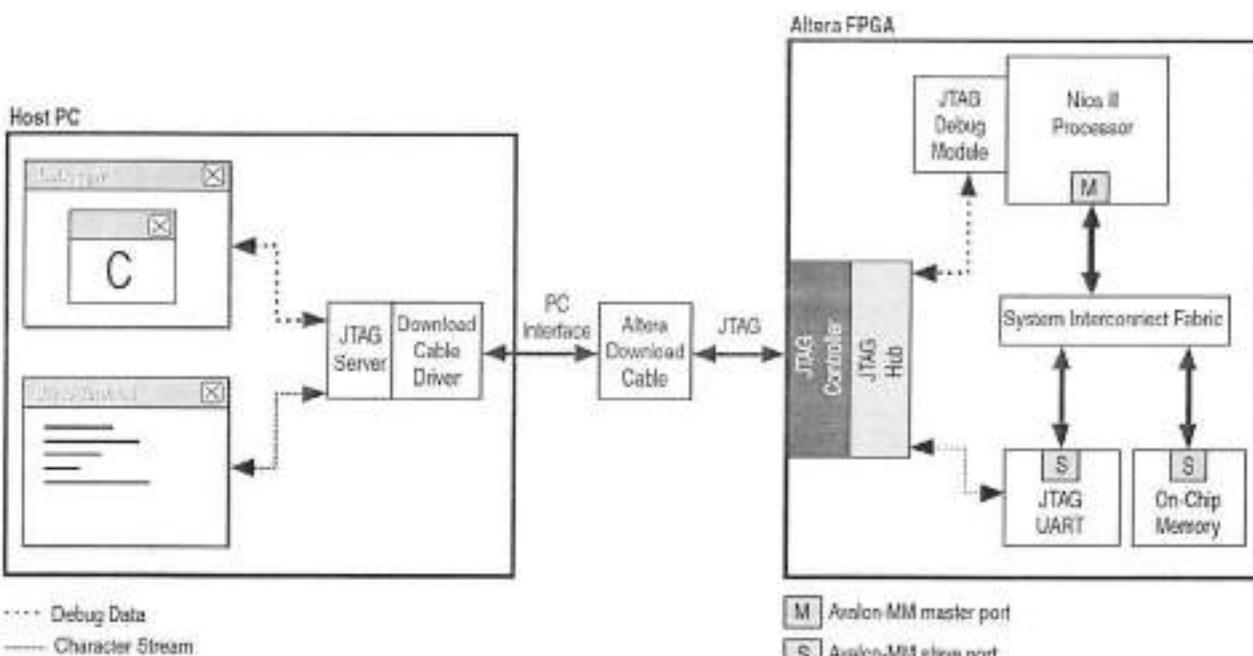

Figura 13. Diagrama de blocos (Fonte: Manual JTAG UART core, pág. 3)

O núcleo JTAG UART atuará como um escravo do barramento AVALON, e permitirá que o processador NIOS II envie um fluxo de dados à uma aplicação em execução no PC. O caminho que este fluxo de dados irá percorrer até atingir seu destino final é mostrado na figura 13, e é descrito sucintamente a seguir.

Logo após ter sido enviado ao núcleo JTAG UART, o fluxo de dados será encaminhado ao controlador JTAG (JTAG Controller). Em seguida, o controlador JTAG irá transmitir o fluxo de dados ao PC através de um cabo de download da

Altera (Altera Download cable), que consiste de um cabo USB. Ao chegar ao computador através do cabo USB, o fluxo de dados será armazenado em um buffer de entrada do driver do cabo de download (Download Cable Driver). Este driver atuará como um servidor (JTAG Server), fornecendo uma API para permitir que a aplicação do usuário receba o fluxo de dados armazenado no buffer temporário. Ao ser lido pela aplicação final, o fluxo de dados originado no processador NIOS II termina seu percurso.

Caso a aplicação no PC deseje enviar um fluxo de dados ao NIOS II, o percurso que este fluxo irá percorrer até seu destino final será o mesmo descrito para o caso do processador NIOS II enviar um fluxo de dados ao PC, porém na ordem contrária. A aplicação do PC irá inicialmente enviar o fluxo de dados ao servidor JTAG, o qual encaminhará os dados, através do cabo de download USB da Altera, ao controlador JTAG presente na placa de prototipagem. O controlador JTAG, por sua vez, enviará o fluxo de dados ao núcleo JTAG UART onde os dados serão armazenados em um buffer de entrada, do qual poderão ser recuperados pela aplicação em execução no processador NIOS II através de uma operação de leitura no barramento Avalon.

Todos os componentes presentes no subsistema JTAG, sendo eles o núcleo JTAG UART, o controlador JTAG, o cabo de download da Altera, o driver do cabo de download e o servidor JTAG não necessitam ser implementados, ou seja, eles são fornecidos pela ALTERA e estão prontos para serem usados. Consequentemente, pelo fato destes componentes não precisarem ser desenvolvidos neste projeto, um tempo valioso foi economizado. Além disso, a solução sendo adotada possui alta confiabilidade por ser amplamente utilizada por projetistas que utilizam FPGAs da ALTERA (esta solução só é disponibilizada para FPGAs da ALTERA).

No lado do processador NIOS II, a utilização do núcleo JTAG UART será feita através de macros de acesso ao barramento AVALON, como apresentado no código abaixo:

```

/* Macro para leitura do barramento Avalon */

unsigned int IORD( void* BASE_ADDRESS, void* OFFSET );

/* Macro para escrita no barramento Avalon */

void IOwR( void* BASE_ADDRESS, void* OFFSET, unsigned int VALUE );

```

Sendo BASE\_ADDRESS o endereço do periférico do barramento Avalon que se deseja acessar, OFFSET uma variação de endereço relativa ao endereço base e VALUE o valor que se deseja transmitir pelo barramento. Como o processador NIOS II possui uma arquitetura de 32 bits, o parâmetro VALUE é do tipo "unsigned int". Contudo, transações de variáveis de um byte ou de dois bytes também são permitidas.

Esta forma de acesso à periféricos é típica de dispositivos mapeados em memória, ou seja, dispositivos cujas operações de escrita e leitura realizadas pelo processador são análogas à operações de acesso à memória.

O núcleo JTAG UART possui um conjunto de registradores que controla seu funcionamento. O mapa de registradores do núcleo JTAG UART é apresentado na tabela 1.

Tabela 1. Mapa de registradores (Fonte: Manual JTAG UART core, pág. 12)

| Offset | Register Name | R/W | Bit Description |     |          |          |    |     |         |    |    |   |   |      |   |   |   |

|--------|---------------|-----|-----------------|-----|----------|----------|----|-----|---------|----|----|---|---|------|---|---|---|

|        |               |     | 31              | ... | 16       | 15       | 14 | ... | 11      | 10 | 9  | 8 | 7 | ...  | 2 | 1 | 0 |

| 0      | data          | RW  | RAVAIL          |     | RVALID   | RESERVED |    |     |         |    |    |   |   | DATA |   |   |   |

| 1      | control       | RW  | WSPACE          |     | RESERVED | AC       | WI | RI  | RESERV. | WE | RE |   |   |      |   |   |   |

É importante observar que o campo DATA, que representa o topo dos buffers FIFO de entrada e de saída deste núcleo, possui apenas 8 bits. Isto significa que o núcleo JTAG UART trabalha com variáveis de um byte. Outros campos importantes são RAVAIL, que contém o número de bytes disponíveis para leitura no buffer FIFO de entrada, RVALID, que indica se o campo DATA é válido e WSPACE, que representa o espaço disponível para escrita no buffer de saída (em bytes). Os demais campos estão relacionados à configuração e execução de interrupções.

No lado do PC o acesso ao subsistema JTAG é feito através de uma API de comunicação com o servidor JTAG. A API em questão possui o nome "JTAG ATLANTIC", e pode ser encontrada na biblioteca dinâmica "jtag\_atlantic.dll". As principais funções desta biblioteca são mostradas no código abaixo:

```

/* Estrutura que mantém informações sobre o estado da comunicação JTAG */

typedef struct JTAGATLANTIC JTAGATLANTIC;

/* Abre o canal de comunicação */

JTAGATLANTIC* jtagatlantic_open( const char *chain, int device_index, int link_instance, const char *app_name );

/* Fecha o canal de comunicação */

void jtagatlantic_close( JTAGATLANTIC *link );

/* Envia dados pelo canal de comunicação aberto */

int jtagatlantic_write( JTAGATLANTIC *link, char *buf, unsigned int bufLen );

/* Recebe dados do canal de comunicação aberto */

int jtagatlantic_read( JTAGATLANTIC *link, char *buf, unsigned int bufLen );

/* Indica o número de bytes disponíveis para leitura */

int jtagatlantic_bytes_available( JTAGATLANTIC *link );

```

### 3.2.1.3 ADAPTADOR RTL

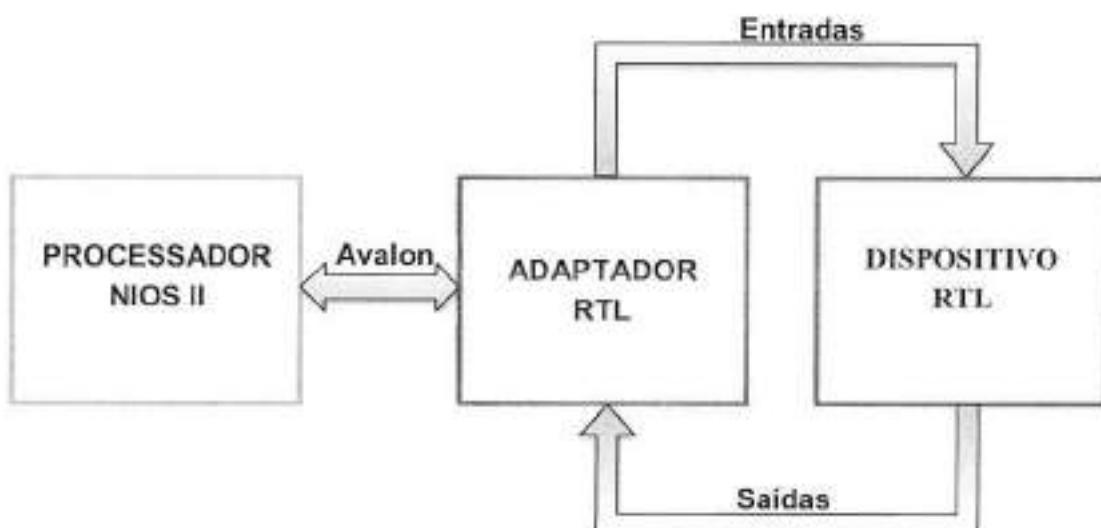

O adaptador RTL genérico é o módulo de hardware responsável pela interligação ao sistema RTOOL de um dispositivo RTL qualquer que se deseje depurar. De um lado o adaptador RTL se comunicará com o processador NIOS II através do barramento AVALON, enquanto que do outro lado o adaptador RTL se conectará diretamente às interfaces de entrada e de saída do dispositivo RTL que será depurado. O diagrama da figura 14 mostra como o adaptador RTL se encaixa no contexto do projeto RTOOL.

Figura 14. Diagrama do contexto no qual o adaptador RTL está inserido

O primeiro passo tomado rumo à implementação do adaptador RTL foi o estudo da especificação do barramento AVALON (disponibilizada pela ALTERA), para poder se determinar quais sinais seriam convenientes a este dispositivo de acordo com as funcionalidades que ele deve oferecer.

#### 3.2.1.3.1 Barramento AVALON

O barramento AVALON foi desenvolvido pela Altera para se efetuar a interconexão de dispositivos em um sistema integrado construído sobre um FPGA. São suportados sete tipos diferentes de interfaces sobre o barramento AVALON, de modo a fornecer todas as funcionalidades que um barramento de dados convencional possui. As interfaces de interesse ao Adaptador RTL são descritas sucintamente na tabela 2. Na primeira coluna tem-se o nome da interface, enquanto na segunda coluna é fornecida sua descrição.

Tabela 2. Descrição das interfaces selecionadas para o Adaptador RTL (Fonte: *Avalon Interface Specification*, pág. 5)

| Interface                      | Descrição                                                                                                                                                   |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Avalon Memory Mapped Interface | Típica interface de leitura/escrita baseada em endereçamento.                                                                                               |

| Avalon Conduit Interface       | Conjunto de sinais adicionais, não definidos na especificação do barramento Avalon, que podem ser usados para a conexão com um dispositivo externo ao SOPC. |

| Avalon Interrupt Interface     | Interface para a implementação da funcionalidade de interrupção. Por exemplo, um periférico pode requisitar uma interrupção ao processador.                 |

| Avalon Clock Interface         | Necessária à sincronização dos dispositivos conectados ao barramento Avalon. Todas as interfaces do barramento são síncronas.                               |

| Avalon Reset Interface         | Permite que seja enviada uma requisição de reinicialização a um dispositivo conectado ao barramento.                                                        |

Os sinais de entrada/saída especificados pelo barramento AVALON são flexíveis, ou seja, um dispositivo compatível com o barramento Avalon pode apresentar um número variável de interfaces, de acordo com suas necessidades.

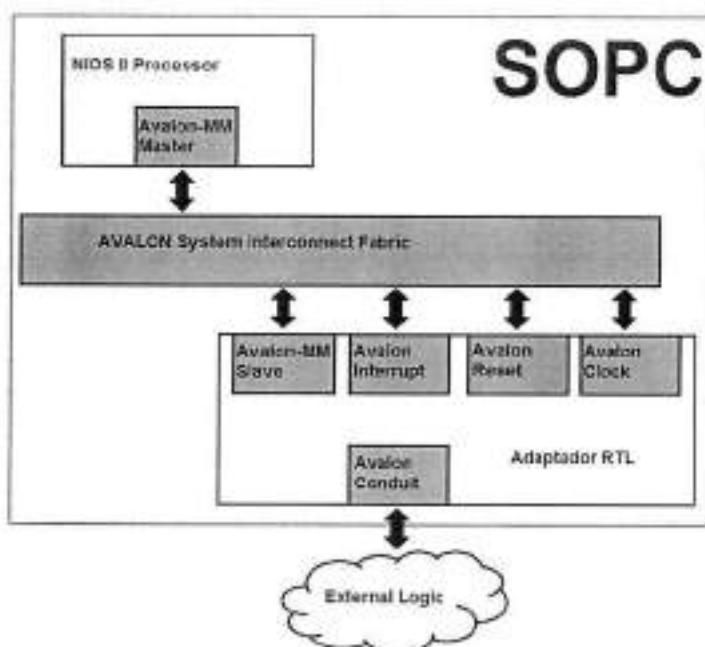

A figura 15 mostra como o Adaptador RTL é interligado ao barramento AVALON, de acordo com o conjunto de interfaces selecionadas.

Figura 15. Diagrama de interligação entre o Adaptador RTL e o barramento AVALON

Note que a interface AVALON Conduit permite que dispositivos externos se comuniquem com o SOPC. No contexto do sistema RTOOL, o circuito lógico externo corresponde ao dispositivo RTL do usuário.

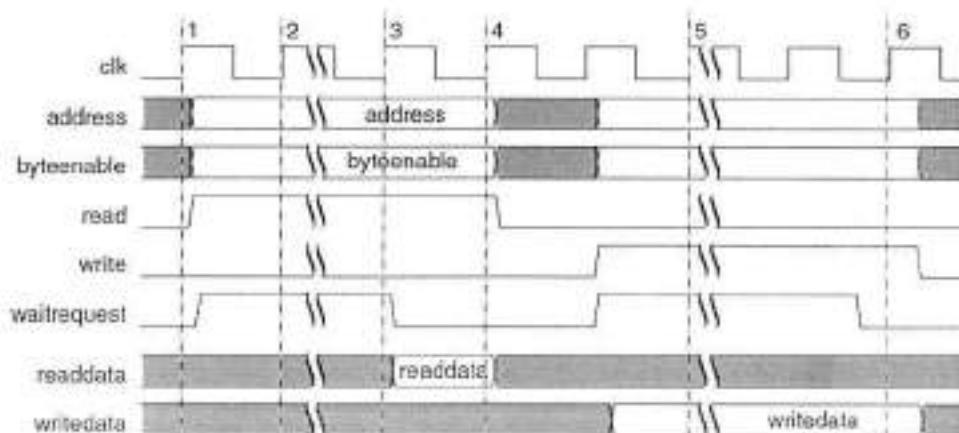

A sequência de sinalização necessária à realização de uma transferência de dados, tanto para uma operação de leitura como para uma operação de escrita, sobre o barramento Avalon é apresentada na figura 16.

Figura 16. Carta de tempos do barramento Avalon (Fonte: *Avalon Interface Specification*, pag. 22)

Na primeira borda de subida do clock (1) tanto o sinal "write" como o sinal "read" estão em nível baixo, o que indica que o mestre do barramento não deseja realizar nenhuma operação naquele momento. Já na segunda borda de subida (2) pode-se perceber que o sinal "read" assumiu nível lógico alto, o que indica que o mestre do barramento deseja efetuar uma leitura. Contudo, devido ao fato de o escravo ter colocado o sinal "waitrequest" em nível alto, o mestre irá aguardar antes de finalizar a operação. Logo após a terceira borda de subida do clock (3) o escravo atualiza as saídas "readdata" e "waitrequest" de acordo com o valor de endereço "address" enviado pelo mestre do barramento Avalon. Consequentemente, na quarta borda de subida do clock (4) o mestre do barramento irá ler o valor requisitado e a operação de leitura estará completa.

A operação de escrita também é apresentada na figura 16, e é análoga à operação de leitura. Contudo, neste caso o mestre do barramento deve enviar o valor de "writedata" que deseja escrever no endereço "address". Novamente, a operação somente chegará ao final após o escravo do barramento colocar o sinal "waitrequest" em nível lógico baixo.

Para se enviar um comando de *reset* ao dispositivo escravo, o mestre do barramento deverá ajustar o sinal *reset* da AVALON Reset Interface para nível lógico alto antes da próxima borda de subida do sinal de clock, e mantê-lo estável até a subsequente borda de descida (a operação é síncrona).

Com relação às interrupções, basta que o dispositivo escravo modifique o valor do sinal "irq\_n" da AVALON *Interrupt Interface* para nível lógico alto para que a requisição seja enviada ao processador NIOS II. Após a interrupção ter sido tratada, o dispositivo escravo do barramento deverá ajustar o nível lógico do sinal "irq\_n" de volta para zero.

### 3.2.1.3.2 Funcionalidades do Adaptador RTL

A seleção das interfaces do barramento AVALON adequadas ao Adaptador RTL considerou os seguintes requisitos funcionais:

- O Adaptador RTL deve permitir que o processador NIOS II efetue operações de escrita/leitura dos sinais pertencentes à interface AVALON *Conduit Interface*, os quais serão usados para a interligação da descrição RTL do usuário ao sistema RTOOL.

- O Adaptador RTL deve permitir que o dispositivo RTL do usuário envie requisições de transferência de dados de entrada/saída ao processador NIOS II através da interface AVALON *Interrupt*.

- O clock que alimenta o dispositivo RTL do usuário deve ser configurado (frequência de operação) pelo processador NIOS II.

- O processador NIOS II, sempre que desejar, deve ser capaz de restaurar as configurações iniciais do dispositivo RTL do usuário através do envio de um comando de reset.

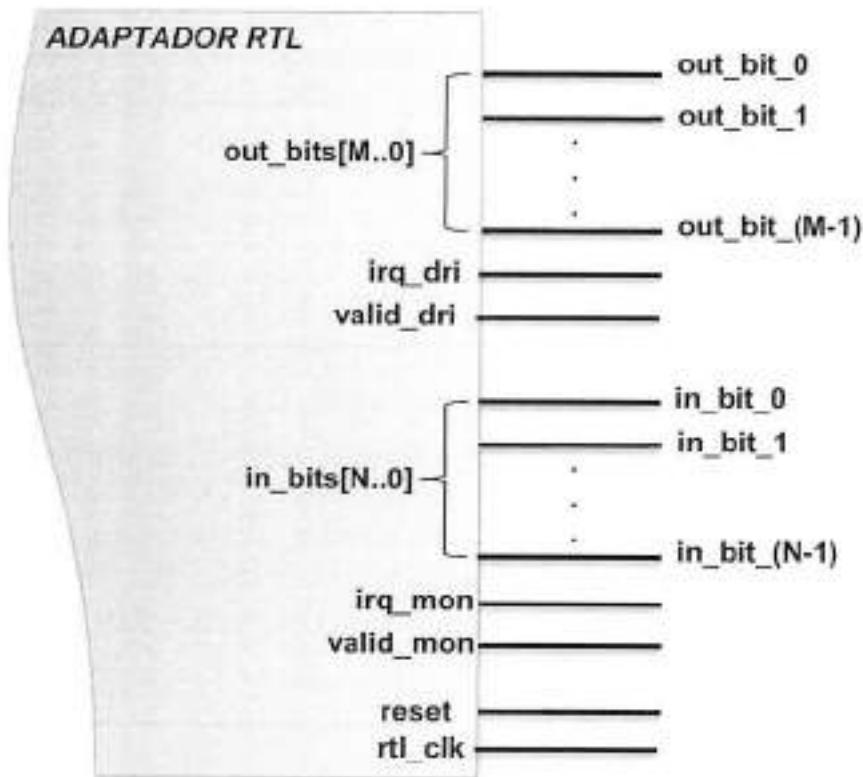

Levando em consideração estes requisitos funcionais, os sinais de interligação entre o Adaptador RTL e a descrição RTL do usuário, os quais pertencem à AVALON *Conduit Interface*, puderam ser definidos. O resultado é apresentado na figura 17.

Figura 17. Implementação da AVALON Conduit Interface para o Adaptador RTL.

Há três grupos de sinais, sendo eles sinais do DRIVER, sinais do MONITOR e os sinais GLOBAIS.

No grupo de sinais do DRIVER tem-se:

- Vetor de bits "out\_bits[M..0]": Bits de dados que o Adaptador RTL envia ao dispositivo RTL, cujo mapeamento lógico é definido de acordo com as interfaces de entrada presentes no DRIVER do usuário.

- Sinal de interrupção "irq\_dri": Bit controlado pelo DRIVER do usuário, o qual mantém nível baixo durante operação normal e assume nível alto quando o DRIVER requisitar novos dados válidos.

- Sinal "valid\_dri": Bit de indicação de dado válido no barramento "out\_bits" controlado pelo Adaptador RTL, o qual mantém nível baixo durante operação normal e, após uma requisição de dados por parte do DRIVER, assume nível alto quando o vetor "out\_bits" estiver pronto para ser lido.

No grupo de sinais do MONITOR tem-se:

- Vetor de bits "in\_bits[N..0]": Bits de dados que o dispositivo RTL envia ao Adaptador RTL, cujo mapeamento lógico é definido de acordo com as interfaces de saída presentes no MONITOR do usuário.

- Sinal de interrupção "irq\_mon": Bit controlado pelo MONITOR do usuário, o qual mantém nível baixo durante operação normal e assume nível alto quando o MONITOR desejar avisar que novos dados válidos estão presentes no vetor "in\_bits".

- Sinal "valid\_mon": Bit de indicação de leitura do barramento "in\_bits" controlado pelo Adaptador RTL, o qual mantém nível baixo durante operação normal e, após um aviso de dados prontos para leitura por parte do MONITOR, assume nível alto quando o vetor "in\_bits" tiver sido lido pelo Adaptador RTL.

No grupo de sinais de GLOBAIS tem-se:

- Sinal "rtl\_clk": Sinal de clock controlado pelo Adaptador RTL e que é utilizado para alimentar o dispositivo RTL do usuário, juntamente do DRIVER e do MONITOR. A frequência deste sinal de clock pode ser configurada através de uma escrita, por parte do processador NIOS, no Adaptador RTL.

- Sinal "reset": Sinal de reset controlado pelo Adaptador RTL que deve ser usado pelo RTL do usuário, juntamente do DRIVER e do MONITOR, para restaurar as condições iniciais do sistema.

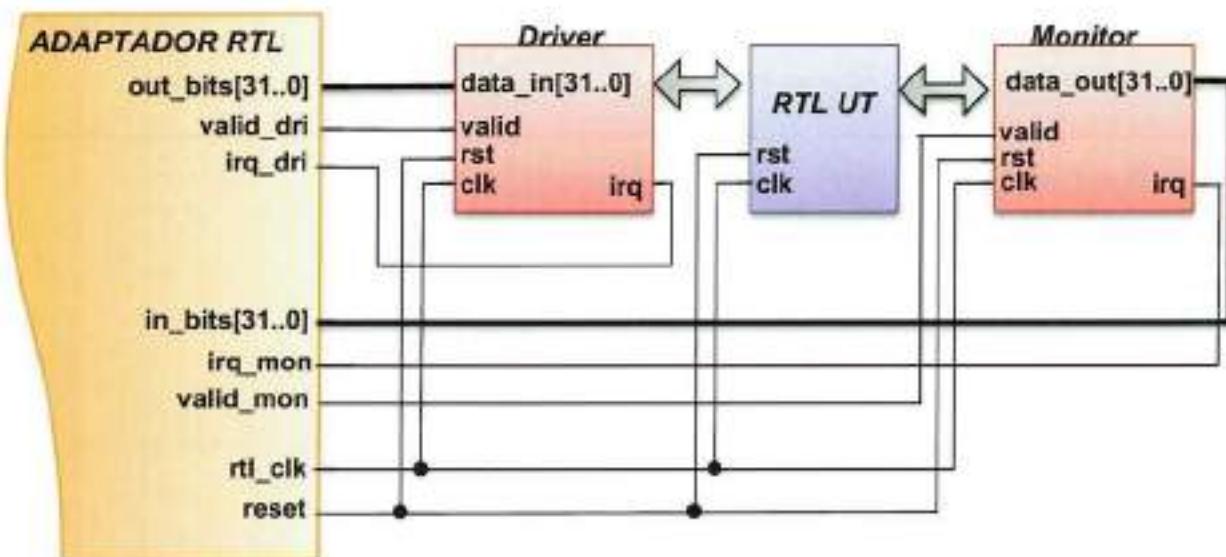

A versão corrente do Adaptador RTL usa vetores de dados "in\_bits" e "out\_bits" de 32 bits ( $M=N=31$ ) de comprimento. Isto facilitou o desenvolvimento de hardware pelo fato de que o barramento AVALON também utiliza palavras com 32 bits de comprimento. A figura 18 mostra em detalhes como o dispositivo RTL do usuário irá ser interligado ao sistema RTOOL.

Figura 18. Detalhamento da interligação entre o Adaptador RTL e o dispositivo RTL do usuário

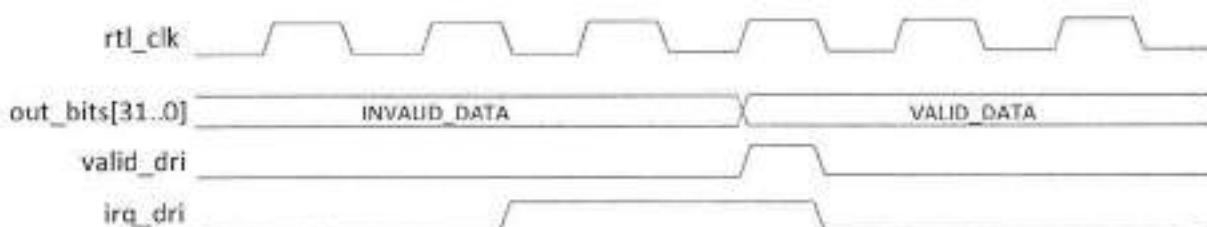

A seguir são apresentados exemplos de transação entre o DRIVER e o Adaptador RTL, e entre o MONITOR e o Adaptador RTL. Note que, como a comunicação entre estes dispositivos é assíncrona, pois eles pertencem a dois domínios de clocks distintos, o sinal de clock é irrelevante. Contudo, o sinal de clock foi apresentado nos diagramas por conveniência.

Exemplo de requisição de dados por parte do DRIVER:

Figura 19. Carta de tempos de uma requisição do DRIVER

Inicialmente a entrada "data\_in[31..0]" do driver, a qual corresponde à interface "out\_bits[31..0]" do Adaptador RTL, contém dados inválidos. Quando o DRIVER do dispositivo RTL estiver pronto para receber dados de entrada ele irá gerar uma interrupção colocando o sinal "irq\_dri" em nível lógico alto. O sistema RTOOL iniciará sua rotina de atualização do vetor "out\_bits[31..0]", e, após terminar, colocará o sinal "valid\_dri" em nível alto. Para finalizar a transação o DRIVER colocará o sinal "irq\_dri" em nível lógico baixo para indicar o recebimento de dados, e o Adaptador RTL colocará o sinal "valid\_dri" em nível baixo imediatamente em seguida.

Exemplo de aviso de dados válidos por parte do MONITOR:

Figura 20. Carta de tempos de uma requisição do MONITOR

Quando o MONITOR atualizar sua saída ("data\_out[31..0]") com novos dados válidos, ele deverá gerar uma interrupção para que o Adaptador RTL tenha conhecimento deste evento. Neste momento o Adaptador RTL irá iniciar sua rotina de leitura do vetor "in\_bits[31..0]" e, após terminar, colocará o sinal "valid\_mon" em nível alto. Para finalizar a transação o MONITOR colocará o sinal "irq\_mon" em nível lógico baixo, e o Adaptador RTL colocará o sinal "valid\_dri" em nível baixo imediatamente em seguida.

### 3.2.2 Software do SOPC

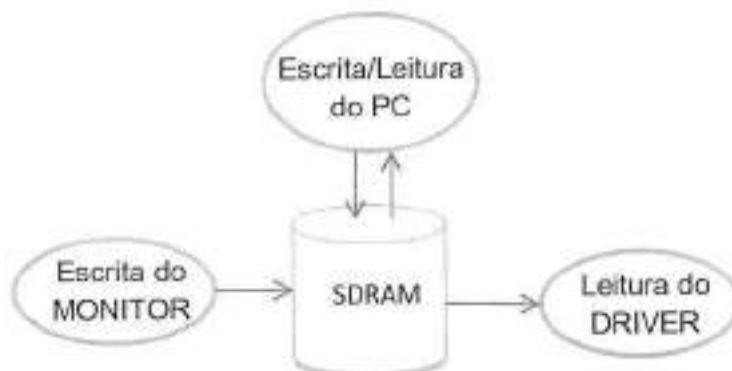

O software embarcado do processador NIOS II tem por objetivo gerenciar os diversos processos que ocorrem na placa. São eles: processo de leitura/escrita do PC, processo de leitura do DRIVER e processo de escrita do MONITOR.

Inicialmente, é fornecida uma descrição conceitual dos processos que foram implementados em software. Em seguida, a máquina de estados finitos desenvolvida em linguagem de programação C é apresentada e explicada.

O software desenvolvido para o processador NIOS II, na verdade, corresponde a um firmware, já que não foi usado nenhum sistema operacional.

#### 3.2.2.1 Descrição conceitual dos processos

O diagrama da figura 21 mostra de que forma cada processo usa a memória SDRAM. O processo "Escrita/Leitura do PC" escreve e lê, enquanto o processo "Escrita do MONITOR" apenas escreve e o processo "Leitura do DRIVER" apenas lê da memória.

Figura 21. Interações entre os processos e a memória SDRAM

A seguir cada processo é apresentado individualmente, e suas interdependências são explicitadas.

##### ➤ Escrita/Leitura do PC:

Trata-se do processo em que ocorre a transferência, entre o PC e o NIOS, de vetores de entrada/saída do dispositivo RTL do usuário.

Na operação de escrita do PC, os pacotes de dados são enviados pelo PC e recebidos pelo NIOS. Após serem recebidos pelo NIOS, os dados são armazenados na memória SDRAM, para posterior utilização pelo processo de leitura do DRIVER.

Na operação de leitura do PC, os pacotes de dados são requisitados pelo PC e, se houverem dados disponíveis na memória SDRAM, enviados pelo NIOS. A disponibilidade de dados na memória SDRAM é determinada pelo processo de escrita do MONITOR.

➤ **Leitura do DRIVER:**

É o processo em que os pacotes de dados enviados pelo PC, e que se encontram armazenados na memória, devem ser repassados ao DRIVER do dispositivo RTL.

A condição de início de uma transferência de dados entre o NIOS e o DRIVER é uma requisição de interrupção por parte do DRIVER. Isto fará com que pacotes de dados disponíveis na memória SDRAM sejam enviados ao DRIVER.

Cada pacote é composto por um conjunto de campos que representam os vetores de estímulo da entrada do DRIVER.

➤ **Escrita do MONITOR:**

Neste processo ocorre o inverso do processo de Leitura do DRIVER, ou seja, o recolhimento dos pacotes já processados pelo dispositivo RTL do usuário.

A condição de inicio desta transferência entre o MONITOR e o NIOS, novamente, é uma requisição de interrupção por parte do MONITOR. Esta requisição tem por objetivo informar que dados de saída estão prontos para serem coletados.

Os pacotes recolhidos são escritos na memória SDRAM para posterior transferência ao PC.

### 3.2.2.2 Máquina de Estados Finitos

A metodologia de desenvolvimento de software na forma de máquinas de estados finitos (MEF) é particularmente útil quando não há um sistema operacional na plataforma para a qual o software está sendo desenvolvido, pois permite atribuir um caráter multi tarefa à esta aplicação.

Em linguagem de programação C, o *framework* comumente adotado para a implementação de MEF é apresentado no código a seguir, no qual a declaração "switch" é adotada para se efetuar a multiplexação entre as rotinas de cada estado da máquina:

```

#define ESTADO_0 0

#define ESTADO_1 1

// variáveis de estado

```

```

unsigned int state, next_state = ESTADO_0;

while( 1 )

{

state = next_state; // atualiza estado

switch( state )

{

case ESTADO_0:

TarefaDoEstado0( &next_state );

break;

case ESTADO_1:

TarefaDoEstado1( &next_state );

break;

default:

TratamentoDeEstadoInvalido( &next_state );

break;

}

}

```

No framework fornecido, há apenas dois estados definidos, porém uma MEF com mais estados pode ser facilmente construída de forma análoga ao código em questão.

Verifique que cada estado da MEF executa sua rotina específica, a qual pode vir a alterar, ou não, a variável que determina o próximo estado, de acordo a verificação de uma condição de mudança de estado.

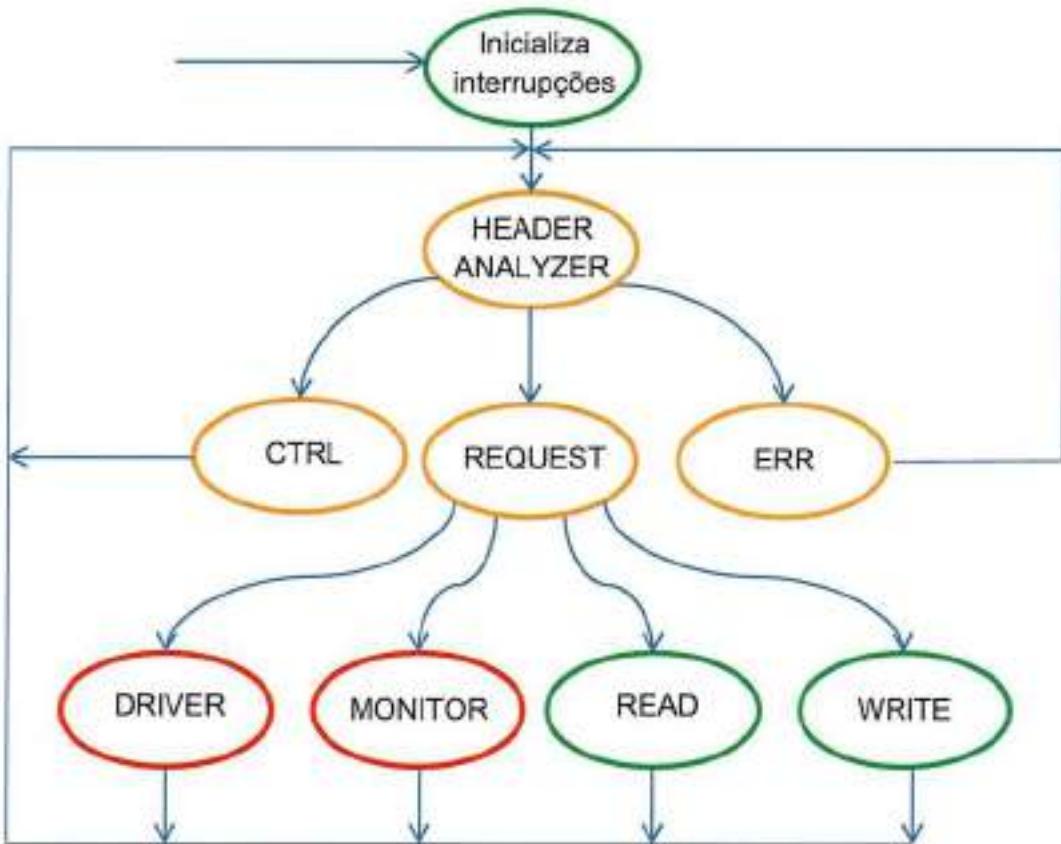

Referente ao software embarcado do RTOOL, o diagrama da MEF implementada é mostrado na figura 22.

Figura 22. Diagrama da MEF do software embarcado do sistema RTOOL

As diferentes cores dos estados são explicadas a seguir:

- Em verde tem-se os estados nos quais as interrupções do processador NIOS II foram desabilitadas.

- Em laranja tem-se os estados nos quais as interrupções do processador NIOS II estão ativas.

- Em vermelho tem-se os estados que podem ser diretamente acessados (fora do percurso normal da MEF) quando uma requisição de interrupção é enviada ao processador NIOS II.

Antes da execução do código entrar na MEF, as interrupções do processador NIOS II são habilitadas. Isto é necessário para que o DRIVER e o MONITOR do dispositivo RTL do usuário possam requisitar operações de escrita/leitura ao software embarcado.

Uma vez que as interrupções foram habilitadas, a MEF vai para seu estado inicial, o estado HEADER\_ANALYZER, cuja função principal é analisar os pacotes de dados recebidos pelo processador NIOS II, os quais foram enviados pelo PC. Depois de decodificar o tipo de pacote recebido (de acordo com o protocolo definido na seção

"3.2.4.3 – Protocolo de comunicação com a placa de prototipagem") o estado HEADER\_ANALYZER configura o próximo estado da MEF.

Caso o estado seguinte ao HEADER\_ANALYZER seja o estado CTRL, isto significa que uma operação de controle foi requisitada. São definidas como operações de controle o comando de *reset* do sistema RTOOL, a configuração da frequência do sinal de *clock* que alimenta o hardware do usuário e a configuração do tamanho, em bits, da palavra que será escrita/lida do Adaptador RTL (32 bits). Após a realização da operação de controle, a MEF volta à seu estado inicial.

Caso o estado seguinte ao HEADER\_ANALYZER seja o estado ERR, isto significa que uma mensagem de erro foi enviada pelo PC. Na versão corrente do sistema RTOOL, o único tipo de erro contemplado é o erro de "*time out*", ou seja, um erro que ocorre quando uma das partes da comunicação deixa de responder uma mensagem. O estado ERR tem o intuito de manter a sincronização entre o PC e o NIOS mesmo quando um erro de "*time out*" ocorre. Após a realização desta operação, a MEF volta à seu estado inicial.

Caso o estado seguinte ao HEADER\_ANALYZER seja o estado REQUEST, isto significa que uma requisição de escrita/leitura de vetor de dados de entrada/saída do hardware do usuário foi enviada pelo PC. As requisições podem ser de dois tipos, os quais são explicados a seguir:

- A requisição WRITE é enviada pelo PC quando o mesmo deseja disponibilizar mais vetores de dados entrada ao dispositivo RTL do usuário. Como tais vetores de dados serão guardados temporariamente na memória SDRAM da placa de prototipagem (até que sejam requisitados pelo DRIVER), se faz necessária uma verificação de disponibilidade de espaço na memória na região de vetores de entrada do dispositivo RTL do usuário. Caso haja espaço disponível, uma mensagem de requisição aceita será enviada ao PC e o próximo estado da MEF será o estado WRITE. Caso não haja espaço disponível, uma mensagem de requisição negada será enviada ao PC e o próximo estado da MEF será o estado DRIVER.

- A requisição READ é enviada ao pelo PC quando o mesmo desejar ler vetores de dados de saída gerados pelo dispositivo RTL do usuário. Logo após o recebimento desta requisição, o NIOS irá verificar se existem dados suficientes para serem lidos da região de memória de vetores de saída do dispositivo RTL do usuário. Caso haja dados disponíveis, uma mensagem de requisição aceita será enviada ao PC, e o próximo estado da MEF será o estado READ. Caso não haja dados disponíveis o suficiente, uma mensagem de requisição negada será enviada ao PC e o próximo estado da MEF será o estado MONITOR.

No estado WRITE o processador NIOS II simplesmente irá receber os vetores de dados do PC e irá armazená-los na região da memória SDRAM de vetores de entrada do dispositivo RTL. O próximo estado será o estado inicial da MEF.

No estado READ o processador NIOS II simplesmente irá ler vetores de dados da memória SDRAM na região de vetores de saída do dispositivo RTL, e em seguida irá enviá-los ao PC. O próximo estado será o estado inicial da MEF.

O estado DRIVER pode ser atingido de duas formas, proveniente da execução prévia do estado REQUEST ou através de uma interrupção gerada pelo DRIVER do dispositivo RTL do usuário:

- Quando o estado DRIVER é atingido por uma interrupção, o processador NIOS II irá verificar se existem vetores de entrada disponíveis na memória SDRAM e, se houver, irá enviá-los ao DRIVER do RTL do usuário. Caso contrário, uma *flag* de sinalização de **falta de vetores de entrada** será "setada". Ao final da rotina de interrupção a MEF retorna ao estado que estava sendo executado antes da interrupção.

- Se o estado DRIVER foi atingido proveniente da execução prévia do estado REQUEST, isto significa que a região de memória de vetores de entrada está cheia. Neste caso o processador irá verificar se a *flag* de **falta de vetores de entrada** está com nível lógico alto, e, se estiver, irá transferir vetores de entrada da memória SDRAM ao DRIVER do RTL do usuário com o intuito de gerar espaço disponível na memória. Em seguida a MEF retornará à seu estado inicial.

O estado MONITOR, também, pode ser atingido de duas formas, proveniente da execução prévia do estado REQUEST ou através de uma interrupção gerada pelo MONITOR do dispositivo RTL do usuário.

- Quando o estado MONITOR é atingido por uma interrupção, o processador NIOS II irá verificar se existe espaço disponível na região da memória SDRAM de vetores de saída e, se houver, irá transferir o vetor de saída recém gerado do MONITOR à memória. Caso contrário, uma *flag* de sinalização de **vetor de saída pendente** será "setada". Ao final da rotina de interrupção a MEF retorna ao estado que estava sendo executado antes da interrupção.

- Se o estado MONITOR foi atingido proveniente da execução prévia do estado REQUEST, isto significa que a região de memória de vetores de saída está vazia. Neste caso o processador irá verificar se a *flag* de **vetor de saída**

**pendente** está com nível lógico alto, e, se estiver, irá transferir vetores de saída do MONITOR do RTL do usuário à região correspondente da memória SDRAM com o intuito de aumentar a disponibilidade de dados para uma futura requisição de leitura por parte do PC. Em seguida a MEF retornará à seu estado inicial.

### 3.2.3 Ferramenta de prototipagem rápida

Tendo por objetivo facilitar o uso do sistema RTOOL, uma ferramenta de prototipagem rápida com interface gráfica de usuário (GUI) foi desenvolvida. Este capítulo descreve os processos que tal ferramenta torna automáticos, e mostra o design da GUI criada.

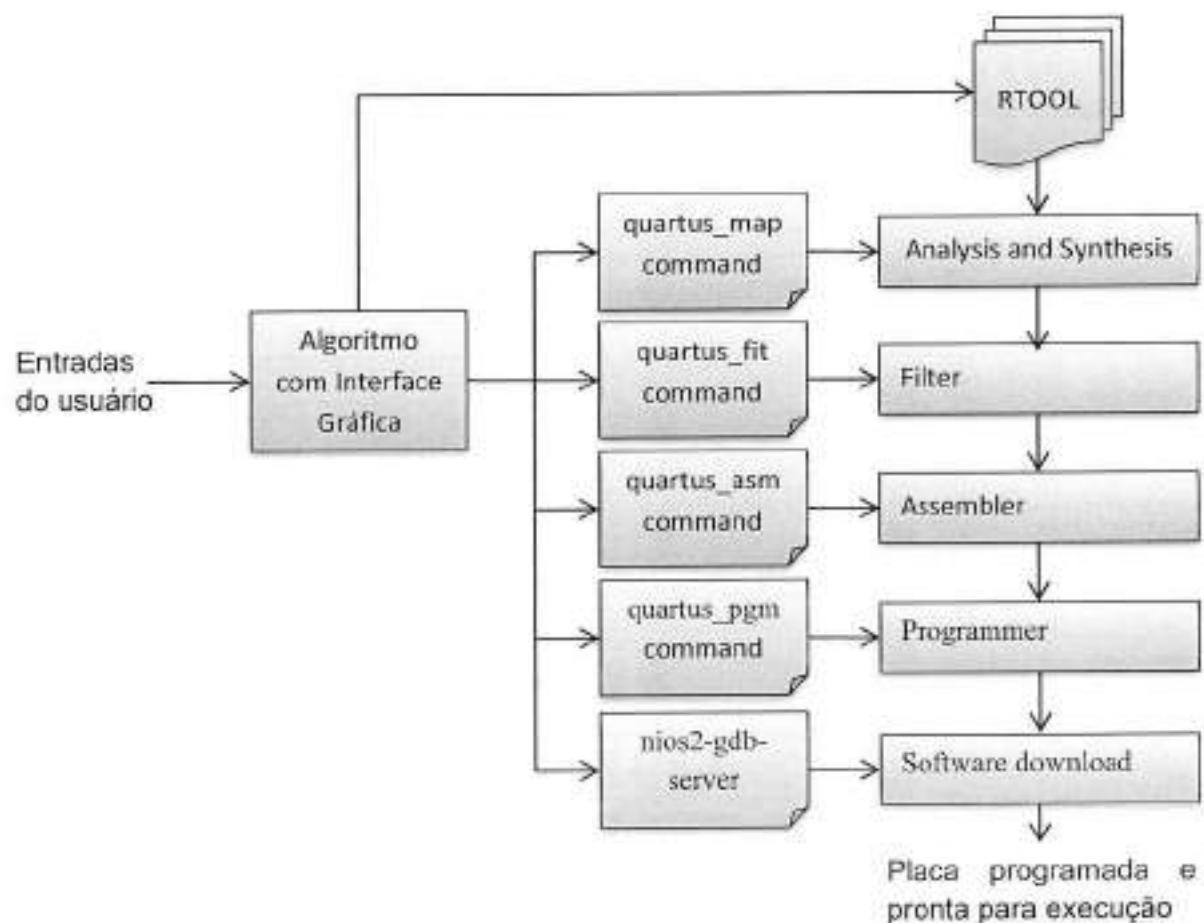

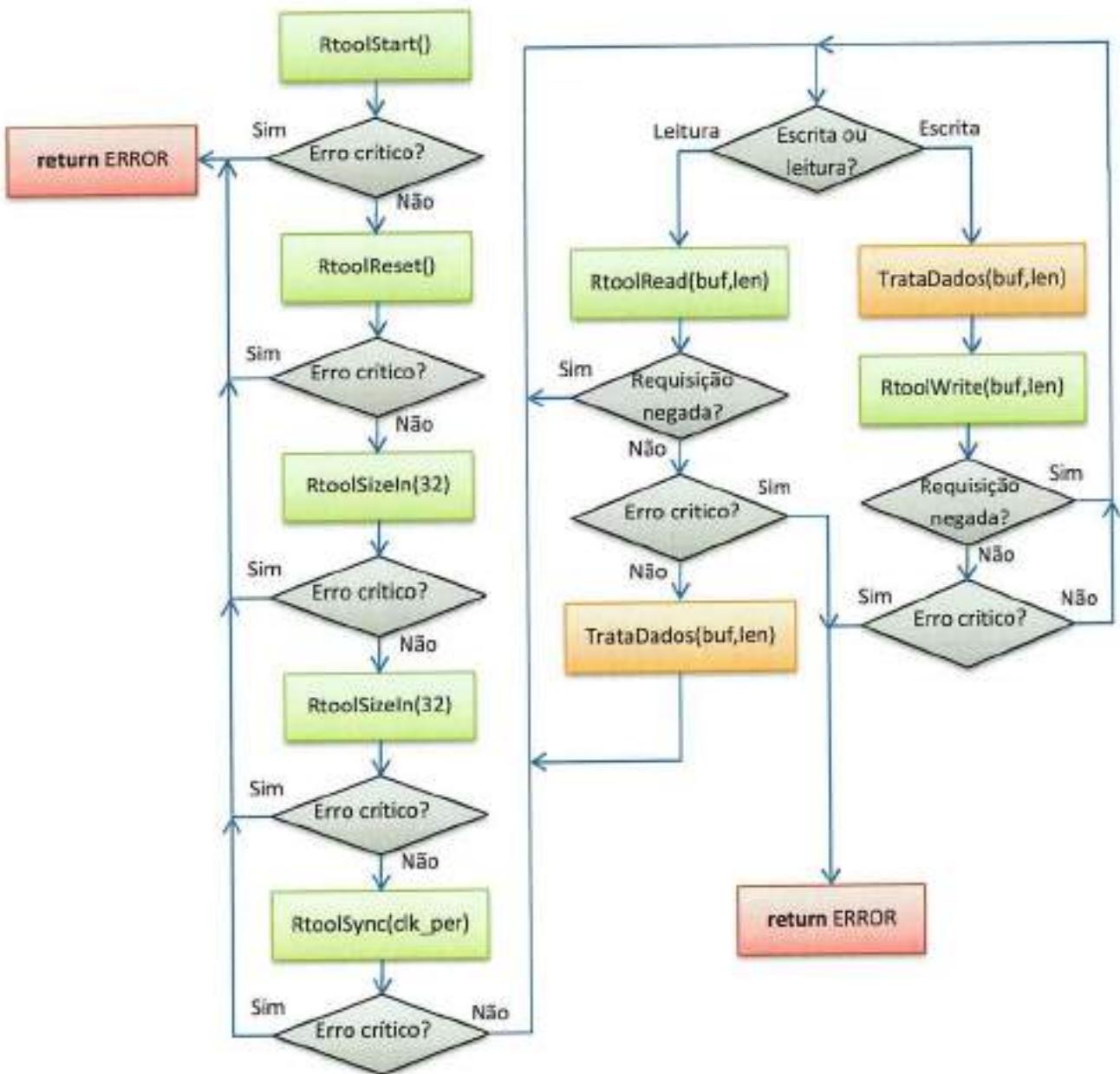

#### 3.2.3.1 Algoritmo de integração, compilação e programação

As etapas de integração do dispositivo RTL do usuário ao SOPC do RTOOL, de compilação do hardware resultante e de programação da placa de prototipagem com o hardware sintetizado e com o software embarcado são tarefas que poderiam realizadas manualmente. Todavia, dado que estas três tarefas são bastante simples e repetitivas, optou-se por implementar neste projeto um algoritmo que permite a realização destas etapas de forma automatizada.